- •В схеми «і» «або» на діодно резистивних ланках

- •2. Транзисторний ключ з спільнимемітером

- •Двокаскадна др. Логіка

- •4) Підвищення швидкодії транзисторна ключа за рахунок збільшення струму бази при включенні і зміни її напрямку на зворотній при виключені

- •5)Схема з трьома станами

- •6)Транзисторний ключ з нелінійним зворотним зв’язком

- •7) Схемы транзисторных ключей

- •11) Основна базова схема інжекційно інтегральної логіки

- •12) Ключ на мдп транзисторі. З мдп транзистором замість р(рез) стокового

- •15) Основна базова схема другого типу на мдп транзисторах

- •2. Його позитиви: простота.

- •3. Його недоліки: заборонені стани.

- •17) Реалізація рс тригера на елементах або нє

- •18 Реалізаціярстригера на елементах і нє

- •19. Т тригер(нічийний )

- •20) Д тригер

- •22. Двотактний регістр

- •25. Зсув інформації в регістрах в ліво

- •26. Зсув інформації в регістрах в право

- •27. Зсув інформації в регістрах Вліво вправо.

- •29) Лічильник з наскрізним переносом

- •31) За способом організації переносу (позички) між розрядами лічильники поділяють на такі типи:

- •32. Двійково-десяткові лічильники

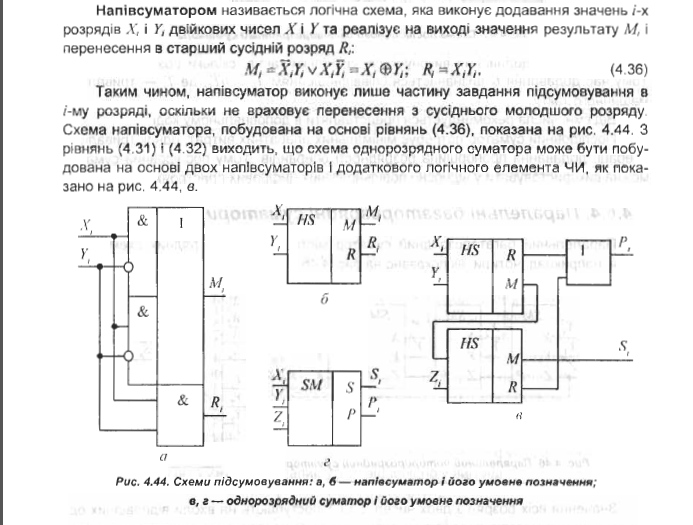

- •33) Двохходовий одно розрядний суматор комбінаційного типу напівсуматор

- •34) Трьохходовий одно розрядний суматор комбінаційного типу повний суматор

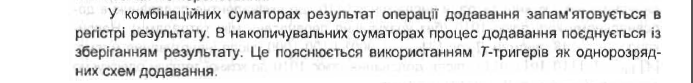

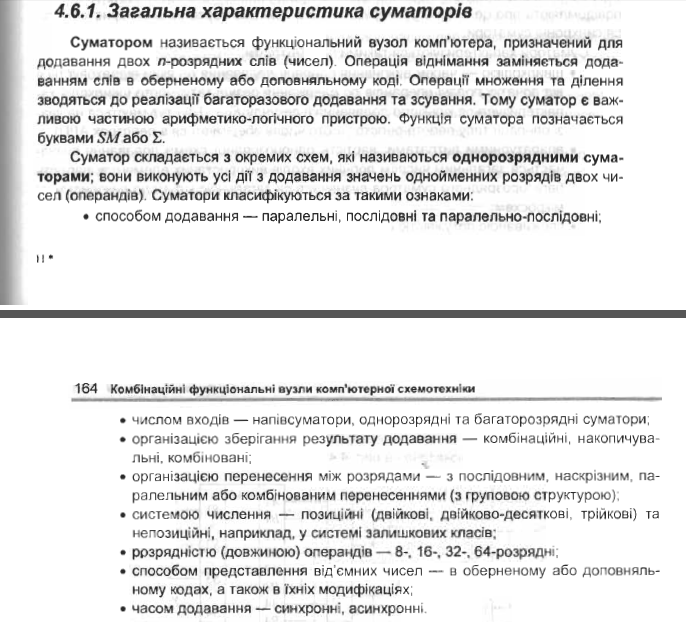

- •35. Однорозрядні суматори накопичуючого типу

- •36. Послідовний багаторозрядний суматор

- •37. Багато розрядний суматор паралельної дії

- •38. Прямокутний дешифратор

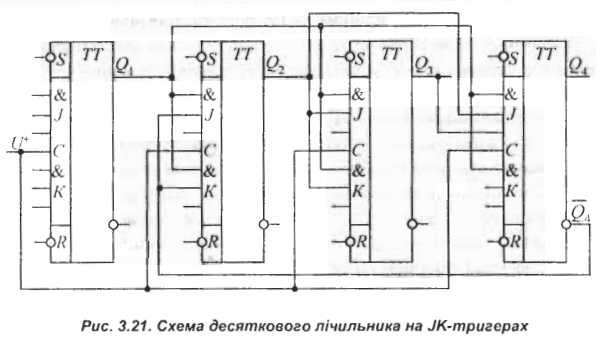

32. Двійково-десяткові лічильники

Двійково-десяткові лічильники реалізують лічбу імпульсів у десятковій системічислення, причому кожна десяткова цифра від нуля до дев'яти кодується чотирироз-рядним двійковим кодом (тетрадою). Ці лічильники часто називають десятковимиабо декадними, оскільки вони працюють з модулем лічби, кратним десяти.

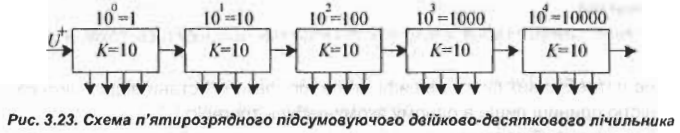

Багаторозрядний двійково-десятковий лічильник будується на основі регулярного ланцюга декад, при цьому перша (молодша) декада має вагу 10°, друга — 101,третя — 102 і т.д.

Декада будується на основі чотирирозрядного двійкового лічильника, в якомувилучається надлишкове число станів. Вилучення зайвих шести станів у декаді досягається багатьма способами:

попереднім записуванням числа б (двійковий код 011-0); після лічбидев'ятого імпульсу вихідний код дорівнює І ІІІ і десятковий сигнал повертаєлічильник у початковий стан 0110, отже, тут результат лічби фіксуєтьсядвійковим кодом з надлишком 6;

блокуванням переносів: лічба імпульсів до дев'яти здійснюється у двійковому коді, після чого вмикаються логічні зв'язки блокування перенесень, з надходженням десятого імпульсу лічильник закінчує цикл роботи і повертається□ початковий нульовий стан;

введенням обернених зв'язків, які забезпечують лічбу в двійковому коді йпримусовим перемиканням лічильника в нульовий початковий стан післянадходження десятого імпульсу.

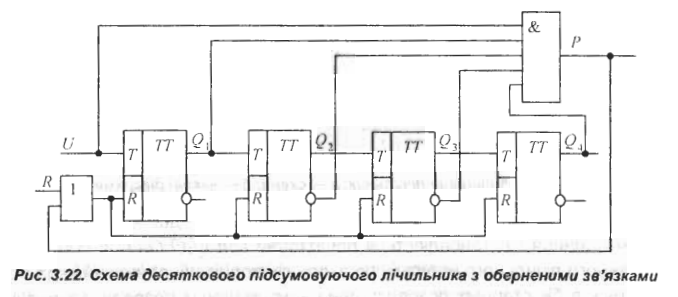

Схема синхронного десяткового лічильника з блокуванням перенесень показанана рис. 3.21. У цій схемі С-входи використовуються як лічильні. З надходженням десятого імпульсу на С-вхід молодшого розряду Ж-тригера обнуляються перший і четвертий розряди і сигналом з виходу Q\ блокують перемикання другого і третьогорозряду. Схема підсумовуючого лічильника з оберненими зв'язками (один розряд)показана на рис. 3.22.

Після скидання в нульовий початковий стан на лічильний вхід першого тригерапоступають підсумовуючі імпульси U. Сигнали перенесення в старші розряди формуються звичайним асинхронним способом. Лічба до дев'яти ведеться в двійковомукоді. Після приходу десятого вхідного імпульсу обернений зв'язок на основі схемизбігу виробляє сигнал Р - £/" 0^0?0г0{, який є переносом для старшої декади і одночасно перемикає лічильник в нульовий стан. Далі цикл роботи лічильника повторюється.

Виходи тригерів кожної декади підключаються до входів дешифраторів, які забезпечують візуальну індикацію стану лічильника за допомогою різного роду світлових табло

33) Двохходовий одно розрядний суматор комбінаційного типу напівсуматор

пу

напівсуматор

пу

напівсуматор

34) Трьохходовий одно розрядний суматор комбінаційного типу повний суматор

35. Однорозрядні суматори накопичуючого типу

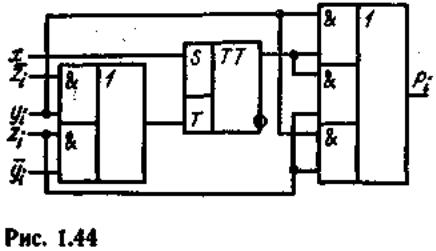

Накопичуючіоднорозрядні суматори. Накопичуючимоднорозрядним суматором називають схему з пам'яттю, що здійснює арифметичне додавання цифр що складаються xi, yi і переносу zi при подачі їхній на суматор послідовно в часі, незалежно від того, яким кодом (послідовним чи паралельної) представлені слова, що складаються, X і Y, а також запам'ятовуючий результат додавання. Такі суматоры будують на основі тригерів T-типу. Одна зі схем однорозрядногонакопичуючого суматора представлена на рис.1.43. Тут на тригері 1 спочатку формується сума q=x*y , а потім s=q*z.

Перенос при додаванні xi і уi формується елементом 4 і запам'ятовується тригером 2 до подачі зовнішнього сигналу дозволу переносу (РП), синхронного із сигналом zi (відмінність між zi і РП у тім, що, коли РП = 1, zi може бути дорівнює і 0, і 1). Перенос при додаванні qi і zi формується елементом 7. Час додавання на такому суматорі дорівнює трьом тактам. Вхід xi може бути відсутнім. При цьому цифри доданків надходять послідовно на вхід уi У комбінаційно-накопичуючому суматорі (рис.1.44) сигнал переносу pi формується по МДНФ цієї функції, а сума si — на тригері T-типу. На вхід цього тригера подають сигнал, дорівнює сумі по mod 2 yi і zi і формований комбінаційною схемою. Час додавання тут складає два такти.