- •В схеми «і» «або» на діодно резистивних ланках

- •2. Транзисторний ключ з спільнимемітером

- •Двокаскадна др. Логіка

- •4) Підвищення швидкодії транзисторна ключа за рахунок збільшення струму бази при включенні і зміни її напрямку на зворотній при виключені

- •5)Схема з трьома станами

- •6)Транзисторний ключ з нелінійним зворотним зв’язком

- •7) Схемы транзисторных ключей

- •11) Основна базова схема інжекційно інтегральної логіки

- •12) Ключ на мдп транзисторі. З мдп транзистором замість р(рез) стокового

- •15) Основна базова схема другого типу на мдп транзисторах

- •2. Його позитиви: простота.

- •3. Його недоліки: заборонені стани.

- •17) Реалізація рс тригера на елементах або нє

- •18 Реалізаціярстригера на елементах і нє

- •19. Т тригер(нічийний )

- •20) Д тригер

- •22. Двотактний регістр

- •25. Зсув інформації в регістрах в ліво

- •26. Зсув інформації в регістрах в право

- •27. Зсув інформації в регістрах Вліво вправо.

- •29) Лічильник з наскрізним переносом

- •31) За способом організації переносу (позички) між розрядами лічильники поділяють на такі типи:

- •32. Двійково-десяткові лічильники

- •33) Двохходовий одно розрядний суматор комбінаційного типу напівсуматор

- •34) Трьохходовий одно розрядний суматор комбінаційного типу повний суматор

- •35. Однорозрядні суматори накопичуючого типу

- •36. Послідовний багаторозрядний суматор

- •37. Багато розрядний суматор паралельної дії

- •38. Прямокутний дешифратор

26. Зсув інформації в регістрах в право

М ікросхема ИР1 – це універсальний 4-розрядний регістр зсуву, який дозволяє здійснювати послідовний і паралельний запис інформації в тригери регістра, послідовне і паралельне зчитування інформації та зсув інформації. Він має послідовний вхід даних SI, чотири паралельних входи D0..D3, а також чотири виходи Q0..Q3 від кожного з тригерів. Регістр має також два тактових входи C1 і C2. Інформація на виходи від будь-якого з п’яти входів даних надійде синхронно з від’ємним перепадом, поданим на вибраний тактовий вхід.

Вхід дозволу паралельного завантаження EL використовується для вибору режиму роботи регістра. Якщо на вхід EL подається лог.1, дозволяється робота по тактовому входу C2. В момент приходу на цей вхід від’ємного перепаду тактового імпульса в регістр завантажуються дані від паралельних входів D0..D3.

Якщо на вхід EL подано лог.0, дозволяється робота по тактовому входу C1. Від’ємні фронти послідовності тактових імпульсів зсувають дані від послідовного входу SI на вихід Q0, потім на Q1, Q2 і Q3, тобто вправо

З сув

вправо (1000010000100001)

сув

вправо (1000010000100001)

Зсув вліво (0001001001001000)

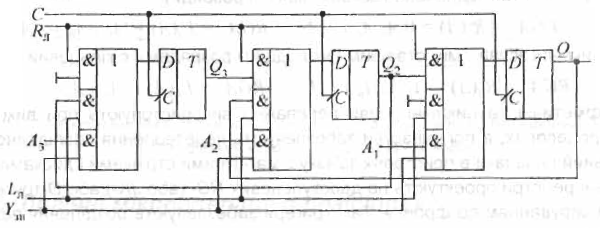

27. Зсув інформації в регістрах Вліво вправо.

Зсув-це одночасне просторове переміщення двійкового слова в розрядній сітці із збереженням порядку слідування нулів і одиниць. Регістри, які призначенні для виконання мікрооперацій зсуву називаються регістрами зсуву або зсувовими.

Оскільки у нас іде зсув Вліво а потім вправо, то мова буде іти про реверсивні регістри. Вони працюють таким чином. При значенні сигналу Yзп=1 (В) в регістр записується інформація паралельним однофазним кодом. При значенні сигналу Rл =0 інформація, що зберігається одночасно зсувається в у бік старших розрядів (вліво), при цьому розряд Q1обнулюється. При значенні сигналу Lа = 0 інформація в регістрі одночасно зсувається у бік старших розрядів (вправо), при цьому розряді Q3обнуляється. Запис і зсув інформації відбувається по фронту синхроімпульсу.

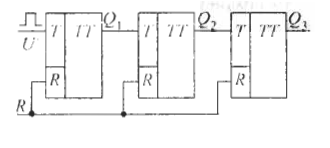

28. Простий каскадний лічильник(Лічильники з послідовним переносом)

За способом організації міжрозрядних зв'язків лічильники діляться на лічильники з послідовним переносом, вони ще носять назву каскадні,лічильники з паралельним переносом і лічильники з паралельно-послідовним переносом. Найпростіші і разом з тим самі повільні – це лічильники з послідовним переносом. Прості лічильники можуть вести рахунок тільки в одному напрямку, тобто тільки

додавати вхідні сигнали до коду (лічильники додавання), сформованому на лічильнику, або тільки віднімати вхідні сигнали з цього коду (лічильник віднімання).

*Асинхронний тригер можу бути створений на лічильному тригері будь якого типу. В більшості випадків використовують D - та JK - тригери,використовуючи, їх в лічильному режимі. Для приведення лічильника в початковий стан використовується сигнал скидання R, що надходить одночасно на всі входи R тригерів.Найпростіший лічильник на D-Тригерах складається із з'єднаних послідовно рахункових тригерів, таким чином, що вихід Qk кожного тригера з'єднаний із входом Qk+1 наступного(рис. 4.1). При надходженні рахункових імпульсів на вхід СLK тригери лічильника будуть змінювати свої стани, описувані послідовно зростаючими двійковими числами.

*Для побудови синхронних лічильників використовують різні типи лічильних синхронних тригерів. Ці схеми реалізуються на синхронних рахункових тригерах і логічних елементах «І» для формування сигналів переносу Р або позики Z.