- •В схеми «і» «або» на діодно резистивних ланках

- •2. Транзисторний ключ з спільнимемітером

- •Двокаскадна др. Логіка

- •4) Підвищення швидкодії транзисторна ключа за рахунок збільшення струму бази при включенні і зміни її напрямку на зворотній при виключені

- •5)Схема з трьома станами

- •6)Транзисторний ключ з нелінійним зворотним зв’язком

- •7) Схемы транзисторных ключей

- •11) Основна базова схема інжекційно інтегральної логіки

- •12) Ключ на мдп транзисторі. З мдп транзистором замість р(рез) стокового

- •15) Основна базова схема другого типу на мдп транзисторах

- •2. Його позитиви: простота.

- •3. Його недоліки: заборонені стани.

- •17) Реалізація рс тригера на елементах або нє

- •18 Реалізаціярстригера на елементах і нє

- •19. Т тригер(нічийний )

- •20) Д тригер

- •22. Двотактний регістр

- •25. Зсув інформації в регістрах в ліво

- •26. Зсув інформації в регістрах в право

- •27. Зсув інформації в регістрах Вліво вправо.

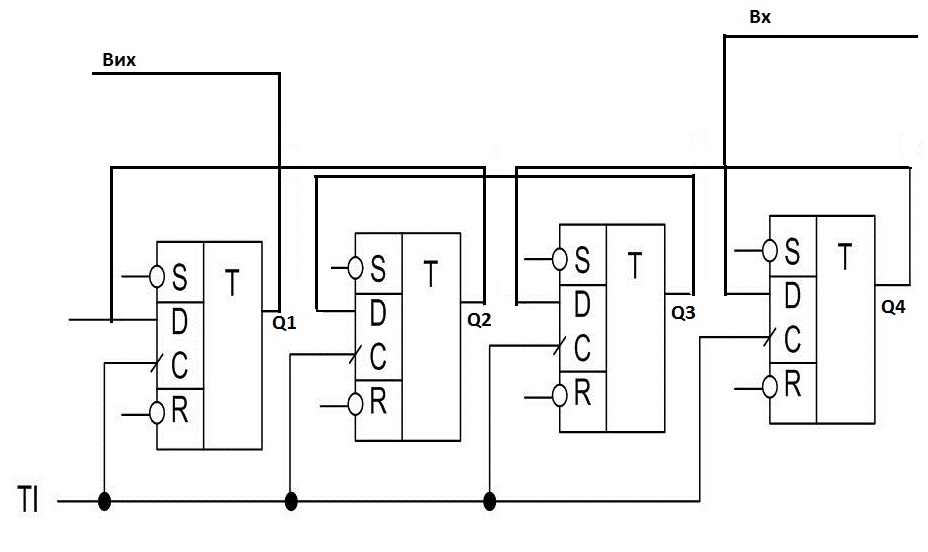

- •29) Лічильник з наскрізним переносом

- •31) За способом організації переносу (позички) між розрядами лічильники поділяють на такі типи:

- •32. Двійково-десяткові лічильники

- •33) Двохходовий одно розрядний суматор комбінаційного типу напівсуматор

- •34) Трьохходовий одно розрядний суматор комбінаційного типу повний суматор

- •35. Однорозрядні суматори накопичуючого типу

- •36. Послідовний багаторозрядний суматор

- •37. Багато розрядний суматор паралельної дії

- •38. Прямокутний дешифратор

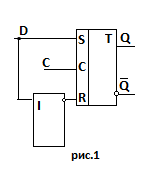

20) Д тригер

Три́гер— електронна логічна схема, яка має два стійкі стани, в яких може перебувати доки не зміняться відповідним чином сигнали керування. Напруги і струми на виході тригера можуть змінюватися стрибкоподібно.

За способом організації логічних зв’язків розрізняють тригери з запуском (RS-тригери); з лічильним входом (Т-тригери); тригери затримки (D-тригери); універсальні (JK-тригери); комбіновані (наприклад, RST-, JKRS-, DRS-тригери).

Тригером типу D називається синхронний запам’ятовуючий елемент з двома стійкими станами і одним інформаційним D-входом. Закон функціонування D-тригера описується логічним рівнянням:

Qt+1 = CtDt .

Це рівняння показує, що після перемикання стан D-тригера повторює значення сигналцу на D-вході в тактові моменти часу.

Схему

D-тригера можна побудувати на основі

синхронного RS-тригера, якщо сигнал по

входу S одночасно подавати через інвертор

на вхід

R

(рис. 1). Схеми D-тригера будуть також на

основі самостійного логічного рівняння.

Перетворимо рівняння

![]() замінивши сигнал S на

D i

сигнал R

на

замінивши сигнал S на

D i

сигнал R

на

![]() :

:

\1\

\1\

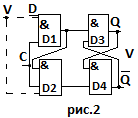

Схема D-тригера на елементах НЕ І з логічними зв'язками згідно з рівнянням \1\ показана на рис.2

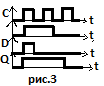

Тут D- тригер : 1- на основі RS-тригера, 2- на елементах НЕ І, 3- часові діаграми роботи

D-тригер слідкує за зміною сигналу на D-вході під час дії синхросигналу С і зберігає ту інформацію, яка була в момент його закінчення. RS-тригери такої властивості не мають, тому вони менше завадостійкі порівняно з D-тригерами.

Для затримки інформації в D-тригері на довільне число тактів використовується дозволяючий V-вхід, як показано штрихованою лінією на рис.2. Якщо V=1, то DV-тригер функціонує як звичайний тригер затримки; якщо V=0, то робота схеми за входами блокується і DV-тригер зберігає попередню інформацію.

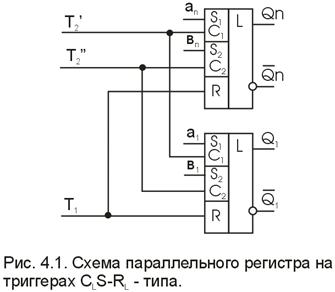

22. Двотактний регістр

Однофазні

паралельні регістри двотактного

дії

Найбільш

економічними по числу компонентів є

однофазні регістри двотактного дії, як

розрядів яких використовуються тригери ![]() -

Типів (двотактні D-тригери на рис.1).

На

рис.1 наводиться схема паралельного

регістра двотактного дії з однофазної

записом інформації для режиму запису

двох чисел A і B (регістр на два входи).

Входи

-

Типів (двотактні D-тригери на рис.1).

На

рис.1 наводиться схема паралельного

регістра двотактного дії з однофазної

записом інформації для режиму запису

двох чисел A і B (регістр на два входи).

Входи![]() відповідають входам

розрядів першого числа, а входи

відповідають входам

розрядів першого числа, а входи ![]() -

Входів розрядів другого числа.

-

Входів розрядів другого числа.

|

25. Зсув інформації в регістрах в ліво

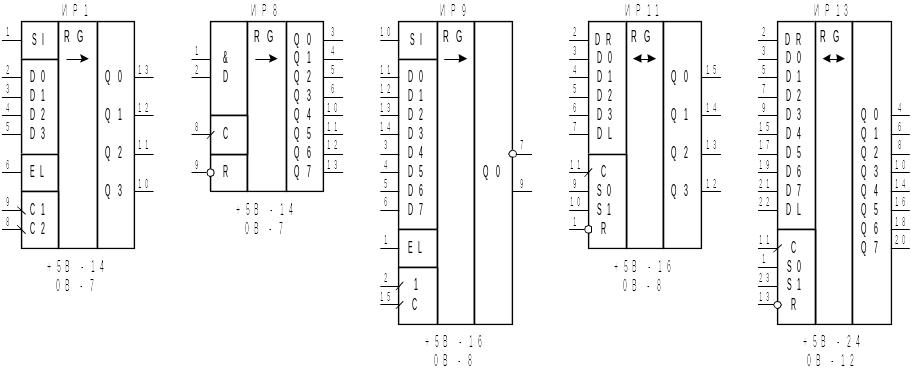

М ікросхема

ИР1 – це

універсальний 4-розрядний регістр зсуву,

який дозволяє здійснювати послідовний

і паралельний запис інформації в тригери

регістра, послідовне і паралельне

зчитування інформації та зсув інформації.

Він має послідовний вхід даних SI,

чотири паралельних входи D0..D3,

а також чотири виходи Q0..Q3

від кожного з тригерів. Регістр має

також два тактових входи C1

і C2.

Інформація на виходи від будь-якого з

п’яти входів даних надійде синхронно

з від’ємним перепадом, поданим на

вибраний тактовий вхід.

ікросхема

ИР1 – це

універсальний 4-розрядний регістр зсуву,

який дозволяє здійснювати послідовний

і паралельний запис інформації в тригери

регістра, послідовне і паралельне

зчитування інформації та зсув інформації.

Він має послідовний вхід даних SI,

чотири паралельних входи D0..D3,

а також чотири виходи Q0..Q3

від кожного з тригерів. Регістр має

також два тактових входи C1

і C2.

Інформація на виходи від будь-якого з

п’яти входів даних надійде синхронно

з від’ємним перепадом, поданим на

вибраний тактовий вхід.

Вхід дозволу паралельного завантаження EL використовується для вибору режиму роботи регістра. Якщо на вхід EL подається лог.1, дозволяється робота по тактовому входу C2. В момент приходу на цей вхід від’ємного перепаду тактового імпульса в регістр завантажуються дані від паралельних входів D0..D3.

Зсув даних по регістру вліво можна здійснити, якщо з’єднати вихід Q3 і вхід D2, Q2 і D1, Q1 і D0. При цьому регістр потрібно перевести в паралельний режим, подавши на вхід EL лог.1. Напругу на вході EL можна змінювати, тільки якщо на обох тактових входах лог.0. Однак, якщо на вході C1 лог.1, зміна сигнала на вході EL від 0 до 1 не змінює станів виходів.