- •В схеми «і» «або» на діодно резистивних ланках

- •2. Транзисторний ключ з спільнимемітером

- •Двокаскадна др. Логіка

- •4) Підвищення швидкодії транзисторна ключа за рахунок збільшення струму бази при включенні і зміни її напрямку на зворотній при виключені

- •5)Схема з трьома станами

- •6)Транзисторний ключ з нелінійним зворотним зв’язком

- •7) Схемы транзисторных ключей

- •11) Основна базова схема інжекційно інтегральної логіки

- •12) Ключ на мдп транзисторі. З мдп транзистором замість р(рез) стокового

- •15) Основна базова схема другого типу на мдп транзисторах

- •2. Його позитиви: простота.

- •3. Його недоліки: заборонені стани.

- •17) Реалізація рс тригера на елементах або нє

- •18 Реалізаціярстригера на елементах і нє

- •19. Т тригер(нічийний )

- •20) Д тригер

- •22. Двотактний регістр

- •25. Зсув інформації в регістрах в ліво

- •26. Зсув інформації в регістрах в право

- •27. Зсув інформації в регістрах Вліво вправо.

- •29) Лічильник з наскрізним переносом

- •31) За способом організації переносу (позички) між розрядами лічильники поділяють на такі типи:

- •32. Двійково-десяткові лічильники

- •33) Двохходовий одно розрядний суматор комбінаційного типу напівсуматор

- •34) Трьохходовий одно розрядний суматор комбінаційного типу повний суматор

- •35. Однорозрядні суматори накопичуючого типу

- •36. Послідовний багаторозрядний суматор

- •37. Багато розрядний суматор паралельної дії

- •38. Прямокутний дешифратор

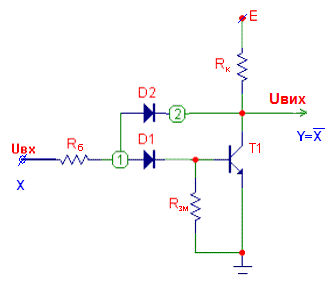

6)Транзисторний ключ з нелінійним зворотним зв’язком

Для підвищення швидкодії у цифрових пристроях часто застосовується нелінійний колекторно-базовий від’ємний зворотний зв’язок.

U1 = UБЕ + UD1 пряме

U2 = U1 − UD2 пряме

Рис. 23. Транзисторний ключ з нелінійним зворотним зв’язком

Призначення елементів:

RБ – обмежує струм у колі бази транзистора;

RК – обмежує струм у колекторному колі транзистора;

RЗМ – резистор зміщення, забезпечує надійне вимикання транзистора при подачі на вхід низького рівня;

D1 – забезпечує гальванічну розв’язку в колі бази;

D2 – забезпечує нелінійний зворотний зв’язок.

Діод зворотного зв’язку D2 перебуває під напругою U1-U2. До моменту, поки напруга в точці 2 перевищує напругу в точці 1, діод закритий. При подачі на вхід високого рівня, струм проходить через резистор RБ та діод D1 на базу транзистора T1. Під час відкриття транзистора напруга в точці 2 зменшується. Коли напруга в точці 2 стає менша за напругу в точці 1, діод D2 включається у прямому напрямку (відкривається). Включення діода замикає вузли 1 та 2 через малий опір відкритого діода D2. Наявність нелінійного зворотного зв’язку (НЗЗ) знижує коефіцієнт підсилення струму каскаду так, що подальше збільшення вхідного струму IRб мало впливає на підвищення струму на колекторі. На колекторі зберігається позитивна напруга і транзистор T1 не заходить у режим насичення.

При наявності НЗЗ транзистор не може зайти в режим насичення. НЗЗ модернізує схему транзисторного ключа. Як тільки напруга відкриває діод, струм розділяється і йде як на колектор, так і на емітер. Якщо D1 та D2 однакові, то UKЕ=UБЕ (теоретична границя насичення).

При подачі замикаючого сигналу спочатку відключається діод D2, а потім змінюється колекторна напруга. При закритому транзисторі нелінійний зворотний зв’язок розірваний. Так як при використанні НЗЗ у базі транзистора не відбувається надлишкове накопичення зарядів, то при закритті транзистора спостерігається мінімальний струм розсмоктування, що забезпечує швидке закриття транзистора.

7) Схемы транзисторных ключей

В цифровых устройствах применяются все виды и типы транзисторных ключей. В настоящее время, используется только npn транзисторы. В комбинированных и аналоговых схемах используются элементы pnp транзисторах. Npn имеют большее быстродействие в сравнении с pnp, объясняется подвижностью носителей заряда. Общая цепь должна иметь минимальную индуктивность. Rб — сопротивление цепи базы.

С общим коллектором

ki>1, ku < 1. Обратная связь по напряжению. Аналогия — эмиттерный повторитель. В нем действует 100% отрицательная последовательная обратная связь по напряжению. Поэтому каскады не обладают формирующими свойствами (сигнал затухает при последовательной передаче через несколько каскадов). У этого каскада очень маленькое выходное сопротивление. Используется как буферный. Используется при работе на низкоомную нагрузку и нагрузку с большой паразитной емкостью и индуктивностью, т.е. линии электрических интерфейсов. Rk — сопротивление, включенное в цепь коллектора. Rб — сопротивление в цепи базы. Rг — внутренне сопротивление источника сигнала. Ег — эдс генератора сигнала.

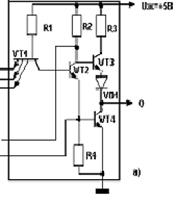

8) Основна базова схема ттл

В Інтегральній техніці знайшли застосування декілька типів основних логічних схем, які відрізняються елементами, що реалізують логічну операцію "1" чи "АБО", а також методом зв'язку між схемами в послідовних колах. Найбільшого поширення при виготовленні елементів малої і середньої степені інтеграції набула транзисторно-транзисторна логіка (ТТЛ). Елементи ТТЛ характерні тим. що з для зменшення впливу ємнісного навантаження (тобто з для підвищення швидкодії) вхідне коло таких елементів виконується на основі багатоемітерного транзистора по схемі з спільною базою, який має низький вхідний опір. В таких схемах необхідно, щоб коло, яке є генератором для багатоемітерного транзистора, при відключенні останнього було низькоомним і забезпечувало б швидке розсмоктування неосновних носіїв, накопичених в базі багатоемітерного транзистора. Для цього вихідний каскад попереднього однотипного елементу повинен бути достатньо потужним і низькоомним. Схема типового базового елемента ТТЛ представлена на рис 2. Даний елемент реалізує функцію "І-НІ в додатній логіці і функцію "АБО-НІ у від'ємній логіці, причому на транзисторах VТ2–VТ4 реалізовано складний інвентор, який здійснює операцію "НІ". Таке схемне рішення дозволило забеспечити високу навантажувальну здатність, достатню швидкодію і завадостійкість схеми, оскільки струм в закритому стані схеми створюється малим вихідним опором емітерного повторювача, зібраного на транзисторі VТЗ. а у відкритому стані струм, що поступає в схему, забезпечується малим вихідним опором відкритого транзистора VТ4. Якщо на всі входи багатоемітерного транзистора VТ1 подані напруги, що відповідають рівню логічної одиниці, то струм через резистор НІ тече в базу транзистора VТ2, а потім підсилений струм з емітера VТ2 поступає в базу вихідного інвертуючого транзистора VТ4, відкриваючи його; при цьому транзистор VТЗ буде закритий і напруга на виході буде відповідати рівню логічного нуля. Якщо хоча б на одному вході багатоемітерного транзистора появиться вхідна напруга, що відповідає рівню логічного нуля, то відкриється відповідний перехід база-емітер, багатоемітерний транзистор перейде в стан насичення і потенціал його колектора стане близьким до нуля. Тобто. VТ2 закриється, VТЗ відкриється, а на виході схеми встановиться напруга, яка відповідає рівню логічної одиниці.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 2. Базова схема елемента "І–НІ" ТТЛ схеми з резистором в колекторі