- •В схеми «і» «або» на діодно резистивних ланках

- •2. Транзисторний ключ з спільнимемітером

- •Двокаскадна др. Логіка

- •4) Підвищення швидкодії транзисторна ключа за рахунок збільшення струму бази при включенні і зміни її напрямку на зворотній при виключені

- •5)Схема з трьома станами

- •6)Транзисторний ключ з нелінійним зворотним зв’язком

- •7) Схемы транзисторных ключей

- •11) Основна базова схема інжекційно інтегральної логіки

- •12) Ключ на мдп транзисторі. З мдп транзистором замість р(рез) стокового

- •15) Основна базова схема другого типу на мдп транзисторах

- •2. Його позитиви: простота.

- •3. Його недоліки: заборонені стани.

- •17) Реалізація рс тригера на елементах або нє

- •18 Реалізаціярстригера на елементах і нє

- •19. Т тригер(нічийний )

- •20) Д тригер

- •22. Двотактний регістр

- •25. Зсув інформації в регістрах в ліво

- •26. Зсув інформації в регістрах в право

- •27. Зсув інформації в регістрах Вліво вправо.

- •29) Лічильник з наскрізним переносом

- •31) За способом організації переносу (позички) між розрядами лічильники поділяють на такі типи:

- •32. Двійково-десяткові лічильники

- •33) Двохходовий одно розрядний суматор комбінаційного типу напівсуматор

- •34) Трьохходовий одно розрядний суматор комбінаційного типу повний суматор

- •35. Однорозрядні суматори накопичуючого типу

- •36. Послідовний багаторозрядний суматор

- •37. Багато розрядний суматор паралельної дії

- •38. Прямокутний дешифратор

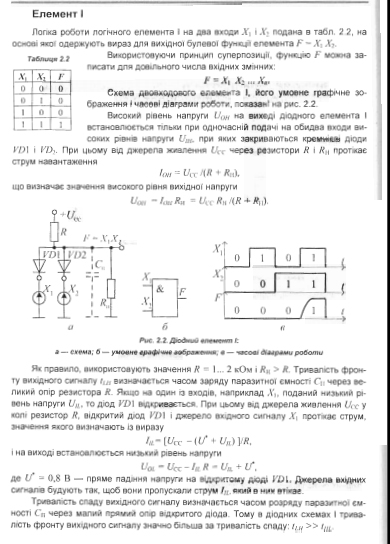

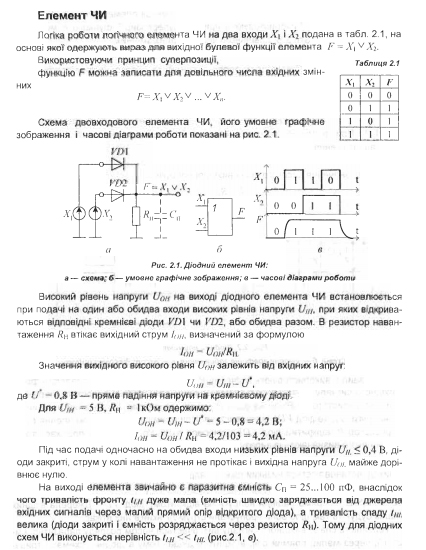

В схеми «і» «або» на діодно резистивних ланках

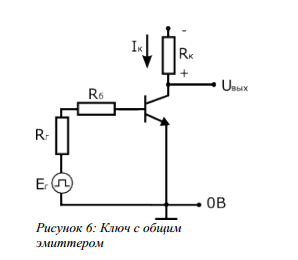

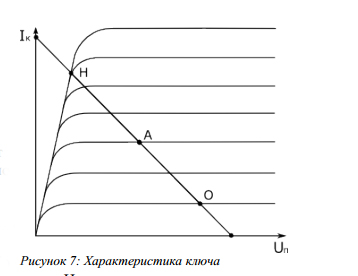

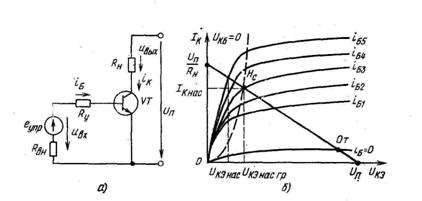

2. Транзисторний ключ з спільнимемітером

коефіцієнтпідсилення по напрузі ku> 1, коефіцієнт посилення по струму ki> 1 (струмколектора до струму бази). Дає посилення по потужності.

Ключ з спільним емітером найбільш поширений, тому забезпечує підсилення по напрузі і струму.

Тому ключі можна з'єднувати послідовно (каскадом). При цьому, сигнал не затухає.

Амплітуда (і струм, і напруга) сигналу зберігається при будь-якому числі включенихкаскадів.

У підсилювальних каскадах біполярний транзистор працює з

малими сигналами. Вхідний сигнал не перевищує

температурний потенціал.

Прінціп дії каскаду:

Навантажувальна пряма:

a) Uк = 0; I = Uп / Rк;

б) Ік = 0; Uк = Uп;

Точка А - перетин навантажувальної прямої з ВАХтранзистора при струмі бази Iб = Iба (струм бази в активномурежимі). У цій точці виконується співвідношення для вхідних сигналів Eг = Iба (Rг + Rб)+ Uбеа

Uбеа - падіння напруги на прямо зміщеномуемітерному переході. У залежності від ступенялегування емітера і бази Uбеа = 0,65 ... 0,8.

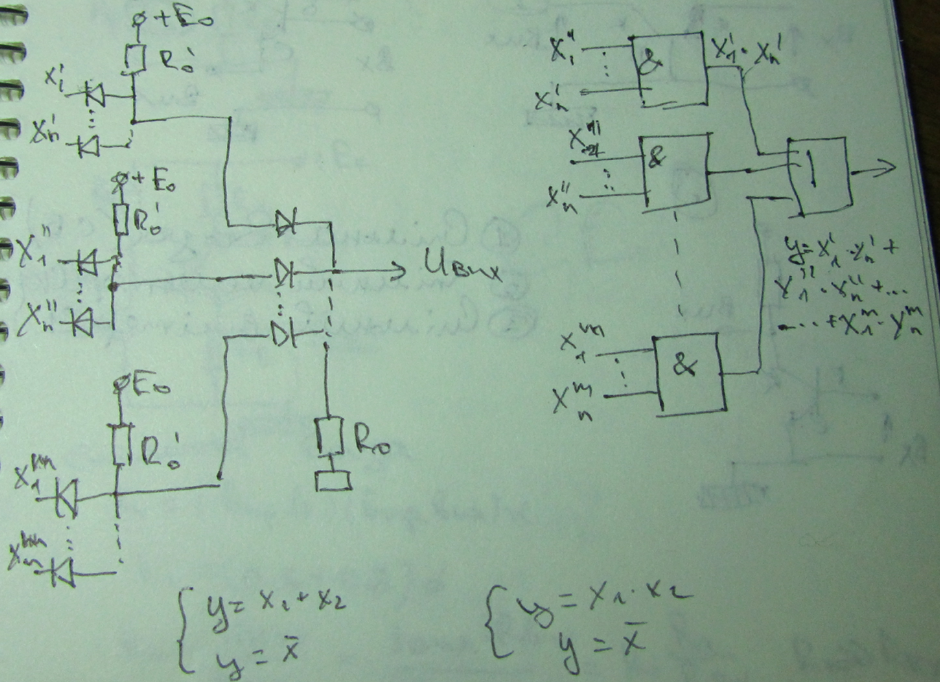

Двокаскадна др. Логіка

справа – функціональна схема двохкаскадної діодно-резистивної логіки.

Зліва – реалізація.

4) Підвищення швидкодії транзисторна ключа за рахунок збільшення струму бази при включенні і зміни її напрямку на зворотній при виключені

Д ля

скорочення перехідних процесів в ключі

необхідно підвищити швидкість накопичення

і розсмоктування заряда в базі і одночасно

знизити рівень граничного заряду,не

допускаючи при цьому накопичення в базі

надлишкового заряду. Вирішення цієї

задачі досягається збільшенням

прямого(при включенні)і

зворотнього (при виключенні) струмів

бази зменшенням

струма колектора в режимі насичення ,а

також введення в схему ключа зворотнього

звязку, запобігає перехід транзистора

при включенні в стані насичення.

ля

скорочення перехідних процесів в ключі

необхідно підвищити швидкість накопичення

і розсмоктування заряда в базі і одночасно

знизити рівень граничного заряду,не

допускаючи при цьому накопичення в базі

надлишкового заряду. Вирішення цієї

задачі досягається збільшенням

прямого(при включенні)і

зворотнього (при виключенні) струмів

бази зменшенням

струма колектора в режимі насичення ,а

також введення в схему ключа зворотнього

звязку, запобігає перехід транзистора

при включенні в стані насичення.

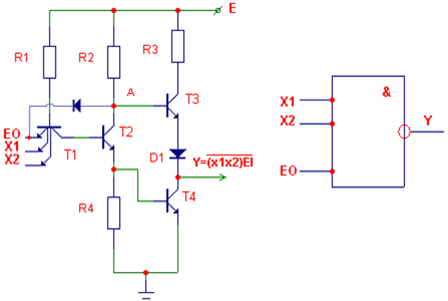

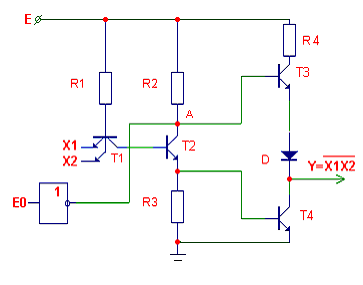

5)Схема з трьома станами

Схеми використовуються для організації обміну через загальну шину. На виході схеми може бути три стани: стан логічної «1», стан логічного «0» та третій стан – високоімпедансний. Він характеризується тим, що вихідні транзистори в парафазному підсилювачі знаходяться в режимі відсічки. Цей стан забезпечується подачею на вхід ЕО (Enable Out) високого рівня. В цьому випадку вхідні сигнали Х1 та Х2 на вихідний рівень не впливають.

Рис. 1. Схема з трьома станами

Розглянемо принцип роботи схеми (Рис. 37) за умови, коли X1=L, X2=H:

Якщо EO=L, то на базу Т2 струм не подається, оскільки Т1 працює в прямому режимі. Т2 закритий, відповідно і Т4 закритий також. На базу Т3 через R2 подається струм. Відповідно Т3 і D1 відкриті, на виході високий рівень.

Якщо EO=H, то в точці А буде низький рівень завдяки вихідному транзистору інвертора. Струм через R2 буде проходити на колектор вихідного транзистора інвертора і Т3 буде закритий. Таким чином, транзистори каскаду закриті, на виході буде третій стан.

Рис. 2. Схема з трьома станами (інший варіант підключення сигналу ЕО)

Розглянемо роботу схеми (Рис. 38):

На виході високий рівень, при цьому Т3 та D відкриті, Т2 та Т4 закриті. Струм через R2 іде на базу Т3. Щоб перевести схему в третій стан, на вхід ЕО подаємо високий рівень. В точці А встановлюється низький рівень, який визначається UКЕн вихідного транзистора інвертора. При цьому струм на базу Т3 йти не буде. Він через R2 піде на колектор вихідного транзистора інвертора. На виході схеми встановлюється третій стан, так як Т3 та Т4 закриті.

Розглянемо випадок, коли на вході низький рівень. При цьому Т3 та діод D закриті, Т2 та Т4 – відкриті. Вихідний рівень дорівнює напрузі UКЕн транзистора Т4. Щоб переключити схему в третій стан, подаємо високий рівень на вхід ЕО. В точці А встановлюється низький рівень, через R2 струм іде на інвертор, а на базу і колектор транзистора Т2 струм не поступає. Т2 та Т4 переходять в режим відсічки. На виході встановлюється третій стан.