- •Технічне завдання

- •Опис проекту

- •1. Структура мікрокомп`ютера

- •2 Зовнішній інтерфейс мікропроцесора Gnome

- •2.1 Порти мікропроцесора

- •2.2 Інтерфейс з зовнішньою пам'яттю

- •2.3 Переведення мікропроцесора до початкового стану

- •3. Програмна модель мікропроцесора

- •3.1 Програмно-доступні регістри

- •3.2 Множина інструкцій мікропроцесора

- •4. Внутрішня структура мікропроцесора

- •4.1 Інформаційний тракт мікропроцесора Gnome

- •1. Восьмирозрядний мультиплексор mux1

- •2. Програмно-доступні регістри pc,pc1, z, c, acc

- •3. Регістр інструкцій ir

- •4. Семирозрядний мультиплексор mux2 та суматор sm

- •5. Чотирирозрядний мультиплексор mux3

- •6. Арифметико-логічний пристрій

- •7. Регістровий файл

- •8. Допоміжні елементи

- •4.2 Цикли виконання команд

- •1. Цикл вибирання інструкцій (Instruction Fetch cycle -if)

- •2. Цикл декодування інструкції/вибирання операнда з регістрового файлу (Instruction decode/register fetch cycle - id)

- •3. Цикл виконання (Execute cycle - ex)

- •4.3 Керуючий автомат

- •1. Цикл вибирання інструкцій (Instruction Fetch cycle -if)

- •3. Цикл виконання (Execute cycle - ex)

- •Висновки

- •Список літератури

- •Додаток

8. Допоміжні елементи

В інформаційному тракті мікропроцесора Gnome присутні повторювачі, інвертори та інші логічні елементи, які забезпечують формування керуючих сигналів та інформації на шині даних.

4.2 Цикли виконання команд

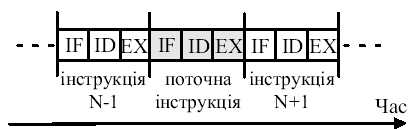

Інформаційний тракт мікропроцесора Gnome забезпечує виконання однієї інструкції в поточний момент часу. Кожна інструкція виконується за три цикли. Після виконання поточної інструкції мікропроцесор переходить до виконання наступної (рис.4.2.1), тобто в основу закладено принцип послідовного неконвеєрного опрацювання інструкцій.

Оскільки в даному курсовому проекті проектування мікропроцесора виконується на функціональному рівні, то при синтезі VHDL-моделі увага часовим витратам виконання кожного циклу не приділяється. Вважатимемо, що час виконання кожного з циклів є однаковий і дорівнює тривалості тактового інтервалу clock. Розглянемо детально множини мікродій (елементарних операцій), що виконуються у кожному циклі:

Рис.4.2.1. Послідовність виконання циклів команд в мікропроцесорі Gnome

1. Цикл вибирання інструкцій (Instruction Fetch cycle -if)

Виконуються наступні мікродії:

IR = ROM[PC];

PC = PC + 1.

Виконання першої мікродії забезпечує завантаження з пам‘яті інструкцій ROM за адресою, яка вказана в регістрі PC, команди з пам’яті програм в регістр інструкцій IR. Друга мікродія виконує інкремент лічильника команд PC на одиницю, що формує адресу комірки пам‘яті, з якої буде завантажуватись наступна планова інструкція. Обчислене значення адреси наступної команди на фазі IF може бути змінене на фазі EX під час виконання інструкцій переходу. Зауважимо, що нумерація мікродій в даному описі є суто умовною, оскільки згадані мікродії виконуються паралельно в часі і можуть розглядатись як одна сукупна мікродія.

2. Цикл декодування інструкції/вибирання операнда з регістрового файлу (Instruction decode/register fetch cycle - id)

У даному циклі проводиться декодування інструкції для виявлення команд, що працють з зовнішньою пам`ятю або одним з двох спеціалізованих пристроїв. Зокрема, це такі команди: LOAD та STORE в полі операнда яких (молодші 4-ри розряди) вказують адресу джерела або призначення операнда. Для таких команд встановлюються керуючі сигнали read,write,mx3 та sel_addr.

Для решти інструкцій в циклі ID вибір операнда виконується з регістрового файлу або безпосередньо «виймається» з поля команди, сюди також входять інструкції, які не вимагають операнда.

На цьому циклі також встановлюється сигнал pc1_we для запису у регістр PC1 значення, що містить лічильник команд (при надходженні сигналу переривання).

3. Цикл виконання (Execute cycle - ex)

Послідовність виконання елементарних операцій, що виконуються інформаційним трактом на фазі EX, залежить від типу інструкції, які можна умовно об‘єднати в три групи: арифметико-логічні операції, операції збереження результату, операції умовних та безумовних переходів.

У групу арифметико-логічних операцій входять команди: CLEAR_C, SET_C, LOAD_IMM, ADD_IMM, LOAD_DIR, ADD_DIR, XOR_DIR, TEST_DIR. При виконанні вищенаведених інструкцій в фазі EX бере участь арифметико-логічний пристрій, результат заноситься в акумулятор. В дану групу включені команди LOAD_IMM, LOAD_DIR, оскільки запис в акумулятор виконується за участю АЛП. Код операції alu_op для АЛП формує керуючий автомат:

ACC = ACC alu_op IR[3:0] або ACC = ACC alu_op RF[IR[3:0]].

Встановлюється значення mx3 для вибору джерела для АЛП.

Групу операцій збереження результату становлять команди STORE_DIR, LOAD та STORE. При виконанні даних інструкцій у фазі EX записується вміст акумулятора в один з двох пристроїв або читається інформація з них( LOAD та STORE), а також запис у регістровий файл (команда STORE_DIR).

DEV[R0[3:0]& IR[3:0]]=ACC або

ACC=DEV[R0[3:0]& IR[3:0]] – для команд LOAD та STORE;

RF[IR[3:0]]=ACC – для команди STORE_DIR, формується сигнал we=1 для запису у регістровий файл.

В принципі можливим є читання із зовнішньої пам`яті даного з певної комірки, що адресується так: ACC=MEM[R0[3:0]&IR[3:0]].

Група операцій умовних переходів складається з команд SKIP_C, SKIP_Z, JZ.

Команди безумовних переходів представлені однією єдиною командою RET. При виконанні команди SKIP_C або SKIP_Z, при встановленому в одиницю регістра переносу C або регістра ознаки нульового результата Z відповідно, виконується збільшення поточного значення лічильника команд на одиницю:

PC = PC +1 (inc_pc=Z або inc_pc=C відповідно)

Операція умовного переходу виконується записом адреси переходу в регістр PC:

PC = R0[2:0]&IR[3:0] та визначенням сигналу jump_pc=”11”.

Команда безумовного переходу виконує такі мікродії: встановлення сигналу jump_pc=”01”, встановлення можливості обробки переривання – відповідно сигнали disable_interrupt та enable_interrupt: disable_interrupt= '0' та enable_interrupt='1';

Якщо лінія маскованого апаратного переривання утримана в 1, то скидаємо сигнал запису до регістру PC1: pc1_we<='0'; вибираємо перехід по адресі R14_15 сигналом керування jump_pc<="10" мультиплексора MUX2; та забороняємо переривання на час виконання підпрограми обробки переривання:

disable_interrupt <= '1';

enable_interrupt<='0';

Окремо стоїть команда NOP, призначення якої не виконувати протягом трьох циклів ніяких змін у стані мікропроцесора.