- •Технічне завдання

- •Опис проекту

- •1. Структура мікрокомп`ютера

- •2 Зовнішній інтерфейс мікропроцесора Gnome

- •2.1 Порти мікропроцесора

- •2.2 Інтерфейс з зовнішньою пам'яттю

- •2.3 Переведення мікропроцесора до початкового стану

- •3. Програмна модель мікропроцесора

- •3.1 Програмно-доступні регістри

- •3.2 Множина інструкцій мікропроцесора

- •4. Внутрішня структура мікропроцесора

- •4.1 Інформаційний тракт мікропроцесора Gnome

- •1. Восьмирозрядний мультиплексор mux1

- •2. Програмно-доступні регістри pc,pc1, z, c, acc

- •3. Регістр інструкцій ir

- •4. Семирозрядний мультиплексор mux2 та суматор sm

- •5. Чотирирозрядний мультиплексор mux3

- •6. Арифметико-логічний пристрій

- •7. Регістровий файл

- •8. Допоміжні елементи

- •4.2 Цикли виконання команд

- •1. Цикл вибирання інструкцій (Instruction Fetch cycle -if)

- •2. Цикл декодування інструкції/вибирання операнда з регістрового файлу (Instruction decode/register fetch cycle - id)

- •3. Цикл виконання (Execute cycle - ex)

- •4.3 Керуючий автомат

- •1. Цикл вибирання інструкцій (Instruction Fetch cycle -if)

- •3. Цикл виконання (Execute cycle - ex)

- •Висновки

- •Список літератури

- •Додаток

3. Регістр інструкцій ir

Призначено для зберігання коду прочитаної інструкції. Керуючий сигнал ld_ir дозволяє завантажувати в регістр IR 8-розрядне слово інструкції з пам‘яті команд. Якщо сигнал ld_ir=’0’, то регістр зберігає своє попереднє значення, інакше з пам`яті команд до нього завантажується 8-розрядне слово команди. Вихід з цього регістра поступає до керуючого автомата, регістрового файлу, АЛП та на мультиплексор формування фізичної адреси.

4. Семирозрядний мультиплексор mux2 та суматор sm

Призначено для формування логічної адреси наступної інструкції на основі керуючих сигналів jump_pc[1:0] та inc_pc. Якщо inc_pc=’1’, на виході суматора є збільшений на одиницю вміст лічильника інструкцій PC, а якщо inc_pc=’0’,— поточне. Сигнал jump_pc керує формуванням наступної адреси pc_nxt з молодших розрядів регістра інструкцій IR[3:0], R0[2:0], PC1[6:0], R14_R15[6:0] та виходом з суматора. У таблиці 4.1.1 показано режими роботи мультиплексора.

Табл.4.1.1 Режими роботи мультиплексора MUX2

jump_pc |

Обране значення |

“00” |

pc_nxt<=pc_r+inc_pc |

“01” |

pc_nxt<=pc1_r |

“10” |

pc_nxt<=R14_15[6:0] |

“11” |

pc_nxt<=R0[2:0]&IR[3:0] |

5. Чотирирозрядний мультиплексор mux3

Призначений для передачі на АЛП значень відповідно з шини даних з регістру інструкції та з регістрового файлу. Керується дворозрядним керуючим сигналом mx3[1:0], що надходить з керуючого автомата. Має 4 стани, що показані у табл.4.1.2 нижче

Табл.4.1.2 Режими роботи мультиплексора MUX3

mx3 |

Обране значення |

“00” |

IR[3:0] |

“01” |

RF_r[3:0] |

“10” |

data[3:0] |

“11” |

збереження попереднього значення |

6. Арифметико-логічний пристрій

АЛП є комбінаційним пристроєм, який виконує певні операції над вхідними операндами. Для випадку розглядуваного мікропроцесора Gnome першим вхідним операндом АЛП (рис.4.1.1) є поточна інформація з акумулятора cur_acc, другим операндом є вихід мультиплексора MUX3, а також поточні значення ознак переносу curr_carry та нуля curr_zero. На виході блок АЛП залежно від коду операції alu_op формує результат: наступне значення акумулятора next_acc, отримане значення ознаки переносу next_carry, отримане значення ознаки нуля next_zero. Блок АЛП виконує невелику кількість операцій над 4-розрядними операндами (табл.4.1.3), що зумовлено простою системою команд мікропроцесора.

Табл.4.1.3 Множина операцій АЛП

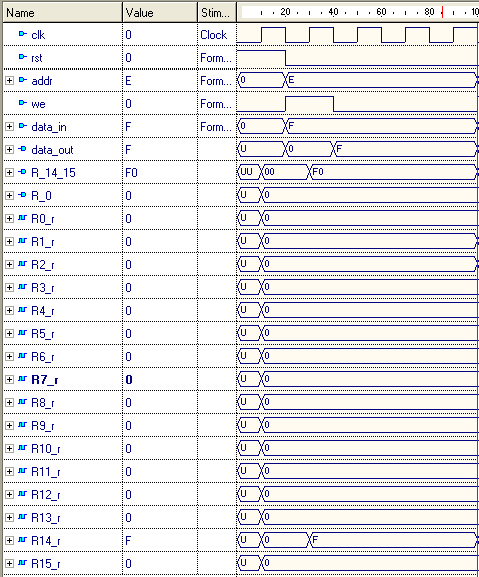

7. Регістровий файл

Регістровий файл являє собою сукупність 16 4-розрядних регістрів загального призначення. На кожен з них надходить глобальні сигнали синхронізації та скиду. Спільна вхідна шина даних одночасно видає значення на всі 16 регістрів, а дешифратор «обирає» той регістр, якому призначені ці дані. Дешифратором керує 4-розрядна шина адресу та сигнал запису до регістрового файлу (приходить з керуючого автомату), що активізує дешифратор.

Рис.4.1.2. Схема побудови регістрового файлу

Мультиплексор активізації не потребує, тобто процес читання з регістрового файлу відбувається постійно, потрібно лише подавати адресу регістру на вхід addr[3:0]. Одночасно з виходом мультиплексора (основним виходом регістрового файлу) видаються значення регістрів R0, R14 та R15, як цього вимагає технічне завдання на проектування. Значення регістру R0 приймає участь у формуванні адреси (мультиплексор MUX1), об`єднання регістрів R14 та R15 вказує на адресу підпрограми обробки переривання і воно надходить на мультиплексор MUX2. Вихід регістрового файлу RF_r[3:0] є одним з входів мультиплексора MUX3, що працює з акумулятором.

Рис.4.1.3. Часові діаграми роботи регістрового файлу