- •Технічне завдання

- •Опис проекту

- •1. Структура мікрокомп`ютера

- •2 Зовнішній інтерфейс мікропроцесора Gnome

- •2.1 Порти мікропроцесора

- •2.2 Інтерфейс з зовнішньою пам'яттю

- •2.3 Переведення мікропроцесора до початкового стану

- •3. Програмна модель мікропроцесора

- •3.1 Програмно-доступні регістри

- •3.2 Множина інструкцій мікропроцесора

- •4. Внутрішня структура мікропроцесора

- •4.1 Інформаційний тракт мікропроцесора Gnome

- •1. Восьмирозрядний мультиплексор mux1

- •2. Програмно-доступні регістри pc,pc1, z, c, acc

- •3. Регістр інструкцій ir

- •4. Семирозрядний мультиплексор mux2 та суматор sm

- •5. Чотирирозрядний мультиплексор mux3

- •6. Арифметико-логічний пристрій

- •7. Регістровий файл

- •8. Допоміжні елементи

- •4.2 Цикли виконання команд

- •1. Цикл вибирання інструкцій (Instruction Fetch cycle -if)

- •2. Цикл декодування інструкції/вибирання операнда з регістрового файлу (Instruction decode/register fetch cycle - id)

- •3. Цикл виконання (Execute cycle - ex)

- •4.3 Керуючий автомат

- •1. Цикл вибирання інструкцій (Instruction Fetch cycle -if)

- •3. Цикл виконання (Execute cycle - ex)

- •Висновки

- •Список літератури

- •Додаток

4. Внутрішня структура мікропроцесора

У пристрої обробки цифрової інформації виділяють інформаційний тракт (операційний блок, Datapath Unit) та керуючий автомат (блок керування, Control Unit).Такий підхід спрощує проектування та полегшує розуміння процесу функціонування пристрою (рис.4.1.1).

Рис.4.1.1. Функціональна схема пристрою обробки цифрової інформації

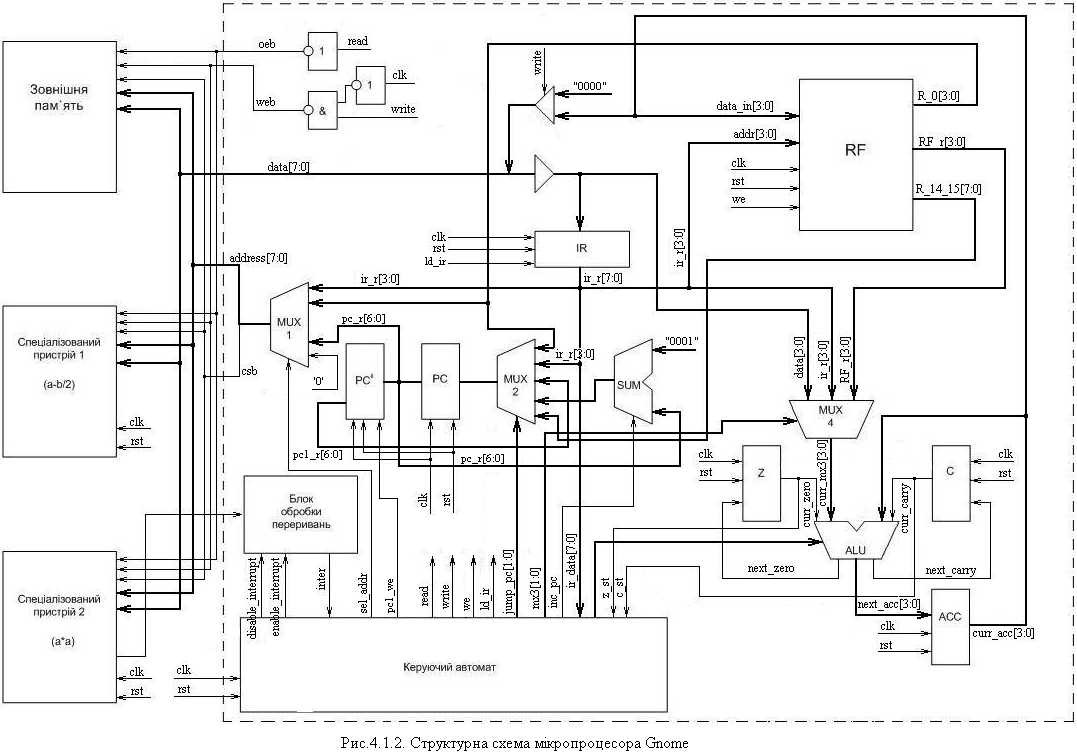

Інформаційний тракт мікропроцесора Gnome (рис.6) містить РЗП (регістровий файл), службові регістри, АЛП та допоміжні вузли, які забезпечують виконання інструкцій читанням даних з пам‘яті, їх зберігання та перетворення, до того ж інформаційний тракт формує для керуючого автомата сигнали стану з інформацією про стан операндів, окремих вузлів, особливих значень операндів, їх окремих розрядів та результати виконання операцій (наприклад, рівність нулю результату операції і т.п.).

Процес функціонування в часі мікропроцесора складається з послідовності тактових інтервалів, в яких інформаційний тракт виконує елементарні операції — передачу слова з регістра в регістр, зсув і т.п. Виконання даних елементарних операцій ініціюється надходженням в інформаційний тракт відповідних керуючих сигналів (мікродій) з керуючого автомата. Послідовність елементарних операцій керуючий автомат формує на основі коду операції (регістр інструкцій IR) та службових сигналів стану з інформаційного тракту. Сукупність мікродій, які забезпечують виконання інструкції за певну кількість циклів, називають мікропрограмою даної інструкції.

4.1 Інформаційний тракт мікропроцесора Gnome

Інформаційний тракт складається з таких компонентів:

1. Восьмирозрядний мультиплексор mux1

Цей мультиплексор формує фізичну адресу, виходячи з типу адресації, що необхідний для виконання біжучої команди. На нього надходить шина pc_r[6:0], що є виходом лічильника команд, шина R0[3:0], яка є виходом з регістра файлу, а фактично з регістру R0 та шина IR[3:0] – молодша тетрада регістра інструкцій. Керує мультиплексором сигнал sel_addr, що формується керуючим автоматом. Якщо sel_addr=’0’, то на виході мультиплексора формується адреса, старший біт якої ‘0’, а молодші сім – значення семирозрядного лічильника команд (застосовується для вибірки наступної команди з зовнішньої пам`яті). В протилежному випадку (sel_addr=’1’) на шину адреси надходить «злиття» бітів R0[3:0] та IR[3:0]. На виході мультиплексора формується сигнал вибору мікросхеми csb, що фактично є старшим бітом адреси address[7:0].

2. Програмно-доступні регістри pc,pc1, z, c, acc

Семирозрядний регістр PC призначено для зберігання вмісту лічильника команд. Регістр PC1 дублює значення регістру PC, при необхідності терміново виконати обробку переривання і відповідного переходу до нової адреси. Потім із нього відновлюється природній порядок виконання команд. Регістри Z та C є однорозрядними регістрами- тригерами, які зберігають поточне значення регістра ознаки нульового значення та регістра ознаки переносу. ACC – чотирирозрядний регістр, який виконує роль акумулятора. До кожного з них надходять глобальні сигнали синхронізації та скиду.