- •Развитие архитектуры универсальных микропроцессоров.

- •Этапы развития архитектуры 32-разрядных микропроцессоров фирмы Intel IA-32

- •Структура универсального микропроцессора c архитектурой IA-32

- •Группы регистров:

- •Основные функциональные регистры

- •Регистры общего назначения

- •Регистр флагов

- •Регистры процессора с плавающей точкой:

- •Тэг определяет содержимое регистра данных с целью оптимизации обработки.

- •Типы данных 32-разрядного универсального микропроцессора

- •Системные регистры: управляют

- •Биты, входящие в регистр управления CR0, определяют режим работы процессора:

- •Регистр CR1 зарезервирован.

- •Регистры системных адресов и системных сегментов

- •Регистры отладки и тестирования

Развитие архитектуры универсальных микропроцессоров.

Основные блоки 32- разрядного универсального микропроцессора

с архитектурой IA-32.

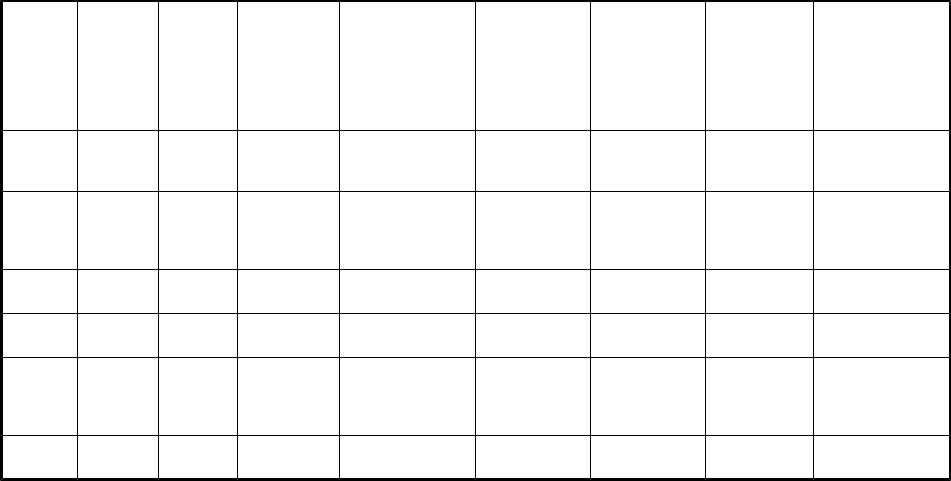

Этапы развития архитектуры 32-разрядных микропроцессоров фирмы Intel IA-32

|

|

Число |

Максима |

|

|

|

Год |

транзи |

|

||

|

с- |

льная |

Схема |

||

Моде |

начала |

||||

торов |

тактовая |

обработки |

|||

ль |

выпуск |

||||

на |

частота, |

данных |

|||

|

а |

||||

|

криста |

МГц |

|

||

|

|

|

|||

|

|

л-ле |

|

|

|

i386 |

1985 |

275 |

40 |

SISD, ФТ |

|

тыс. |

|||||

|

|

|

|

||

i486 |

1989 |

1,2 |

100 |

SISD, ФТ, ПЗ |

|

млн. |

|||||

|

|

|

|

||

Pentiu |

1993 |

3,1 |

200 |

- " - |

|

m |

млн. |

||||

|

|

|

|||

Pentiu |

1997 |

4,5 |

233 |

- " - + SIMD ФТ |

|

m MMX |

млн. |

||||

|

|

|

|||

Pentiu |

|

9,5 |

|

|

|

1999 |

млн. |

1400 |

- " - + SIMD ПЗ |

||

m III |

(28,1 |

||||

|

|

|

|||

|

|

млн)* |

|

|

|

Pentiu |

* - с учётом кэш-памяти L2 |

- " - |

|||

m 4 |

2000 |

42 млн. |

3800 |

||

|

|

|

|

||

Наличие кэш- памяти на кристалле

нет

да

-" -

-" -

-" - +кэш L2

-" -

Регистры

32-раз рядные с ФТ

- " - +80- разрядные с ПЗ

- " - - " -

- " - +128- разрядные SSE

- " -

Количест |

Количество |

во команд |

конвейеров / |

в системе |

ступеней |

команд |

конвейера |

220 |

– |

- " - |

– |

- " - |

2/5 |

+ 57 |

4/14 |

+70 |

5/11 |

+144 |

9/31 |

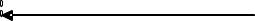

Структура универсального микропроцессора c архитектурой IA-32

Процессор |

Блок |

Блок |

|

чисел с |

сегментац |

страничной адресации |

|

фиксированной |

ии |

|

Кэш |

точкой |

|

||

АЛУ |

|

Блок ассоциативной |

памят |

РОН |

|

ь |

|

|

трансляции |

|

|

32 |

|

страничного адреса TLB |

|

|

|

|

Блок управления памятью MMU

Процессор чисел с плавающей запятой FPU АЛУ

РОН |

80 |

Устройство |

|

Управление |

Внутрення |

управления |

|

предвыборкой |

|

|

я |

||

|

|

|

|

|

|

|

магистрал |

|

|

|

ь |

Управление |

|

Буфер команд |

|

защитой |

|

|

|

|

|

|

|

Блок управления

Блок

интерфейс а внешней шины

Внешняя

магистрал

ь

Группы регистров:

-основные функциональные регистры;

-регистры процессора с плавающей точкой;

-системные регистры;

-регистры отладки и тестирования.

Основные функциональные регистры

–регистры общего назначения;

–регистр указателя команд;

–регистр флагов;

–сегментные регистры.

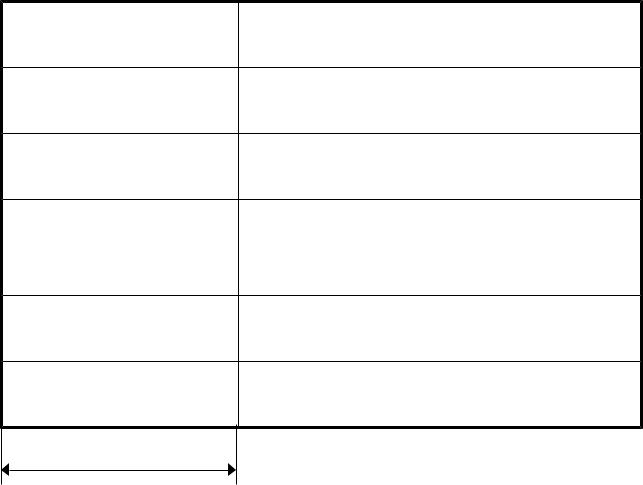

Регистры общего назначения

31 |

16 15 |

|

0 |

||

EAX |

|

|

|

|

|

|

|

(AH) |

AX |

(AL) |

|

EBX |

|

|

(BH) |

BX |

(BL) |

ECX |

|

|

(CH) |

CX |

(CL) |

EDX |

|

|

(DH) |

DX |

(DL) |

ESI |

|

|

|

SI |

|

EDI |

|

|

|

DI |

|

EBP |

|

|

|

BP |

|

ESP |

|

|

|

SP |

|

|

|

32 |

|

|

|

Регистр указателя команд

31 |

16 15 |

0 |

||

EIP |

|

|

|

|

|

|

|

IP |

|

32

32

Регистр флагов

31 |

16 15 |

0 |

||

EFLAGS |

|

|

|

FLAGS |

32

Регистр флагов содержит признаки результата выполненной команды, а также разряды, управляющие работой микропроцессора.

К битам состояния регистра флагов относятся: ZF – признак нуля результата;

SF – знак результата;

OF – признак переполнения; CF – флаг переноса;

PF – признак чётности.

В состав флагов управления входят:

IF – флаг разрешения маскированных аппаратных прерываний; TF – флаг ловушки, или трассировки;

NТ – бит вложенной задачи;

IOPL –уровень привилегий ввода/вывода .

|

Сегментные регистры |

|

CS |

Сегмент кода |

|

SS |

Сегмент стека |

|

DS |

Сегмент данных |

|

ES |

Доп. сегмент |

|

|

данных |

|

FS |

- |

‘’ - |

GS |

- |

‘’ - |

16

Регистры процессора с плавающей точкой:

•регистры данных;

•регистры тэгов;

•регистр состояния;

•указатели команд и данных FPU;

•регистр управления FPU.

Тэг определяет содержимое регистра данных с целью оптимизации обработки.

Регистр состояния содержит указатель вершины блока данных, работающего в режиме стека, признаки результата и ошибок, возникающих при выполнении операции в FPU, а также флаг переполнения и антипереполнения стека регистров данных.

Регистр управления управляет округлением (к ближайшему значению, вниз, вверх, к нулю), точностью (длина мантиссы 24, 53 или 64 бита), а также содержит маску признаков ошибок, фиксируемых в регистре состояния.

Указатели команд и данных содержат адрес команды, вызвавшей ошибку, и адрес использованного операнда.