- •Понятие информации и ее виды; подходы к оценке количества информации. Аналоговая и дискретная форма представления информации. Единицы дискретной информации.

- •Понятие алгоритма. Операция. Программа. Команда. Укрупненная структура и принцип функционирования эвм.

- •Способы представления дискретной информации. Позиционные и непозиционные системы счисления.

- •Системы счисления, используемые в эвм - двоичная, восьмиричная, шестнадцатиричная и двоично-десятичные системы счисления.

- •Перевод чисел из одной позиционной системы счисления в другую. Диапазон представления чисел со знаком и без знака. Точность представления числа.

- •Прямой, обратный и дополнительный коды. Выполнение операций двоичной арифметики в прямом, обратном и дополнительных кодах.

- •Представление чисел с фиксированной точкой и с плавающей запятой. Символьные данные.

- •Булевы функции одной и нескольких переменных. Функционально полные системы булевых функций. Логические операции и элементы для их выполнения.

- •Нормальные формы логических функций. Минимизация булевых функций.

- •Логические элементы и комбинационные схемы. Сложность комбинационных схем по Квайну.

- •Выполнение арифметических операций на основе функционально-полной системы логических функций. Комбинационные сумматоры и алу.

- •Последовательностные схемы (цифровые автоматы). Запоминающие элементы - триггеры.

- •Основные типы операционных элементов эвм. Шины. Организация передач между операционными элементами.

- •Сдвигающие регистры. Регистровые файлы.

- •Счетчики. Дешифраторы.

- •Основные характеристики компьютеров.

- •Быстродействие и производительность компьютеров.

- •Структура процессора простейшей базовой эвм. Назначение основных функцинальных устройств и элементов процессора.

- •Структура операционного автомата базовой эвм.

- •Выполнение команд в базовой эвм (на примере арифметической команды).

- •Выполнение команд в базовой эвм (на примере команд условного перехода).

- •Выполнение команд в эвм (на примере базовой эвм).

- •Понятие архитектуры и организации эвм. Основные элементы архитектуры.

- •Принцип программного управления.

- •Каноническая структура компьютера. Принстонская и гарвардская архитектура эвм.

- •Достоинства и недостатки неймановской архитектуры эвм.

- •Организация системы памяти. Внутренняя память процессора,

- •Организация ввода-вывода данных.

- •Структура компьютера с программно-управляемым интерфейсом.

- •Структура компьютера с общей шиной

- •Структура компьютера с каналами ввода-вывода.

- •Понятие системного интерфейса. Контроллеры внешних устройств. Параллельная и последовательная передача данных.

- •Способы адресации, используемые в эвм.

- •Способы адресации с модификацией адреса.

- •Стековая адресация. Выполнение вычислений в стековых эвм (на примере).

- •Система команд компьютера. Основные виды команд.

- •Понятие cisc и risc-архитектуры

- •Характерные особенности risc-процессоров

- •Однопрограммный режим работы компьютера.

- •Мультипрограммный режим работы компьютера.

- •Средства мультипрограммирования.

- •Функции управляющих программ операционной системы.

- •Привилегированные операции и состояния процессора.

- •Организация прерывания программ. Источники прерываний.

- •Основные сведения об организации ввода/вывода информации. Программно-управляемая передача данных и режим прямого доступа к памяти.

- •Организация синхронного обмена.

- •Организация асинхронного обмена.

- •Организация обмена по прерыванию.

- •Организация системы прерываний. Вектор прерывания. Понятие глубины прерывания. Уровни прерывания.

- •Понятие приоритета прерываний. Абсолютный и относительный приоритет. Организация обработки запросов на прерывание.

- •Программирование приоритетов по маске и по порогу.

- •Организация обмена в режиме прямого доступа к памяти. Функции контроллера пдп.

- •Принцип микропрограммного управления. Операционный и управляющий автоматы, их взаимодействие.

- •Микрооперация. Микрокоманда. Виды микрокоманд .Микропрограмма.

- •Горизонтальное кодирование микрокоманд.

- •Вертикальное кодирование микрокоманд.

- •Смешанное кодирование микрокоманд.

- •Управляющий автомат с хранимой микропрограммой.

- •Управляющий автомат с жесткой логикой.

- •Каноническая структура процессора.

- •Цикл выполнения машинных команд и его фазы.

- •Синхронный конвейер команд. Оценка его производительности.

- •Причины снижения производительности при конвейерном режиме обработки команд.

- •Способы повышения производительности при конвейерной обработке команд.

- •Структура процессора i8086. Организация конвейера команд. Регистровый файл процессора.

- •Особенности организации процессора i80286. Конвейер команд. Организация защиты памяти на аппаратном уровне.

- •Особенности организации конвейера команд в процессорах Pentium. Структура процессора. Понятие суперскалярной архитектуры.

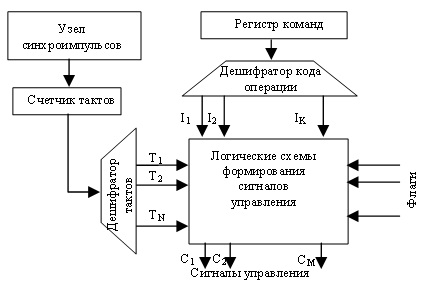

Управляющий автомат с жесткой логикой.

К од

операций (КОП), хранящийся в регистре

команды, используется для определения

того, какие сигналы управления и в какой

последовательности должны формироваться.

При этом, желательно иметь в УУ отдельный

логический сигнал для каждого кода

операции (IK). Это может быть реализовано

с помощью дешифратора.

од

операций (КОП), хранящийся в регистре

команды, используется для определения

того, какие сигналы управления и в какой

последовательности должны формироваться.

При этом, желательно иметь в УУ отдельный

логический сигнал для каждого кода

операции (IK). Это может быть реализовано

с помощью дешифратора.

Сигналы управления, по которым выполняется микрооперация, должны вырабатываться в строго определенные моменты времени, поэтому все сигналы управления "привязаны" к импульсам синхронизации. Счетчик тактов сбрасывается (устанавливается в состояние Т1) по окончании цикла очередной команды. Цикл команды может потребовать разного количества тактов. На каждом такте вырабатывается своя микрокоманда, состоящая из нескольких сигналов управления. Дополнительным фактором, влияющим на выработку сигналов управления, являются флаги.

Каноническая структура процессора.

Каноническая (основополагающая) структура процессора состоит из операционного и управляющего автоматов, которые вместе обеспечивают выполнение заданного набора процессорных операций: последовательную выборку команды из оперативной памяти; декодирование кода операции; определение операндов, с которыми работает команда; выполнение предписанной командой операции; возможно, сохранение результата операции; определение адреса следующей команды. Естественно, что выборка команд и данных происходит из оперативной памяти, поэтому оперативная память, входящая вместе с процессором в ядро компьютера, включена в состав канонической структуры процессора. Чтобы упростить понимание рисунка, определяющего структуру операционного автомата, представляющего часть процессора, ограничимся рассмотрением основных деталей операционного автомата, а управляющий автомат будем представлять одним прямоугольником, понимая, что функции управляющего автомата весьма многогранны и описывают управление процессами выполнения многих десятков, а в ряде случаев и сотен различных команд. Так, оставим без внимания все вопросы организации мультипрограммирования в компьютере, обработку прерываний и другие сложные для восприятия моменты организации компьютера как целостной системы.

К аноническая

структура процессора изображена на

рис. Операционный автомат процессора

состоит из трех частей: арифметико-логического

устройства АЛУ, регистров специального

назначения (РСН) и регистров общего

назначения (РОН). Эти части связаны между

собой с помощью трех шин – шин А,

В

и С,

управляемых множеством сигналов Y={{yA},

{yB},

{yC},

{yАЛУ},

ЧТОП, ЗПОП, ЗОП}, формируемых управляющим

автоматом процессора.

аноническая

структура процессора изображена на

рис. Операционный автомат процессора

состоит из трех частей: арифметико-логического

устройства АЛУ, регистров специального

назначения (РСН) и регистров общего

назначения (РОН). Эти части связаны между

собой с помощью трех шин – шин А,

В

и С,

управляемых множеством сигналов Y={{yA},

{yB},

{yC},

{yАЛУ},

ЧТОП, ЗПОП, ЗОП}, формируемых управляющим

автоматом процессора.

Цикл выполнения машинных команд и его фазы.

Цикл выполнения машинной команды. Для реализации одной команды требуется выполнить определенное количество микрокоманд, каждая из которых инициируется одним тактовым импульсом. Общее число тактовых импульсов, требуемых для выполнения команды, определяет время ее выполнения, называемое циклом команды. Цикл команды обычно включает один или несколько машинных циклов. Устройство управления базовой ЭВМ может находиться в четырех возможных состояниях: выборки команды, выборки адреса, исполнения и прерывания. Длительность каждого из этих четырех состояний определяет время выполнения соответствующего машинного цикла. Более подробно в 23 пункте.