- •Структура и принцип работы эвм

- •Виды сигналов

- •Конъюнкция – умножение (и )

- •Дизъюнкция – сложение (или)

- •Отрицание – ( не ) х (не х)

- •Логические основы проектирования цифровых устройств Теория конечных автоматов

- •Машина поста (мп)

- •Машина Поста - математическое построение, предназначенное для уточнения понятия алгоритма. Машина Поста состоит:

- •Из неограниченной в обе стороны ленты, разделенной на ячейки;

- •Из головки чтения/записи, которая может перемещаться вдоль ленты и управляется программой на специальном языке из шести команд.

- •Программа для машины Тьюринга, задается в виде таблицы, определяющей команды для головки. Классификация эвм

- •Обобщенная структурная схема эвм

- •Эволюция структуры построении эвм Структурная схема эвм с каналами ввода-вывода (для больших и средних эвм)

- •Структура персональных эвм с общей шиной

- •Память Структура микросхем памяти

- •Оперативное Запоминающее Устройство (озу)

- •Структура draм (динамической памяти с произвольным доступом)

- •Конструкция дзу

- •Регенерация. Режимы регенерации

- •Типовая диаграмма регенерации

- •Типы динамической памяти

- •Sgram (Synchronus graphic ram) (синхронная графическая динамическая память).

- •Модули динамических оперативных зу

- •Статические зу с произвольным доступом (сзу)

- •Память будущего

- •1. Голографическая память

- •2. Молекулярная память

- •3. Наноструктуры

- •Постоянное запоминающее устройство (пзу)

- •Флэш-память (Flash Memory)

- •Организация flash-памяти

- •Используется три поколения fm:

- •Многоуровневые ячейки (mlc - Multi Level Cell).

- •Разновидности Flash Memory

- •Внешняя память

- •Жесткий диск

- •Головки чтения/записи

- •Процессор

- •Основная структура процессора

- •Программное управление работой эвм. Адресная структура команд и способы адресации операндов

- •Шины расширения пк

- •Шина eisa. (Extended Industry Standard Architecture)

- •Локальная шина vlb

- •Шина pci

- •Шина ieee 1394

- •Применения midi

- •Операционные системы

- •Локальные вычислительные сети

- •Сетевые топологии

- •Радиальная структура (звезда).

- •Последовательная цепочечная структура (кольцо).

- •Шинная структура.

- •4. Древовидная структура

- •Компоненты сети

- •Чем отличается концентратор от коммутатора

- •Концентраторы

- •Коммутаторы

- •Когда следует использовать концентратор или коммутатор

- •Неэкранированная витая пара (Unshielded Twisted Pair) utp

- •Волоконно-оптические кабели

- •Описание и применение волоконно-оптических кабелей

- •8.1 Радиоволны

- •8.1.1 Узкополосная радиосвязь

- •8.1.2 Широкополосная радиосвязь

- •8.2 Радиосеть

- •8.3 Связь через спутниковые каналы

- •Сетевые карты (nic- Network Interface card)

- •9.4. Беспроводные сетевые карты

- •Тенденции развития компьютеров в будущем

- •1.Молекулярные компьютеры

- •2.Газовые компьютеры

- •3.Квантовые компьютеры

- •4.Биокомпьютеры

Основная структура процессора

Программное управление работой эвм. Адресная структура команд и способы адресации операндов

Автоматизация вычислительного процесса осуществляется в ЭВМ на основе принципа программного управления, сформулированного американским ученым Дж. фон Нейманом в 1945 г. при разработке еще первых моделей ЭВМ. Согласно этому принципу все вычисления, выполняемые ЭВМ, задаются соответствующей программой, заранее составленной и введенной в ее память. Программа состоит из последовательности управляющих команд. Каждая команда содержит указания на выполнение конкретной машинной операции и место нахождения (адреса) в памяти участвующих в ней данных (операндов). Коды команд представляют собой многоразрядные двоичные комбинации, состоящие из 1 и 0, и внешне ничем не отличаются от двоичных кодов числовых данных. В таком виде эти коды хранятся в памяти ЭВМ.

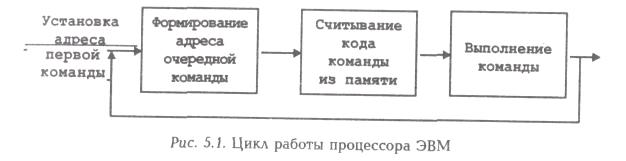

Идеи, заложенные в программе, технически реализуются процессором (микропроцессором), который считывает из памяти очередную команду программы, расшифровывает ее, а затем подключает соответствующим образом необходимые устройства и узлы ЭВМ для выполнения данной команды. По существу, процессор организует автоматическое повторение одного и того же цикла, включающего в себя следующие действия (рис. 5.1):

формирование адреса в памяти очередной команды, при этом адрес первой команды программы формируется вне цикла специальным способом, например, нажатием соответствующей клавиши;

считывание кода команды из памяти и расшифровка ее содержания;

в

ыполнение

команды путем соответствующего

подключения необходимых блоков и

устройств ЭВМ.

ыполнение

команды путем соответствующего

подключения необходимых блоков и

устройств ЭВМ.

Количество таких циклов определяется количеством команд в программе.

В многоразрядном формате кода машинной команды выделяются два так называемых поля: операционное и адресное (рис. 5.2).

В операционном поле команды размещается код той операции (Kon), которую необходимо выполнить данной командой. В адресном поле размещены коды адресов тех ячеек памяти, в которых хранятся данные (операнды), участвующие в выполнении данной операции.

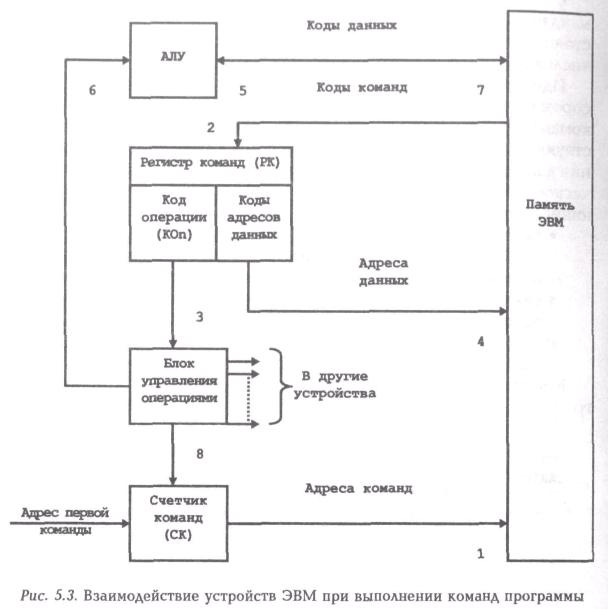

На рис. 5.3 приведена схема, иллюстрирующая характер и последовательность функционального взаимодействия отдельных узлов и устройств ЭВМ в процессе выполнения команд программы. На схеме цифрами указана последовательность работы узлов и устройств ЭВМ в цикле выполнения одной команды.

Для формирования адреса очередной команды используется счетчик команд (СК). Считанный из памяти код команды хранится в регистре команд (РК), состоящем из регистра КОп и регистра адресов данных. Синхронное и согласованное взаимодействие узлов и устройств ЭВМ при выполнении команд программы обеспечивает блок управления операциями (БУО) процессора. Указанное взаимодействие производится в следующей последовательности:

По адресу, сформированному в СК, считывается из памяти код очередной команды.

Код команды поступает в РК.

Код операции из РК расшифровывается в БУО, в результате чего формируются необходимые управляющие сигналы для выполнения данной операции.

Адреса данных из РК поступают в память ЭВМ и по ним производится считывание необходимых операндов.

Считанные коды данных (операндов) поступают в АЛУ.

П

роизводится

выполнение в АЛУ требуемой операции.

роизводится

выполнение в АЛУ требуемой операции.

Результат выполнения операции передается для хранения в память ЭВМ.

В счетчике команд формируется адрес следующей команды.

Если имеет место естественный порядок выполнения команд программы, то адрес очередной команды формируется путем прибавления к адресу предыдущей команды ее длины в байтах. В общем случае этот адрес может быть любым другим и зависеть, например, от результата выполнения предыдущей операции (команды).

Таким образом, функциональное взаимодействие устройств ЭВМ при реализации вычислительного процесса определяется прежде всего машинными командами программы, хранящейся в памяти. Структура машинной команды, как уже отмечалось, состоит из отдельных полей, имеющих определенное функциональное назначение. В такой структуре представлен, с одной стороны, код операции (КОп), подлежащей выполнению, а с другой — адресный код, который содержит в том или ином виде информацию об адресах операндов, участвующих в той операции, а также указывает в явном или неявном виде адрес, по которому следует поместить результат операции в память ЭВМ.

Структура команды с жестко установленным значением каждого разряда (бита) в любом поле команды называется форматом. Обычно формат команды имеет разрядность, кратную одному биту.

Для машинных команд существуют различные варианты адресации операндов, в зависимости от которых существуют одно-, двух-, трехадресные, а также безадресные команды (рис. 5.4).

Одноадресная команда содержит код операции и адрес А одного операнда. При этом второй операнд уже подготовлен предыдущей командой к выполнению и находится в АЛУ процессора (рис. 5.4, а).

Двухадресная команда содержит код операции и адреса двух операндов — А1 и А2 (рис. 5.4, б). Большинство команд современных ЭВМ — двухадресные.

Трехадресная команда содержит код операции, адреса двух операндов — А1 и А2, а также адрес A3, по которому записывается в память результат выполнения этой операции (рис. 5.4, в).

Безадресная команда содержит только код операции, в котором неявно подразумевается вся недостающая информация (рис. 5.4, г).

В общем случае адресный код команды отличается от исполнительного адреса, т.е. адреса памяти, по которому производится фактическое обращение. Правильный выбор способа адресации, т.е. механизма формирования исполнительного адреса, имеет большое значение для эффективного использования технических средств ЭВМ.

Рассмотрим основные способы адресации, сделав при этом оговорку, что кроме этих способов возможны также их различные комбинации.

1. Непосредственная адресация. В команде содержится непосредственно сам операнд, и при этом не требуется выделения ячейки памяти для его хранения. Данный способ удобен для организации вычислений с использованием различных констант.

2. Прямая адресация. Адрес операнда в явном виде задан в соответствующем поле команды и совпадает с исполнительным адресом.

Подразумеваемая адресация. В адресном поле команды не содержится явных сведений об адресах операндов, но они подразумеваются. Например, в двухадресной структуре команд ЭВМ результат выполнения арифметической операции обычно помещается по адресу А2.

Укороченная адресация. Суть ее заключается в использовании только младших разрядов адреса (при этом старшие разряды заранее подразумеваются нулевыми). Этот вид адресации используется лишь для фиксированных ячеек памяти с короткими (малыми) адресами.

Косвенная адресация. В адресном поле команды указывается адрес ячейки памяти, в которой хранится адрес операнда или очередной команды, т.е. косвенная адресация — это адресация адреса. Косвенная адресация широко используется в персональных ЭВМ, имеющих относительно короткую разрядность, так как позволяет преодолеть ограничения короткого формата их команд.

Регистровая адресация. В адресном поле команды указываются омера регистров в составе процессора (микропроцессора), в которых хранятся операнды. Это позволяет повысить производительность процессора за счет уменьшения числа обращений к ОП.

Автоинкрементная и автодекрементная адресация. По сути, оба пособа адресации являются косвенной регистровой адресацией и основаны на хранении в регистре косвенного адреса операнда. Если после выполнения команды производится автоматическое приращение адреса, хранящегося в регистре, то имеет место автоинкрементная адресация; если производится автоматическое уменьшение этого адреса, то — автодекрементная адресация. Эти способы наиболее эффективны при адресации больших информационных массивов.

Стековая адресация используется в безадресных командах обращения к стековой памяти или просто стеку. При этом за стек принимается руппа ячеек памяти с последовательными адресами, а в процессе один из регистров выделяется под указатель стека. Обслуживание обращений к стековой памяти строится по принципу: «Первым пришел — последним обслуживается». При записи в стек нового слова содержимое регистра с указателем стека увеличивается на единицу, а при считывании из стека — уменьшается на единицу. Стековая адресация позволяет безадресным командам выбирать из стека операнды, а результат заносить в стек.

9. Относительная адресация (базирование). Исполнительный адрес в этом случае определяется некоторым базовым адресом и смещением D относительно этого адреса. При этом базовый адрес обычно задается косвенной регистровой адресацией, для чего в адресном поле команды указывается номер В регистра базы процессора, содержимое которого (В) является базовым адресом операнда. Путем суммирования базового адреса и смещения получается исполнительный адрес Аисп обращения к основной памяти, т.е. Аисп = (В) + D, где буква В, заключенная в круглые скобки, означает содержимое регистра базы с номером В.

10. Индексная адресация. При обработке массивов однотипных данных часто требуется производить обработку различных операндов одними и теми же командами. Механизм индексирования позволяет модифицировать адресные части команд (т.е. адреса операндов). Часто индексная адресация применяется в сочетании с базированием. Для этого в составе регистров процессора выделяются два регистра: базовый регистр В и регистр индекса X. В адресном поле команды указываются номера В и X этих регистров, а также смещение D. С учетом базирования и индексирования исполнительный адрес основной памяти определяется суммой Аисп = (В) + (X) + D, где буквы В и X, заключенные в круглые скобки, обозначают соответственно содержимое регистров базы и индекса, имеющих адреса (номера) В и X.