Конфигурационные Байты

CONFIG 0 Адрес 0080h

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

UCON |

WSA1# |

WSA# |

XALE# |

RD1 |

RD0 |

PAGE# |

SRC |

SRC - Source Mode/Binary Mode Select. При значении 1 выбирается исходный режим, при 0 - двоичный режим, т.е. совместимость на уровне двоичных кодов с MCS-51.

PAGE- если бит равен 1, то выбор страничного режима (А15:8/D7:0 на Р2 и А7:0 на Р0).

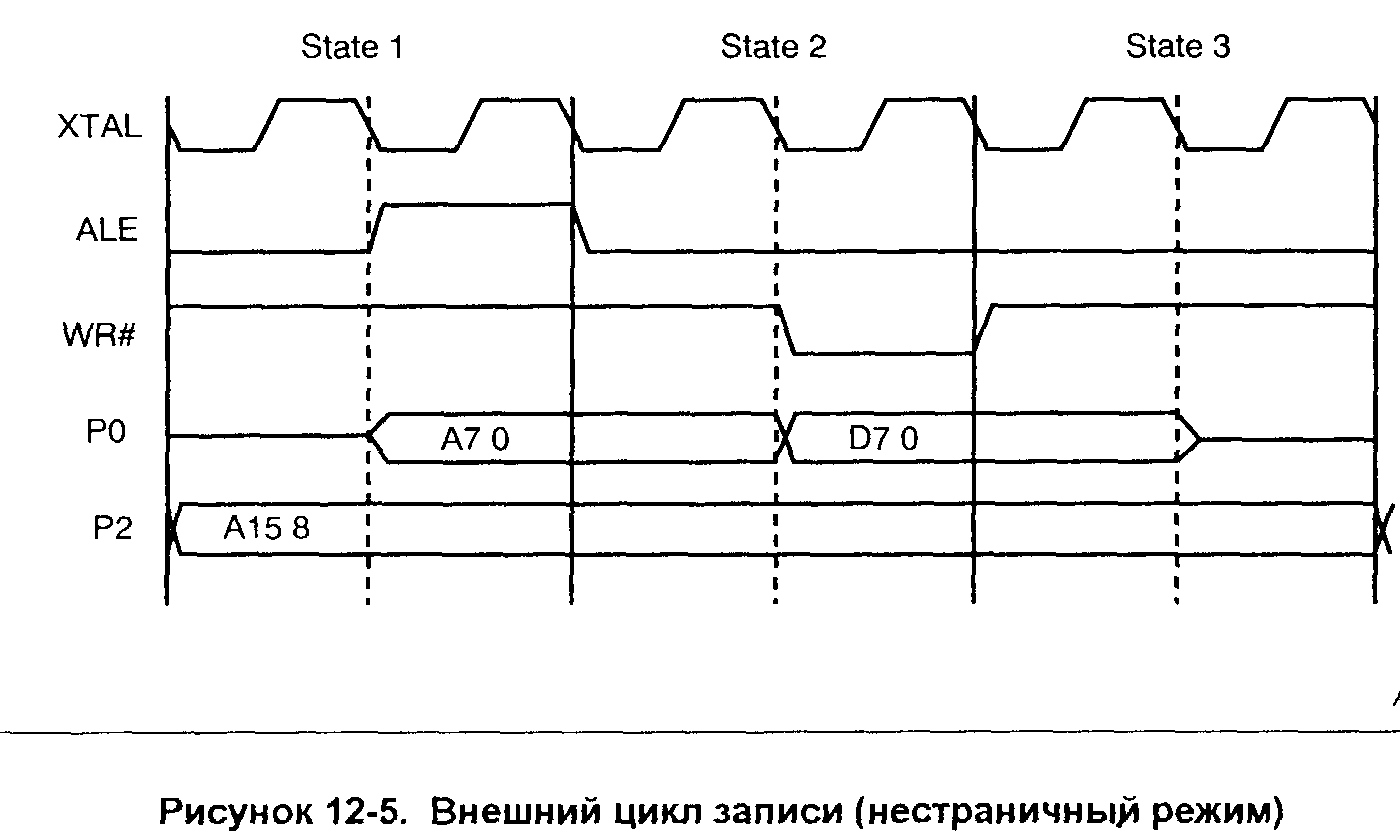

- если бит равен 0, то выбор нестраничного режима (А15:8 на Р2 и А7:0/D7:0 на Р0 (обеспечивается совместимость с 44-выводными MCS 51 в корпусе PLCC)). Ниже внешние циклы рассмотрим отдельно .

RD1, RD0 - Биты выбора функций сигналов RD# и PSEN#. Ниже рассмотрим отдельно.

XALE# (Extend ALE) - Бит управления растяжкой сигнала.

При XALE# = 0 сигнал ALE удлиняется на один такт.

WSA# - Бит управления состоянием ожидания при выборке из всех регионов , исключая регион 00:.

При одном бите управления WSA = 0 в цикл вставляется одно состояние ожидания, при WSA = 1нет.

При двух битах управления комбинации значений битов WSA1# и WSA# включают во внешний цикл при: 00 – три состояния ожидания, 01-два состояния ожидания, 10 – одно состояние ожидания, 11 – нет ожиданий.

UCON -бит выбора местоположения байта конфигурации только для микросхем 87C251Sx (OTPROM / EPROM): при UCON=0 выбор информации о конфигурации из памяти на кристалле;

при UCON=1 выбор информации о конфигурации из памяти на кристалле, если EA# = 1 или же из внешней памяти, если EA# = 0.

WR# -Write. Выходной сигнал записи во внешнюю память.

Если конфигурационные биты RD1 = RD0 = 1, то WR# стробирует запись только в ячейки 00:0000Н-7F:FFFFH.

При иных значениях RD1 и RD0, WR# стробирует запись в любые ячейки памяти.

CONFIG 1 Адрес 0081h

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

— |

— |

— |

INTR |

WSB |

WSB1# |

WSB0# |

EMAP# |

EMAP# - EPROM MAP. При EMAP# = 0старшие 8 Кбайт внутренней памяти программ (FF:2000H-FF:3FFFH) отображаются в 00:Е000Н-00:FFFFH.

При EMAP# = 1 памяти программ не отображается, а обращение в регион 00:E000H–00:FFFFH производит доступ во внешнююRAM.

WSB (Wait State B)- Бит управления ожиданием при выборке из области 01: только для подсемейства SA.

При WSB = 0 в цикл вставляется одно состояниеожидания (RD#, WR#, and PSEN#) , при WSA = 1 нет.

WSB1#, WSB0# - Комбинации значений этих бит во внешний цикл шины включают: 00 – три состояния ожидания; 01 – два состояния; 10 – одно состояние; 11 – ноль сотояний.

INTR - Interrupt Mode.

Если бит установлен, прерывания засылают 4 байта в стек (3 байта регистра PC и регистр PSW1).

Если бит сброшен, прерывания засылают 2 байта в стек (2 младших байта регистра PC).

7÷5 – резервные биты для будущего использования. Устанавливаются в 1 при программировании.

Выбора функций сигналов RD# и PSEN#.

RD1 RD0 |

RD# (Р3.7) |

PSEN# |

Возможности |

00 |

А17 (Р1.7) А16 (Р3.7) |

строб Чт для всех адресов |

256-Kbyte внешней памяти |

01 |

А16 (Р3.7) |

строб Чт для всех адресов |

128-Kbyte внешней памяти |

10 |

Только Р3.7 |

строб Чт для всех адресов |

64-Kbyte внешней памяти |

11 |

строб Чт для всех адресов≤7F:FFFFh |

строб Чт для всех адресов≥80:0000h |

64-Kbyte внешней памяти. Совместимость с MCS 51 |