КИ-08-2 Хламов С. В.

Практическое занятие №3.

Тема: "Организация интерфейса с внешней памятью систем на базе 8XC251SB".

Реализовать ряд примеров дизайна внешней памяти систем на базе микроконтроллера 8хC251SB, которые иллюстрируют гибкость на уровне вариантов конфигурации, особенно по сигналам PSEN# и RD#..

Задание 1.а)Нестраничный режим, 64 Кбайт внешнего ПЗУ,64 Кбайт

внешнего ОЗУ

(Example 5:RD1:0 = 11, 16-bit Bus, External EPROM and RAM).

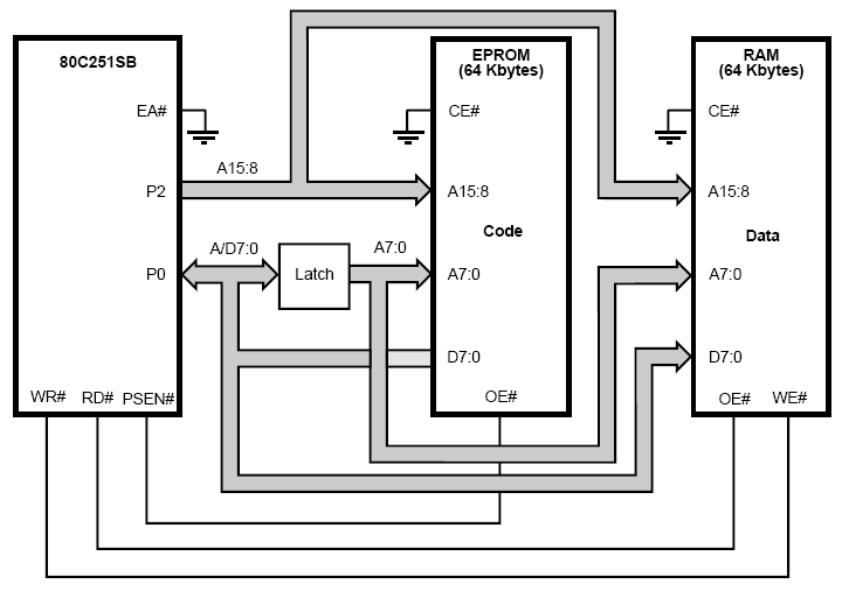

Схема на рис 12-13 показывает 80C251SB, который сконфигурирован так, что RD# стробирует адреса 7F:FFFFH, а сигнал PSEN# стробирует адреса 80 0000H (RD1 == 1 и RD0 = 1).

Рисунок 12-13. Нестраничный режим с внешним ПЗУ и ОЗУ.

В схеме на рис. 12-14 показаны два способа адресации внешней памяти в области внутренней памяти.

Нижние 1056 байт внешнего ОЗУ могут быть адресованы в регионе 01:.

При адресации других ячеек внешнего ОЗУ в регионе 00: или в регионе 01: на внешние контакты шины выдается одинаковый адрес.

Однако, если внешнее ПЗУ и внешнее ОЗУ требуют разного числа тактов ожидания, то внешнее ОЗУ должно целиком адресоваться через регион 01:. (Повторимся, что все регионы 00:, FE: и FF: всегда имеют одинаковое число тактов ожидания. См. Состояния ожидания (WSA, WSB, XALE) ниже в информации для справок).

В последующих примерах показаны две возможные схемы адресации внешнего ОЗУ:

1. Применения, требующие быстрого доступа к стеку

Если в системе необходим быстрый доступ к стеку, то стек удобно расположить в быстром внутреннем ОЗУ данных (00:0020Н-00:041FH), а когда необходимо, выводить в более медленное внешнее ОЗУ данных. В этом случае внешнее ОЗУ может иметь ожидание, если только ПЗУ (EPROM) имеет ожидание. В противном случае, если стек прокручивается выше ячейки 00:041FH, то обращение к внешнему ОЗУ происходит без ожидания. Регионы 00: и 01: слева на рис. 12-14 относятся к данному примеру.

2. Применения, требующие быстрого доступа к данным

Если быстрый доступ к блоку данных важнее, чем быстрый доступ к стеку, то данные могут храниться во внутреннем ОЗУ данных, а стек целиком размещаться во внешней памяти.

Если внешнее ОЗУ имеет ожидание, в ПЗУ (EPROM) работает без ожидания, то внешнее ОЗУ должно целиком адресоваться в регионе 01:. Регионы 00: и 01: справа на рис. 12-14 относятся к данному примеру.

Дать ответы на ниже приведенные вопросы!

Как устанавливается приведенная в задании конфигурация?

Бит PAGE (бит 1 в CONFIG 0) служит для выбора между страничным и нестраничным режимом выборки команд и задает структуру внешней шины. См. описание страничного режима и структуры шины в разделе "Циклы шины в страничном режиме" на стр. 12-10.

• РАGE = 1. 8XC251SB работает в постраничном режиме. Шина имеет такую же структуру, как и архитектура MCS 51, а внешний цикл выборки команд занимает два состояния (4ТOSC).

• PAGE =- 0. 8XC251SB работает в страничном режиме. Шина имеет структуру, отличную от архитектуры MC'S 51, а внешний цикл выборки команд занимает при некоторых условиях всего одно состояние (2ТOSC).

Как по рис.12-13 определить, что приведена конфигурация нестраничного режима обращения к внешней памяти?

Задание 1.b) Страничный режим, 64 Кбайт внешнего ПЗУ, 64 Кбайт внешнего ОЗУ (Example 6:RD1:0 = 11, 16-bit Bus, External EPROM and RAM).

In this example, an 80C251SB operates in page mode with a 16-bit external address bus interfaced

to 64 Kbytes of EPROM and 64 Kbytes of RAM (Figure 13-27). The 80C251SB is configured

so that RD# is asserted for addresses £ 7F:FFFFH, and PSEN# is asserted for addresses ³

80:0000.

This system is the same as Example 5 (Figure 13-25) except that it operates in page mode. Accordingly,

the two systems have the same memory map (Figure 13-26), and the comments on addressing

external RAM apply here also.