- •Введение

- •1 Аналитический обзор

- •1.1 Бинарно-десятичные коды

- •1.2 Ттл логика

- •1.3 Триггеры

- •1.3.1 Общая характеристика

- •1.4 Счетчики

- •1.4.1 Основные характеристики счетчиков

- •1.4.2 Организация переносов в счетчике

- •1.5 Преобразователи кодов

- •2 Конкретизация технического задания

- •3 Выбор и описание работы элементной базы

- •4 Синтез структурной схемы

- •6 Разработка электрической схемы

- •Заключение

- •Список использованных источников

4 Синтез структурной схемы

Определим число устойчивых состояний и элементов памяти.

Ксч=10;

Nmin=10;

m=[log2Nmin]=4;

Nизб=2m – Nmin=6;

Составим таблицу состояний счетчика с внутренним кодом 5-4-2-1 (таблица 4.1).

Таблица 4.1 – Состояния реверсивного счетчика.

Состояние в момент t |

Состояния в момент t+1 |

Функции переходов |

|||||||||||

Q3 |

Q2 |

Q1 |

Q0 |

Q3 |

Q2 |

Q1 |

Q0 |

|

|

|

|

||

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

▲ |

||

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

▲ |

▼ |

||

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

▲ |

||

0 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

▲ |

▼ |

▼ |

||

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

▲ |

▼ |

0 |

0 |

||

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

▲ |

||

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

▲ |

▼ |

||

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

▲ |

||

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

▲ |

▼ |

▼ |

||

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

▼ |

▼ |

0 |

0 |

||

Функции переходов принимают следующие значения:

=0,

если и в текущий, и в следующий момент

времени сохраняется 0;

=0,

если и в текущий, и в следующий момент

времени сохраняется 0;

=1, если и в текущий, и в следующий момент времени сохраняется 1;

=▲, если состояние триггера меняется из 0 в 1;

=▼, если состояние триггера меняется из 1 в 0.

Избыточные комбинации счетчика: 0101; 0110; 0111; 1100; 1101; 1111.

На основе таблицы состояний переходим к картам функций переходов, приведенных на рисунке 4.1.

|

000 |

001 |

011 |

010 |

00 |

0 |

0 |

0 |

0 |

01 |

▲ |

x |

x |

x |

11 |

▼ |

x |

x |

x |

10 |

1 |

1 |

1 |

▼ |

![]()

|

000 |

001 |

011 |

010 |

00 |

0 |

0 |

▲ |

0 |

01 |

▲ |

x |

x |

x |

11 |

▼ |

x |

x |

x |

10 |

0 |

▲ |

▲ |

▼ |

|

000 |

001 |

011 |

010 |

00 |

0 |

▲ |

▼ |

1 |

01 |

▼ |

x |

x |

x |

11 |

0 |

x |

x |

x |

10 |

1 |

▼ |

▼ |

0 |

|

000 |

001 |

011 |

010 |

00 |

▲ |

▼ |

▼ |

▲ |

01 |

▼ |

x |

x |

x |

11 |

0 |

x |

x |

x |

10 |

▲ |

▼ |

▼ |

0 |

Рисунок 4.1 – Карты функций переходов счетчика

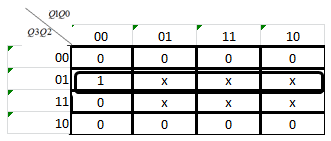

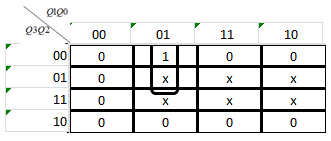

На основе карт функций переходов и словаря переходов RS-триггера (таблица 4.2) составляем карты Карно (рисунок 4.2 и рисунок 4.3) и проводим их минимизацию.

Таблица 4.2 – Словарь переходов RS-триггера

Fa |

S |

R |

0 |

0 |

х |

1 |

х |

0 |

↑ |

1 |

0 |

↓ |

0 |

1 |

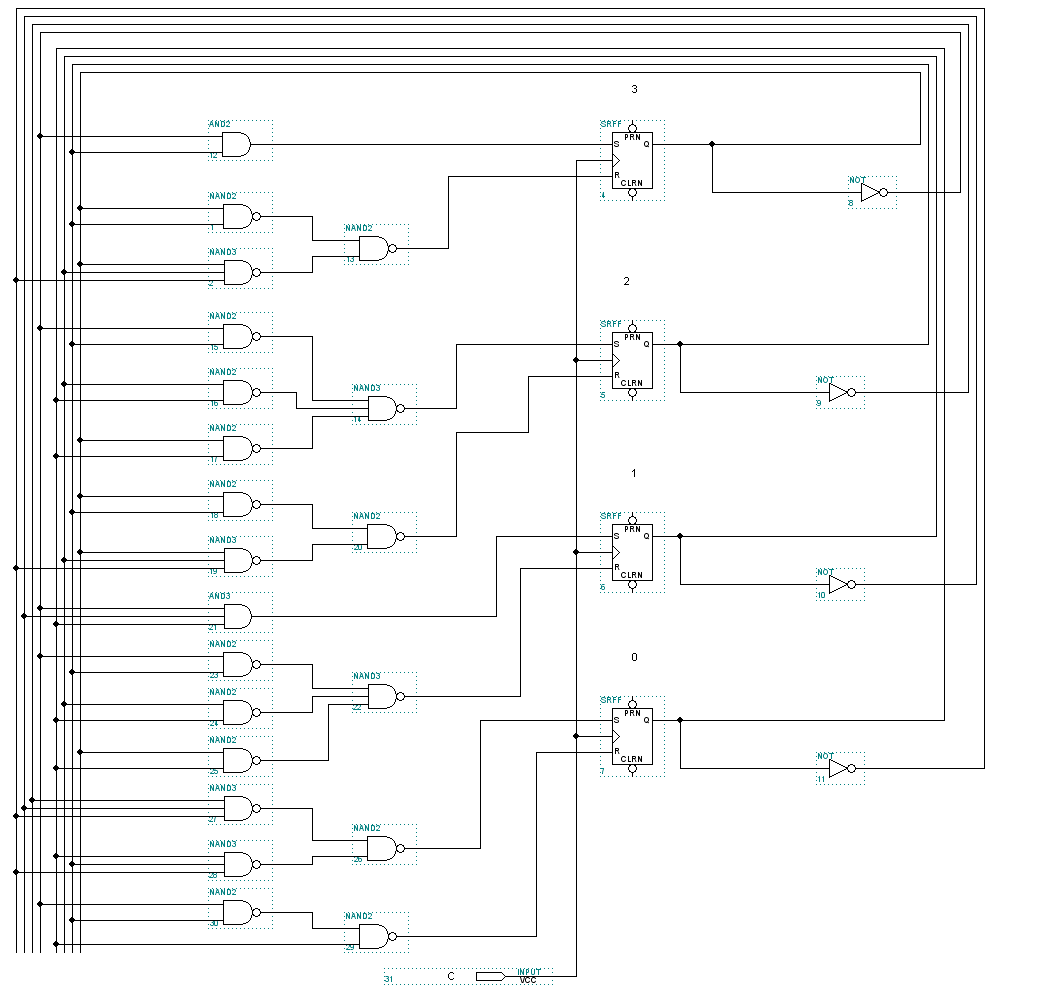

S3

S3 S2

S2

S1

S1

S0

S0

Рисунок 4.2 – Карты Карно для входов S

R3

R3

R2

R2

R1

R1

R0

R0

Рисунок 4.3 – Карты Карно для входов R

Преобразуем полученные выражения для реализации в базисе И-НЕ. Для этого над левой и правой частью ставят знак двойной инверсии, а затем по теореме де Моргана преобразуют инверсию дизъюнкции в конъюнкцию инверсий:

;

;

;

;

;

;

;

;

;

;

;

;

;

;

.

.

На основе полученных выражений строим структурную схему счетчика (рисунок 4.4).

Рисунок 4.4 – Структурная схема счетчика

С учётом заданной элементной базы (логического базиса) и минимизированных логических функций на выходах комбинационного устройства строится структурная схема преобразователя кодов.

.

Таблица 4.3 – Таблица истинности преобразователя кодов

-

Q3

Q2

Q1

Q0

Y3

Y2

Y1

Y0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

1

0

0

1

0

0

0

1

0

0

0

1

1

0

1

0

0

0

1

0

0

0

1

0

1

1

0

0

0

0

1

1

0

1

0

0

1

1

0

0

0

1

0

1

0

1

0

0

1

1

0

1

1

1

0

1

0

1

1

0

0

1

1

0

0

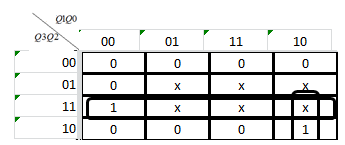

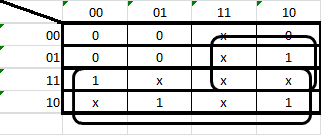

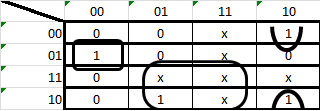

На основе таблицы истинности составляем карты Карно (рисунок 4.5) и проводим их минимизацию.

Рисунок 4.5 – Карты Карно преобразователя кодов

Преобразуем полученные выражения для реализации в базисе И-НЕ:

;

;

;

;

;

;

.

.

На основе полученных выражений строим структурную схему преобразователя кодов (рисунок 4.6).

Рисунок 4.6 – Структурная схема преобразователя кодов

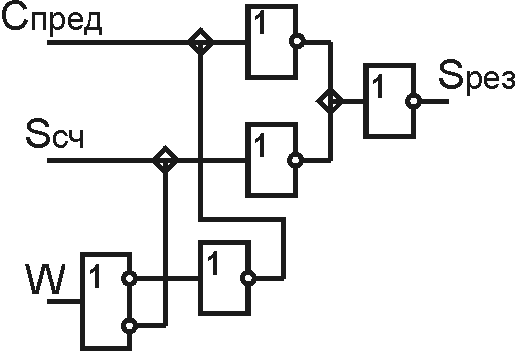

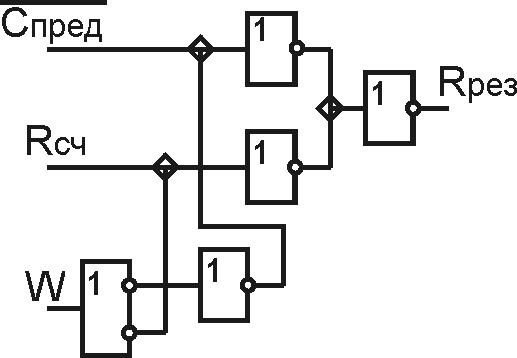

Для разделения режимов счёта и предустановки в счётчике перед каждыми R- и S-входами триггеров предусмотрено устройство, реализующее функцию мультиплексирования сигналов:

SСЧ (RСЧ) – значение функции перехода соответствующего S(R)-входа

СПРЕД (

)

– сигнал соответствующего выхода

(разряда) преобразователя кодов

)

– сигнал соответствующего выхода

(разряда) преобразователя кодов

Для S-входов: Для R-входов:

W |

SРЕЗ |

|

W |

RРЕЗ |

0 |

SСЧ |

0 |

RСЧ |

|

1 |

СПРЕД |

1 |

|

где: W – сигнал управления;

SРЕЗ (RРЕЗ) – результирующий сигнал, поступающий на S(R)-вход триггера

а) б)

Р

исунок

4.7 – структурная схема мультиплексирующего

устройства для S-входа

(а) и для R-входа

(б)

исунок

4.7 – структурная схема мультиплексирующего

устройства для S-входа

(а) и для R-входа

(б)

С учётом функций переходов для R- и S-входов триггеров счётчика в режиме счёта, структурной схемы преобразователя кодов и структурной схемы мультиплексирующего устройства для R- и S-входов триггеров составляется структурная схема проектируемого счётчика (рисунок 4.3).[6]

Подключая полученный преобразователь кодов к выходам суммирующего счетчика, получаем структурную схему проектируемого устройства (рисунок 4.7).

Рисунок 4.7 – Структурная схема проектируемого устройства

5 АНАЛИЗ РАБОТЫ СТРУКТУРНОЙ СХЕМЫ

Анализ структурной схемы проводится с использованием временных диаграмм работы устройства (рисунок 5.1)

Рисунок 5.1 – Временные диаграммы работы устройства

Такт1.

При

подаче на вход

логического «0» происходит установка

в «1» всех триггеров. Данный процесс

происходит независимо от сигналов,

поступающих на входы триггеров, и сигнала

синхронизации. На выходах счётчика

устанавливается значение 1111 («1» в

двоичной системе исчисления). На выходе

переноса в старший разряд устанавливается

логический «0», так как это инверсный

выход четвёртого триггера.

логического «0» происходит установка

в «1» всех триггеров. Данный процесс

происходит независимо от сигналов,

поступающих на входы триггеров, и сигнала

синхронизации. На выходах счётчика

устанавливается значение 1111 («1» в

двоичной системе исчисления). На выходе

переноса в старший разряд устанавливается

логический «0», так как это инверсный

выход четвёртого триггера.

Такт 2.

На вход разрешения предустановки W подаётся логический «0». На элементы «И» мультиплексирующих устройств, на которые поступают сигналы SСЧ и RСЧ, также подаётся сигнал W, т.е. логический «0». Поэтому независимо от сигналов SСЧ и RСЧ на выходах этих элементов будет логический «0». На оставшиеся входные элементы «И» мультиплексирующих устройств подаются соответствующие сигналы с выходов преобразователя кодов, причём сигналы с прямых выходов преобразователя кодов поступают на элементы «И» мультиплексирующих устройств, подключённых к R-входам триггеров, а сигналы с инверсных выходов преобразователя кодов поступают на инверторы мультиплексирующих устройств, подключённых к S-входам триггеров. При поступлении отрицательного фронта сигнала синхронизации информация с выходов преобразователя кодов записывается в соответствующие триггеры. На выходе переноса в старший разряд появляется логический «0». В данном случае на выходах счётчика устанавливается значение 0010 (во внутреннем коде счётчика оно соответствует числу «2» двоичной системы исчисления). Таким образом, в счётчике устанавливается число, с которого будет начат счёт.

Такт 3.

На

вход разрешения предустановки W

подаётся логическая «1». На элементы

«И» мультиплексирующих устройств, на

которые поступают сигналы Спред

и Rпред,

подаётся сигнал

,

т.е. логический «0». Поэтому независимо

от сигналов Спред

и Rпред

на выходах этих элементов будет логический

«0». На элементы «И» мультиплексирующих

устройств, на которые поступают сигналы

SСЧ

и RСЧ,

подаётся сигнал W,

т.е. логическая «1». Поэтому сигналы SСЧ

и RСЧ

поступают на соответствующие входы

триггеров. Таким образом, осуществляется

счет (вычитание) и на выходах счётчика

устанавливается значение 0001 (во внутреннем

коде счётчика оно соответствует числу

«1» двоичной системы исчисления).

,

т.е. логический «0». Поэтому независимо

от сигналов Спред

и Rпред

на выходах этих элементов будет логический

«0». На элементы «И» мультиплексирующих

устройств, на которые поступают сигналы

SСЧ

и RСЧ,

подаётся сигнал W,

т.е. логическая «1». Поэтому сигналы SСЧ

и RСЧ

поступают на соответствующие входы

триггеров. Таким образом, осуществляется

счет (вычитание) и на выходах счётчика

устанавливается значение 0001 (во внутреннем

коде счётчика оно соответствует числу

«1» двоичной системы исчисления).