- •Основные понятия и определения. Лекция №1. Микропроцессоры и микроконтроллеры. Общие сведения. Шина адреса, шина управления.

- •Что такое микропроцессор?

- •Шинная структура связей

- •Лекция №2. Архитектура микропроцессоров и микроконтроллеров. Risc и cisc система команд в мп и мк. Архитектура микропроцессорных систем

- •Типы микропроцессорных систем

- •Risc и cisc система команд в мп и мк

- •Команды пересылки данных

- •Арифметические команды

- •Логические команды

- •Команды переходов

- •Лекция №3. Внутренняя организация процессора. Назначение и функциональные особенности блоков. Быстродействие процессора

- •Классификация и структура

- •Процессорное ядро

- •Функции процессора

- •Лекция №4. Последовательность выполнения команд микропроцессором. Режимы адресации.

- •Адресация операндов

- •Методы адресации

- •Адресация байтов и слов

- •Регистры процессора

- •Система команд мп. Лекция №5. Архитектура изучаемого микроконтроллера. Назначение внутренних блоков. Микроконтроллеры семейства avr

- •Микроконтроллер aTtiny2313 фирмы Atmel

- •Архитектура микроконтроллеров семейства Tiny

- •Организация памяти

- •Память программ

- •Память данных

- •Способы адресации памяти данных

- •Прямая адресация

- •Лекция №6. Блок регистров общего назначения. Команды с непосредственной адресацией. Различные режимы адресации. Энергонезависимая память данных (eeprom)

- •Доступ к eeprom

- •Меры предосторожности

- •Счетчик команд и выполнение программы

- •Лекция №7. Система команд изучаемого микроконтроллера.

- •Лекция №8. Команды переходов и сдвига. Остальные команды.

- •Выводы микроконтроллера. Лекция №9. Описание выводов микроконтроллера.

- •Описание выводов

- •Кварцевый генератор

- •Лекция №10. Пространство ввода/вывода микроконтроллера.

- •Порт ввода/вывода в

- •Регистр направления данных порта b - ddrb

- •Альтернативные функции portb

- •Порт ввода/вывода d

- •Регистр направления данных порта b - ddrb

- •Порт d, как порт ввода/вывода общего назначения

- •Альтернативные функции порта d

- •Регистры и обработка прерываний микроконтроллера. Лекция №13. Регистр состояния и указатель стека микроконтроллера.

- •Регистр состояния - sreg

- •Указатель стека sp

- •Лекция №14. Обработка внешних прерываний в микроконтроллере.

- •Обработка внешних прерываний. Общий регистр маски прерываний gimsk

- •Общий регистр флагов прерываний

- •Регистр управления микроконтроллером - mcucr

- •Лекция №15. Обработка прерываний от таймеров/счетчиков в микроконтроллере.

- •Регистр маски прерывания от таймера/счетчика - timsk

- •Регистр флагов прерываний от таймеров/счетчиков - tifr

- •Прерывания в микроконтроллере. Лекция №16. Определитель таймеров/счетчиков. Принцип работы таймера/счетчика 0.

- •Определитель таймеров/счетчиков

- •Регистр управления таймером/счетчиком 0 - tccr0

- •Лекция №17. Режимы работы таймера/счетчика 1.

- •Регистр a управления таймером/счетчиком 1 - tccr1a

- •Таймер/счетчик 1 - tcnt1h и tcnt1l

- •Регистр совпадения a таймера/счетчика 1 - ocr1ah и ocr1al

- •Регистр захвата таймера/счетчика 1 - icr1h и icr1l

- •Таймер/счетчик в режиме шим

- •Лекция №18. Универсальный асинхронный приемо-передатчик. Принцип работы и управления.

- •Передача данных

- •Прием данных

- •Управление uart регистр ввода/вывода uart

- •Регистр состояния uart (usr)

- •Регистр управления uart (ucr)

- •Генератор скорости передачи

- •Лекция №19. Аналоговый компаратор и сторожевой таймер микроконтроллера.

- •Аналоговый компаратор регистр управления и состояния аналогового компаратора (acsr).

- •Регистр управления сторожевым таймером - wdtcr

- •Форматы представления чисел в эвм. Лекция №20. Формат чисел с фиксированной точкой и элементарные операции над ними.

- •Компьютерное представление целых чисел

- •Лекция №21. Формат чисел с плавающей точкой и элементарные операции над ними.

- •Компьютерное представление вещественных чисел

- •Цифро-аналоговые преобразователи. Лекция №22. Основные понятия и определения цифро-аналоговых преобразователей (цап). Виды погрешностей преобразования.

- •Параметры цап

- •Лекция №23. Цап на взвешивающей матрице и на матрице r-2r. Принцип работы. Достоинства и недостатки. Цап на взвешивающей матрице

- •Цап на матрице r-2r

Логические команды

Логические команды выполняют над операндами логические (побитовые) операции, то есть они рассматривают коды операндов не как единое число, а как набор отдельных битов. Этим они отличаются от арифметических команд. Логические команды выполняют следующие основные операции:

логическое И, логическое ИЛИ, сложение по модулю 2 (Исключающее ИЛИ);

логические, арифметические и циклические сдвиги;

проверка битов и операндов;

установка и очистка битов (флагов) регистра состояния процессора (PSW).

Команды логических операций позволяют побитно вычислять основные логические функции от двух входных операндов. Кроме того, операция И (AND) используется для принудительной очистки заданных битов (в качестве одного из операндов при этом используется код маски, в котором разряды, требующие очистки, установлены в нуль). Операция ИЛИ (OR) применяется для принудительной установки заданных битов (в качестве одного из операндов при этом используется код маски, в котором разряды, требующие установки в единицу, равны единице). Операция "Исключающее ИЛИ" (XOR) используется для инверсии заданных битов (в качестве одного из операндов при этом применяется код маски, в котором биты, подлежащие инверсии, установлены в единицу). Команды требуют двух входных операндов и формируют один выходной операнд.

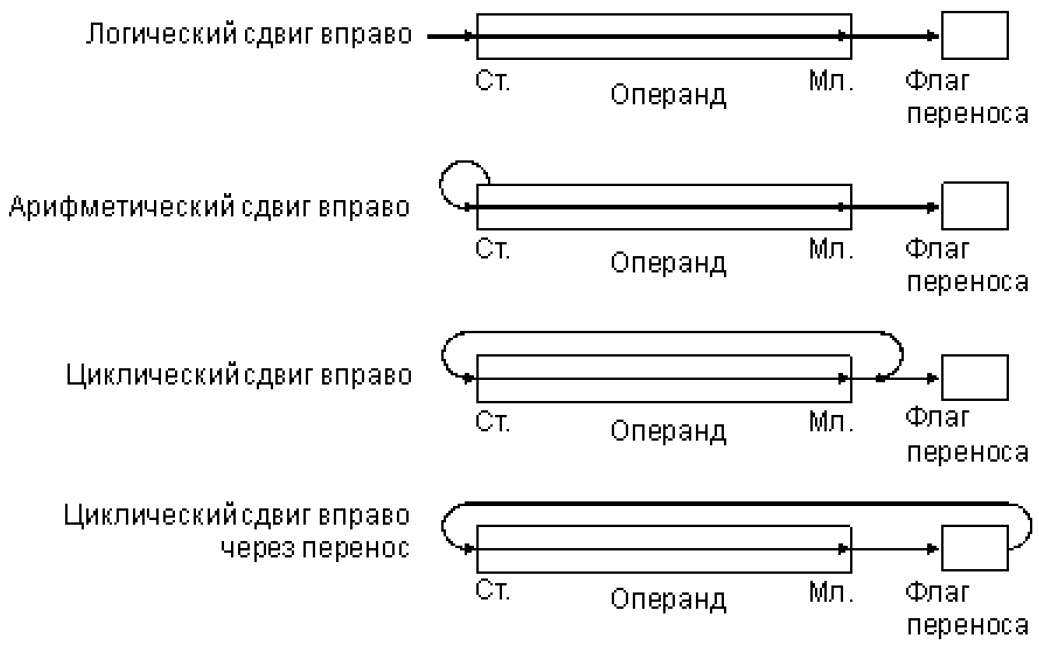

Команды сдвигов позволяют побитно сдвигать код операнда вправо (в сторону младших разрядов) или влево (в сторону старших разрядов). Тип сдвига (логический, арифметический или циклический) определяет, каково будет новое значение старшего бита (при сдвиге вправо) или младшего бита (при сдвиге влево), а также определяет, будет ли где-то сохранено прежнее значение старшего бита (при сдвиге влево) или младшего бита (при сдвиге вправо). Например, при логическом сдвиге вправо в старшем разряде кода операнда устанавливается нуль, а младший разряд записывается в качестве флага переноса в регистр состояния процессора. А при арифметическом сдвиге вправо значение старшего разряда сохраняется прежним (нулем или единицей), младший разряд также записывается в качестве флага переноса.

Циклические сдвиги позволяют сдвигать биты кода операнда по кругу (по часовой стрелке при сдвиге вправо или против часовой стрелки при сдвиге влево). При этом в кольцо сдвига может входить или не входить флаг переноса. В бит флага переноса (если он используется) записывается значение старшего бита при циклическом сдвиге влево и младшего бита при циклическом сдвиге вправо. Соответственно, значение бита флага переноса будет переписываться в младший разряд при циклическом сдвиге влево и в старший разряд при циклическом сдвиге вправо.

Для примера на рис. 2.3 показаны действия, выполняемые командами сдвигов вправо.

Команды проверки битов и операндов предназначены для установки или очистки битов регистра состояния процессора в зависимости от значения выбранных битов или всего операнда в целом. Выходного операнда команды не формируют. Команда проверки операнда (TST) проверяет весь код операнда в целом на равенство нулю и на знак (на значение старшего бита), она требует только одного входного операнда. Команда проверки бита (BIT) проверяет только отдельные биты, для выбора которых в качестве второго операнда используется код маски. В коде маски проверяемым битам основного операнда должны соответствовать единичные разряды.

Рис. 2.3. Команды сдвигов вправо.

Наконец, команды установки и очистки битов регистра состояния процессора (то есть флагов) позволяют установить или очистить любой флаг, что бывает очень удобно. Каждому флагу обычно соответствуют две команды, одна из которых устанавливает его в единицу, а другая сбрасывает в нуль. Например, флагу переноса C (от Carry) будут соответствовать команды CLC (очистка) и SEC или STC (установка).