- •Основные понятия и определения. Лекция №1. Микропроцессоры и микроконтроллеры. Общие сведения. Шина адреса, шина управления.

- •Что такое микропроцессор?

- •Шинная структура связей

- •Лекция №2. Архитектура микропроцессоров и микроконтроллеров. Risc и cisc система команд в мп и мк. Архитектура микропроцессорных систем

- •Типы микропроцессорных систем

- •Risc и cisc система команд в мп и мк

- •Команды пересылки данных

- •Арифметические команды

- •Логические команды

- •Команды переходов

- •Лекция №3. Внутренняя организация процессора. Назначение и функциональные особенности блоков. Быстродействие процессора

- •Классификация и структура

- •Процессорное ядро

- •Функции процессора

- •Лекция №4. Последовательность выполнения команд микропроцессором. Режимы адресации.

- •Адресация операндов

- •Методы адресации

- •Адресация байтов и слов

- •Регистры процессора

- •Система команд мп. Лекция №5. Архитектура изучаемого микроконтроллера. Назначение внутренних блоков. Микроконтроллеры семейства avr

- •Микроконтроллер aTtiny2313 фирмы Atmel

- •Архитектура микроконтроллеров семейства Tiny

- •Организация памяти

- •Память программ

- •Память данных

- •Способы адресации памяти данных

- •Прямая адресация

- •Лекция №6. Блок регистров общего назначения. Команды с непосредственной адресацией. Различные режимы адресации. Энергонезависимая память данных (eeprom)

- •Доступ к eeprom

- •Меры предосторожности

- •Счетчик команд и выполнение программы

- •Лекция №7. Система команд изучаемого микроконтроллера.

- •Лекция №8. Команды переходов и сдвига. Остальные команды.

- •Выводы микроконтроллера. Лекция №9. Описание выводов микроконтроллера.

- •Описание выводов

- •Кварцевый генератор

- •Лекция №10. Пространство ввода/вывода микроконтроллера.

- •Порт ввода/вывода в

- •Регистр направления данных порта b - ddrb

- •Альтернативные функции portb

- •Порт ввода/вывода d

- •Регистр направления данных порта b - ddrb

- •Порт d, как порт ввода/вывода общего назначения

- •Альтернативные функции порта d

- •Регистры и обработка прерываний микроконтроллера. Лекция №13. Регистр состояния и указатель стека микроконтроллера.

- •Регистр состояния - sreg

- •Указатель стека sp

- •Лекция №14. Обработка внешних прерываний в микроконтроллере.

- •Обработка внешних прерываний. Общий регистр маски прерываний gimsk

- •Общий регистр флагов прерываний

- •Регистр управления микроконтроллером - mcucr

- •Лекция №15. Обработка прерываний от таймеров/счетчиков в микроконтроллере.

- •Регистр маски прерывания от таймера/счетчика - timsk

- •Регистр флагов прерываний от таймеров/счетчиков - tifr

- •Прерывания в микроконтроллере. Лекция №16. Определитель таймеров/счетчиков. Принцип работы таймера/счетчика 0.

- •Определитель таймеров/счетчиков

- •Регистр управления таймером/счетчиком 0 - tccr0

- •Лекция №17. Режимы работы таймера/счетчика 1.

- •Регистр a управления таймером/счетчиком 1 - tccr1a

- •Таймер/счетчик 1 - tcnt1h и tcnt1l

- •Регистр совпадения a таймера/счетчика 1 - ocr1ah и ocr1al

- •Регистр захвата таймера/счетчика 1 - icr1h и icr1l

- •Таймер/счетчик в режиме шим

- •Лекция №18. Универсальный асинхронный приемо-передатчик. Принцип работы и управления.

- •Передача данных

- •Прием данных

- •Управление uart регистр ввода/вывода uart

- •Регистр состояния uart (usr)

- •Регистр управления uart (ucr)

- •Генератор скорости передачи

- •Лекция №19. Аналоговый компаратор и сторожевой таймер микроконтроллера.

- •Аналоговый компаратор регистр управления и состояния аналогового компаратора (acsr).

- •Регистр управления сторожевым таймером - wdtcr

- •Форматы представления чисел в эвм. Лекция №20. Формат чисел с фиксированной точкой и элементарные операции над ними.

- •Компьютерное представление целых чисел

- •Лекция №21. Формат чисел с плавающей точкой и элементарные операции над ними.

- •Компьютерное представление вещественных чисел

- •Цифро-аналоговые преобразователи. Лекция №22. Основные понятия и определения цифро-аналоговых преобразователей (цап). Виды погрешностей преобразования.

- •Параметры цап

- •Лекция №23. Цап на взвешивающей матрице и на матрице r-2r. Принцип работы. Достоинства и недостатки. Цап на взвешивающей матрице

- •Цап на матрице r-2r

Прерывания в микроконтроллере. Лекция №16. Определитель таймеров/счетчиков. Принцип работы таймера/счетчика 0.

Помимо внешних сигналов прерывания микроконтроллер имеет множество внутренних сигналов от встроенных устройств. Одним из основных встроенных устройств является блок таймеров/счетчиков.

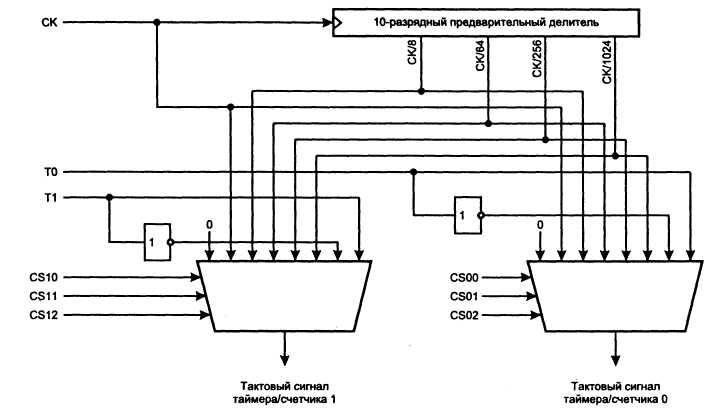

Определитель таймеров/счетчиков

В AT90S2313 предусмотрены два таймера/счетчика общего назначения. 8-разрядный и 16-разрядный. Каждый из таймеров индивидуально подключается к одному из выходов 10-разрядного предварительного делителя частоты. Оба таймера могут использоваться как таймеры с внутренним источником импульсов или счетчики импульсов поступающих извне.

В качестве источника импульсов для таймеров можно выбрать сигнал с тактовой частотой процессора (CK), импульсы предварительного делителя (CK/8, CK/64, CK/256 или CK/1024) или импульсы с соответствующего внешнего вывода. Кроме того, таймеры могут быть остановлены, запретом прохождения импульсов на них.

Рис.16.1. Структурная схема предварительного делителя тактовой частоты для таймеров/счетчиков.

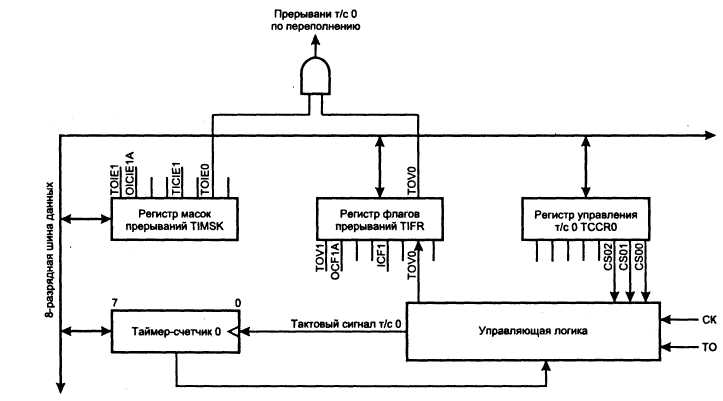

8-РАЗРЯДНЫЙ ТАЙМЕР/СЧЕТЧИК 0

8-разрядный таймер/счетчик может получать импульсы тактовой частоты - CK, импульсы с предварительного делителя (CK/8, CK/64, CK/256 или CK/1024), импульсы с внешнего вывода или быть остановлен соответствующими установками регистра TCCR0. Флаг переполнения таймера находится в регистре TIFR. Биты управления таймером расположены в регистре TCCR0. Разрешение и запрещение прерываний от таймера управляется регистром TIMSK.

При работе таймера/счетчика от внешнего сигнала, внешний сигнал синхронизируется с тактовым генератором ЦПУ. Для правильной обработки внешнего сигнала, минимальное время между соседними импульсами должно превышать период тактовой частоты процессора. Сигнал внешнего источника обрабатывается по спадающему фронту тактовой частоты процессора.

8-разрядный таймер/счетчик можно использовать как счетчик с высоким разрешением, так и для точных применений с низким коэффициентом деления тактовой частоты. Более высокие коэффициенты деления можно использовать для медленных функций или измерения временных интервалов между редкими событиями.

Рис.16.2. Структурная схема таймера/счетчика 0.

Регистр управления таймером/счетчиком 0 - tccr0

Бит 7 6 5 4 3 2 1 0

┌───┬───┬───┬───┬───┬────┬────┬────┐

$33($53)│ - │ - │ - │ - │ - │CS02│CS01│CS00│ TCCR0

└───┴───┴───┴───┴───┴────┴────┴────┘

Чт./зап.(R/W) R R R R R R/W R/W R/W

Начальн.знач. 0 0 0 0 0 0 0 0

Биты 7..3 - зарезервированы. В AT90S2313 эты биты зарезервированы и всегда читаются как 0.

Биты 2,1,0 - CS02, CS01, CS00 - выбор тактовой частоты. Эти биты задают коэффициент деления предварительного делителя.

CS02 |

CS01 |

CS00 |

Описание |

0 |

0 |

0 |

Таймер/счетчик остановлен |

0 |

0 |

1 |

CK |

0 |

1 |

0 |

CK/8 |

0 |

1 |

1 |

CK/64 |

1 |

0 |

0 |

CK/256 |

1 |

0 |

1 |

CK/1024 |

1 |

1 |

0 |

Внешний вывод T0, нарастающий фронт |

1 |

1 |

1 |

Внешний вывод T0, спадающий фронт |

Таблица 16.1. Выбор коэффициента предварительного деления

Условие Stop запрещает/разрешает функционирование таймера/счетчика. В режимах деления используется частота тактового генератора. При использовании работы от внешнего источника предварительно должен быть установлен соответствующий бит регистра направления данных (0 - включает ножку на ввод).

ТАЙМЕР/СЧЕТЧИК 0 - TCNT0.

Бит 7 6 5 4 3 2 1 0

┌───┬───┬───┬───┬───┬───┬───┬───┐

$32($52) │MSB│ - │ - │ - │ - │ - │ - │LSB│ TCNT0

└───┴───┴───┴───┴───┴───┴───┴───┘

Чт./зап.(R/W) R/W R/W R/W R/W R/W R/W R/W R/W

Начальн.знач. 0 0 0 0 0 0 0 0

Таймер/счетчик реализован как нарастающий счетчик с возможностью чтения и записи. При записи таймера/счетчика, если присутствуют тактовые импульсы, таймер/счетчик продолжает счет в следующем за операцией записи тактовом цикле таймера.