- •Основные понятия и определения. Лекция №1. Микропроцессоры и микроконтроллеры. Общие сведения. Шина адреса, шина управления.

- •Что такое микропроцессор?

- •Шинная структура связей

- •Лекция №2. Архитектура микропроцессоров и микроконтроллеров. Risc и cisc система команд в мп и мк. Архитектура микропроцессорных систем

- •Типы микропроцессорных систем

- •Risc и cisc система команд в мп и мк

- •Команды пересылки данных

- •Арифметические команды

- •Логические команды

- •Команды переходов

- •Лекция №3. Внутренняя организация процессора. Назначение и функциональные особенности блоков. Быстродействие процессора

- •Классификация и структура

- •Процессорное ядро

- •Функции процессора

- •Лекция №4. Последовательность выполнения команд микропроцессором. Режимы адресации.

- •Адресация операндов

- •Методы адресации

- •Адресация байтов и слов

- •Регистры процессора

- •Система команд мп. Лекция №5. Архитектура изучаемого микроконтроллера. Назначение внутренних блоков. Микроконтроллеры семейства avr

- •Микроконтроллер aTtiny2313 фирмы Atmel

- •Архитектура микроконтроллеров семейства Tiny

- •Организация памяти

- •Память программ

- •Память данных

- •Способы адресации памяти данных

- •Прямая адресация

- •Лекция №6. Блок регистров общего назначения. Команды с непосредственной адресацией. Различные режимы адресации. Энергонезависимая память данных (eeprom)

- •Доступ к eeprom

- •Меры предосторожности

- •Счетчик команд и выполнение программы

- •Лекция №7. Система команд изучаемого микроконтроллера.

- •Лекция №8. Команды переходов и сдвига. Остальные команды.

- •Выводы микроконтроллера. Лекция №9. Описание выводов микроконтроллера.

- •Описание выводов

- •Кварцевый генератор

- •Лекция №10. Пространство ввода/вывода микроконтроллера.

- •Порт ввода/вывода в

- •Регистр направления данных порта b - ddrb

- •Альтернативные функции portb

- •Порт ввода/вывода d

- •Регистр направления данных порта b - ddrb

- •Порт d, как порт ввода/вывода общего назначения

- •Альтернативные функции порта d

- •Регистры и обработка прерываний микроконтроллера. Лекция №13. Регистр состояния и указатель стека микроконтроллера.

- •Регистр состояния - sreg

- •Указатель стека sp

- •Лекция №14. Обработка внешних прерываний в микроконтроллере.

- •Обработка внешних прерываний. Общий регистр маски прерываний gimsk

- •Общий регистр флагов прерываний

- •Регистр управления микроконтроллером - mcucr

- •Лекция №15. Обработка прерываний от таймеров/счетчиков в микроконтроллере.

- •Регистр маски прерывания от таймера/счетчика - timsk

- •Регистр флагов прерываний от таймеров/счетчиков - tifr

- •Прерывания в микроконтроллере. Лекция №16. Определитель таймеров/счетчиков. Принцип работы таймера/счетчика 0.

- •Определитель таймеров/счетчиков

- •Регистр управления таймером/счетчиком 0 - tccr0

- •Лекция №17. Режимы работы таймера/счетчика 1.

- •Регистр a управления таймером/счетчиком 1 - tccr1a

- •Таймер/счетчик 1 - tcnt1h и tcnt1l

- •Регистр совпадения a таймера/счетчика 1 - ocr1ah и ocr1al

- •Регистр захвата таймера/счетчика 1 - icr1h и icr1l

- •Таймер/счетчик в режиме шим

- •Лекция №18. Универсальный асинхронный приемо-передатчик. Принцип работы и управления.

- •Передача данных

- •Прием данных

- •Управление uart регистр ввода/вывода uart

- •Регистр состояния uart (usr)

- •Регистр управления uart (ucr)

- •Генератор скорости передачи

- •Лекция №19. Аналоговый компаратор и сторожевой таймер микроконтроллера.

- •Аналоговый компаратор регистр управления и состояния аналогового компаратора (acsr).

- •Регистр управления сторожевым таймером - wdtcr

- •Форматы представления чисел в эвм. Лекция №20. Формат чисел с фиксированной точкой и элементарные операции над ними.

- •Компьютерное представление целых чисел

- •Лекция №21. Формат чисел с плавающей точкой и элементарные операции над ними.

- •Компьютерное представление вещественных чисел

- •Цифро-аналоговые преобразователи. Лекция №22. Основные понятия и определения цифро-аналоговых преобразователей (цап). Виды погрешностей преобразования.

- •Параметры цап

- •Лекция №23. Цап на взвешивающей матрице и на матрице r-2r. Принцип работы. Достоинства и недостатки. Цап на взвешивающей матрице

- •Цап на матрице r-2r

Лекция №6. Блок регистров общего назначения. Команды с непосредственной адресацией. Различные режимы адресации. Энергонезависимая память данных (eeprom)

EEPROM (англ. Electrically Erasable Programmable Read-Only Memory) — электрически стираемое перепрограммируемое ПЗУ (ЭСППЗУ), один из видов энергонезависимой памяти. Память такого типа может стираться и заполняться данными до миллиона раз.

Как уже было сказано, некоторые микроконтроллеры семейства Tiny (ATtiny12x и ATtiny15L) имеют в своем составе энергонезависимую память данных (EEPROM-память). Эта память расположена в собственном адресном пространстве, а ее объем составляет 64 байта.

Доступ к eeprom

Для обращения к EEPROM-памяти используются три регистра ввода/вывода: регистр адреса, регистр данных и регистр управления.

Регистр адреса

Регистр адреса EEPROM-памяти EEAR (EEPROM Address Register) расположен по адресу $1E. В этот регистр загружается адрес ячейки, к которой будет производиться обращение. Регистр адреса доступен как для записи, так и для чтения. Поскольку для адресации 64_х ячеек достаточно 6_разрядного адреса, содержимое двух старших разрядов регистра EEAR игнорируется.

Регистр данных

Регистр данных EEPROM-памяти EEDR (EEPROM Data Register) расположен по адресу $1D. При записи в этот регистр загружаются данные, которые должны быть помещены в EEPROM, а при чтении в этот регистр помещаются данные, считанные из EEPROM.

Регистр управления

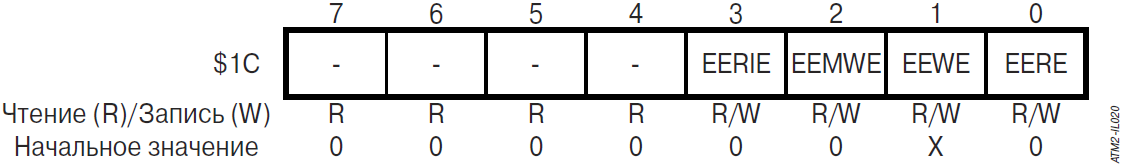

Регистр управления EEPROM-памяти EECR (EEPROM Control Register) расположен по адресу $1C. Как следует из названия, данный регистр используется для управления доступом к EEPROM-памяти. Формат этого регистра показано на Рис. 5.9, а его описание приведено в Табл. 6.1.

Рис. 6.1. Формат регистра EECR

Разряд |

Название |

Описание |

7…4 |

— |

Не используются, читаются как «0» |

3 |

EERIE |

Разрешение прерывания от EEPROM. Данный разряд управляет генерацией прерывания, возникающего при завершении цикла записи в EEPROM. Если этот разряд установлен в «1», прерывания разрешены (если флаг I регистра SREG также установлен в «1»). При сброшенном разряде EEWE прерывание генерируется постоянно |

2 |

EEMWE |

Управление разрешением записи в EEPROM. Состояние этого разряда определяет функционирование флага разрешения записи EEWE. Если данный разряд установлен в «1», то при записи в разряд EEWE «1» происходит запись данных в EEPROM. В противном случае установка EEWE в «1» не производит никакого эффекта. После программной установки этот разряд сбрасывается аппаратно через 4 машинных цикла |

1 |

EEWE |

Разрешение записи в EEPROM. При установке этого разряда в «1» происходит запись данных в EEPROM (если EEMWE равен «1») |

0 |

EERE |

Разрешение чтения из EEPROM. После установки этого разряда в «1» выполняется чтение данных из EEPROM. По окончании чтения этот разряд сбрасывается аппаратно |

Таблица 6.1. Разряды регистра EECR

Таким образом, процедура записи одного байта в EEPROM-память состоит из следующих этапов:

дождаться готовности EEPROM к записи данных (ждать пока не сбросится флаг EEWE (EEPROM Write Enable) регистра EECR);

загрузить байт данных в регистр EEDR, а требуемый адрес — в регистр EEAR;

установить в «1» флаг EEMWE (EEPROM Memory Write Enable) регистра EECR;

в течение 4-х машинных циклов после установки флага EEMWE записать «1» в разряд EEWE регистра EECR.

Длительность цикла записи зависит от частоты внутреннего RC-генератора (от значения калибровочной константы) и составляет 3.1…6.8 мс для моделей ATtiny12x и 4.6…8.2 мс для модели ATtiny15L. По окончании цикла записи разряд EEWE аппаратно сбрасывается, после чего программа может начать запись следующего байта. Следует также помнить, что после установки разряда EEWE в «1», процессор пропускает 2 машинных цикла перед выполнением следующей инструкции.

При записи в EEPROM могут возникнуть некоторые проблемы, вызванные прерываниями. При возникновении прерывания между 3-м и 4-м этапами описанной последовательности запись в EEPROM будет сорвана, т. к. за время обработки прерывания флаг EEMWE сбросится в «0». Если в подпрограмме обработки прерывания, возникшего во время записи в EEPROM-память, также происходит обращение к ней, то будет изменено содержимое регистров адреса и данных EEPROM. В результате первая запись (прерванная) будет сорвана.

Для избежания описанных проблем настоятельно рекомендуется запрещать все прерывания (сбрасывать бит I регистра SREG) при выполнении пунктов 2…4 описанной выше последовательности.

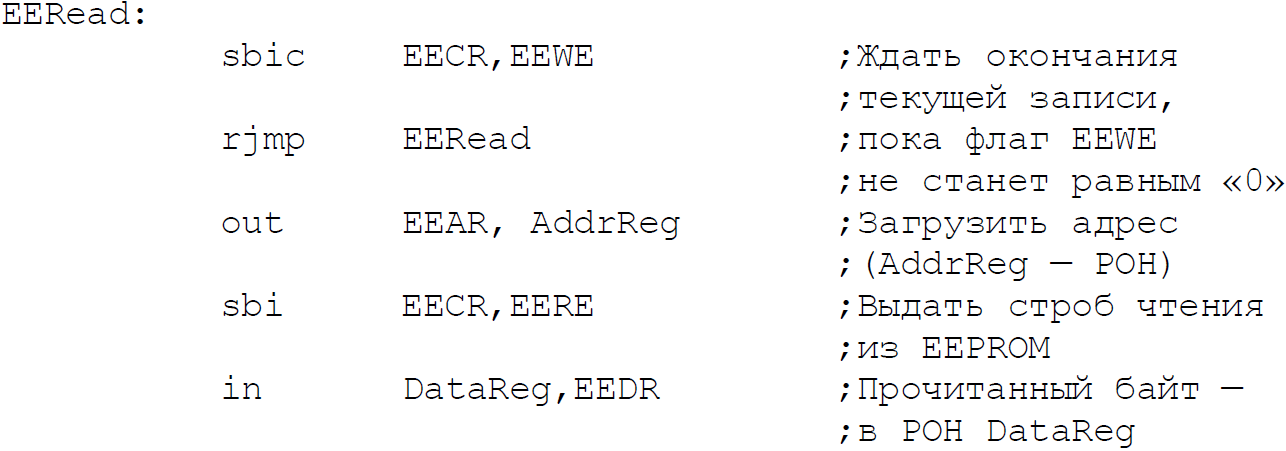

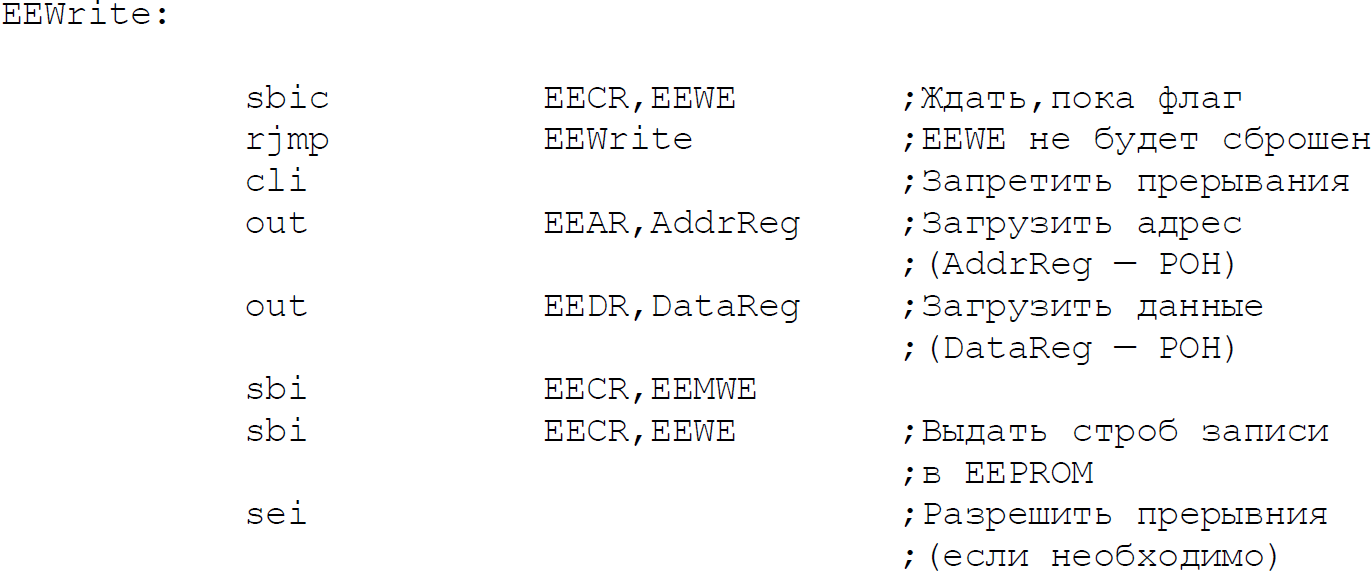

С учетом сказанного фрагмент программы, осуществляющий запись в EEPROM, выглядит следующим образом:

Процедура чтения данных из EEPROM гораздо проще, чем процедура записи. После загрузки требуемого адреса в регистр EEAR, программа должна установить разряд EERE регистра EECR в «1». Когда запрошенные данные будут находиться в регистре данных EEDR, произойдет аппаратный сброс этого разряда.

Операция чтения из EEPROM всегда выполняется за один машинный цикл. Кроме того, после установки разряда EERE в «1» процессор пропускает 4 машинных цикла перед началом выполнения следующей инструкции. Поэтому следить в программе за состоянием разряда EERE нет никакой необходимости.

Единственное, на что нужно обратить внимание при чтении из EEPROM, это состояние флага EEWE. Перед выполнением чтения необходимо убедиться, что этот флаг сброшен. В противном случае в результате загрузки в регистры новых значений адреса и данных во время записи в EEPROM процедура записи будет прервана, а результат этой записи не определен.

С учетом сказанного фрагмент программы, осуществляющий чтение из EEPROM, выглядит следующим образом: