- •Основные понятия и определения. Лекция №1. Микропроцессоры и микроконтроллеры. Общие сведения. Шина адреса, шина управления.

- •Что такое микропроцессор?

- •Шинная структура связей

- •Лекция №2. Архитектура микропроцессоров и микроконтроллеров. Risc и cisc система команд в мп и мк. Архитектура микропроцессорных систем

- •Типы микропроцессорных систем

- •Risc и cisc система команд в мп и мк

- •Команды пересылки данных

- •Арифметические команды

- •Логические команды

- •Команды переходов

- •Лекция №3. Внутренняя организация процессора. Назначение и функциональные особенности блоков. Быстродействие процессора

- •Классификация и структура

- •Процессорное ядро

- •Функции процессора

- •Лекция №4. Последовательность выполнения команд микропроцессором. Режимы адресации.

- •Адресация операндов

- •Методы адресации

- •Адресация байтов и слов

- •Регистры процессора

- •Система команд мп. Лекция №5. Архитектура изучаемого микроконтроллера. Назначение внутренних блоков. Микроконтроллеры семейства avr

- •Микроконтроллер aTtiny2313 фирмы Atmel

- •Архитектура микроконтроллеров семейства Tiny

- •Организация памяти

- •Память программ

- •Память данных

- •Способы адресации памяти данных

- •Прямая адресация

- •Лекция №6. Блок регистров общего назначения. Команды с непосредственной адресацией. Различные режимы адресации. Энергонезависимая память данных (eeprom)

- •Доступ к eeprom

- •Меры предосторожности

- •Счетчик команд и выполнение программы

- •Лекция №7. Система команд изучаемого микроконтроллера.

- •Лекция №8. Команды переходов и сдвига. Остальные команды.

- •Выводы микроконтроллера. Лекция №9. Описание выводов микроконтроллера.

- •Описание выводов

- •Кварцевый генератор

- •Лекция №10. Пространство ввода/вывода микроконтроллера.

- •Порт ввода/вывода в

- •Регистр направления данных порта b - ddrb

- •Альтернативные функции portb

- •Порт ввода/вывода d

- •Регистр направления данных порта b - ddrb

- •Порт d, как порт ввода/вывода общего назначения

- •Альтернативные функции порта d

- •Регистры и обработка прерываний микроконтроллера. Лекция №13. Регистр состояния и указатель стека микроконтроллера.

- •Регистр состояния - sreg

- •Указатель стека sp

- •Лекция №14. Обработка внешних прерываний в микроконтроллере.

- •Обработка внешних прерываний. Общий регистр маски прерываний gimsk

- •Общий регистр флагов прерываний

- •Регистр управления микроконтроллером - mcucr

- •Лекция №15. Обработка прерываний от таймеров/счетчиков в микроконтроллере.

- •Регистр маски прерывания от таймера/счетчика - timsk

- •Регистр флагов прерываний от таймеров/счетчиков - tifr

- •Прерывания в микроконтроллере. Лекция №16. Определитель таймеров/счетчиков. Принцип работы таймера/счетчика 0.

- •Определитель таймеров/счетчиков

- •Регистр управления таймером/счетчиком 0 - tccr0

- •Лекция №17. Режимы работы таймера/счетчика 1.

- •Регистр a управления таймером/счетчиком 1 - tccr1a

- •Таймер/счетчик 1 - tcnt1h и tcnt1l

- •Регистр совпадения a таймера/счетчика 1 - ocr1ah и ocr1al

- •Регистр захвата таймера/счетчика 1 - icr1h и icr1l

- •Таймер/счетчик в режиме шим

- •Лекция №18. Универсальный асинхронный приемо-передатчик. Принцип работы и управления.

- •Передача данных

- •Прием данных

- •Управление uart регистр ввода/вывода uart

- •Регистр состояния uart (usr)

- •Регистр управления uart (ucr)

- •Генератор скорости передачи

- •Лекция №19. Аналоговый компаратор и сторожевой таймер микроконтроллера.

- •Аналоговый компаратор регистр управления и состояния аналогового компаратора (acsr).

- •Регистр управления сторожевым таймером - wdtcr

- •Форматы представления чисел в эвм. Лекция №20. Формат чисел с фиксированной точкой и элементарные операции над ними.

- •Компьютерное представление целых чисел

- •Лекция №21. Формат чисел с плавающей точкой и элементарные операции над ними.

- •Компьютерное представление вещественных чисел

- •Цифро-аналоговые преобразователи. Лекция №22. Основные понятия и определения цифро-аналоговых преобразователей (цап). Виды погрешностей преобразования.

- •Параметры цап

- •Лекция №23. Цап на взвешивающей матрице и на матрице r-2r. Принцип работы. Достоинства и недостатки. Цап на взвешивающей матрице

- •Цап на матрице r-2r

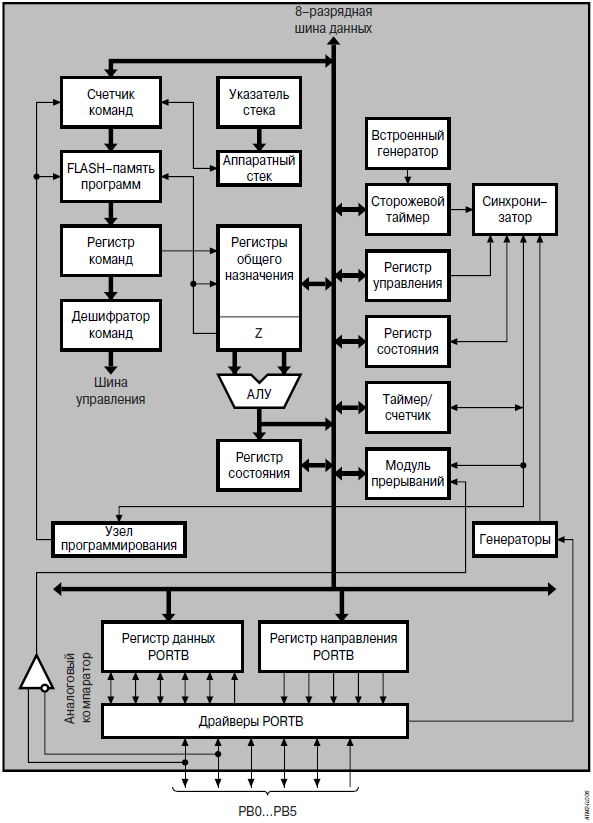

Архитектура микроконтроллеров семейства Tiny

Микроконтроллеры AVR семейства Tiny являются 8-разрядными микроконтроллерами с RISC-архитектурой. Они имеют электрически стираемую FLASH-память программ (ряд моделей имеет также энергонезависимую EEPROM-память данных), а также разнообразные периферийные устройства. Состав этих устройств меняется от модели к модели, более того, одно и то же устройство в разных моделях использует различные ресурсы микроконтроллера (в частности, различные выводы). В то же время некоторые периферийные устройства присутствуют во всех микроконтроллерах семейства: сторожевой таймер, аналоговый компаратор, 8-разрядный таймер/счетчик реального времени и, естественно, порты ввода/вывода.

EEPROM (англ. Electrically Erasable Programmable Read-Only Memory) — электрически стираемое перепрограммируемое ПЗУ (ЭСППЗУ), один из видов энергонезависимой памяти. Память такого типа может стираться и заполняться данными до миллиона раз.

На Рис. 5.2 приведена структурная схема микроконтроллера ATtiny11/11L. Его отличительные особенности:

6-разрядный порт ввода/вывода;

3-уровневый аппаратный стек;

встроенный тактовый RC-генератор;

возможность подключения внешнего резонатора;

использование тактового генератора сторожевого таймера в качестве системного (только ATtiny11x).

Рис. 5.2. Структурная схема микроконтроллеров ATtiny11/11L

Рис. 5.3. Структурная схема микроконтроллера ATtiny15L

Структурная схема микроконтроллера ATtiny15L приведена на Рис. 5.3. Его отличительные особенности:

EEPROM-память данных объемом 64 байт;

6-разрядный порт ввода/вывода;

возможность работы только от встроенного тактового RC-генератора;

два 8-разрядных таймера/счетчика;

4-канальный АЦП.

Организация памяти

Организация памяти микроконтроллеров AVR семейства Tiny выполнена по схеме Гарвардского типа, в которой разделены не только адресные пространства памяти программ и памяти данных, но также и шины доступа к ним. Память данных состоит из двух областей: регистровая память и память на основе EEPROM. Каждая область расположена в своем адресном пространстве.

Обобщенная карта памяти микроконтроллеров AVR семейства Tiny приведена на Рис. 5.4.

Рис. 5.4. Карта памяти микроконтроллеров семейства Tiny

Обратите внимание на следующие моменты. Поскольку микроконтроллеры AVR имеют 16-разрядную систему команд, объем памяти программ на рисунке указан не в байтах, а в 16-битных словах. Символ «$» перед числом означает, что это число записано в шестнадцатеричной системе счисления.

Память программ

Как следует из названия, память программ предназначена для хранения команд, управляющих функционированием микроконтроллера. В памяти программ хранятся также различные константы, не меняющиеся во время работы программы. Как уже было сказано, память программ представляет собой электрически стираемое ППЗУ (FLASH_ПЗУ). Поскольку все команды занимают в памяти по 16 бит, память программ имеет 16-разрядную организацию. Соответственно объем памяти микроконтроллеров семейства составляет 512…1024 16-битных слова.

Для адресации памяти программ используется счетчик команд (PC—Program Counter). Размер счетчика команд составляет 9 или 10 разрядов в зависимости от объема адресуемой памяти.

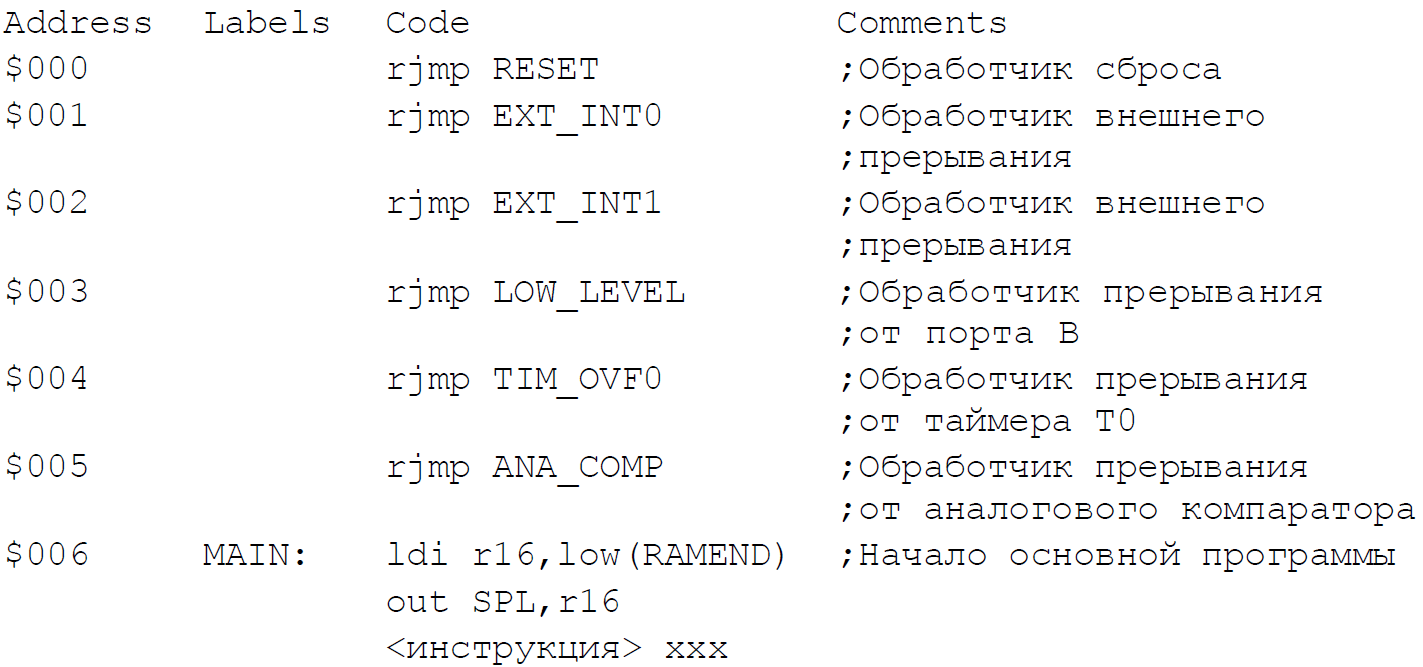

По адресу $000 памяти программ находится вектор сброса. После инициализации (сброса) микроконтроллера выполнение программы начинается с этого адреса (по этому адресу рекомендуется размещать команду относительного перехода к инициализационной части программы). Начиная с адреса $001 располагается таблица векторов прерываний. Размер этой области зависит от модели микроконтроллера и составляет от 4 (адреса $001…$004) до 8 (адреса $001…$008) векторов.

При возникновении прерывания после сохранения в стеке текущего значения счетчика команд происходит выполнение команды, расположенной по адресу соответствующего вектора. Поэтому по этим адресам располагаются команды относительного перехода к подпрограммам обработки прерываний. Ниже приведен типичный листинг начала программы для модели ATtiny28:

Если в программе прерывания не используются (запрещены), то основная программа может начинаться непосредственно с адреса $001.

Следует отметить, что память программ может использоваться не только для хранения кода программы, но также и для хранения различных констант. Для пересылки байта из памяти программ в память данных имеется специальная команда — LPM Rd, Z. Адрес, по которому производится чтение, перед использованием этой команды должен быть загружен в индексный регистр Z (см. далее). При этом старшие 15 разрядов содержимого регистра будут определять адрес слова, а младший разряд будет определять, какой из байтов будет прочитан: «0» — младший байт, «1» — старший байт (Рис. 5.5).

Рис. 5.5. Косвенная адресация памяти программ

В заключение следует отметить, что FLASH-ПЗУ, используемое в микроконтроллерах AVR, рассчитано как минимум на 1000 циклов стирания/записи.