- •7 Форма представления чисел с фиксированной точкой

- •8 Форма представления чисел с плавающей точкой

- •9 Форматы двоично-десятичных чисел

- •10. Машинные коды

- •Прямой код

- •Обратный код

- •. Дополнительный код

- •11 Составные части компьютера

- •12 Логические элементы

- •13. Триггеры

- •2.12.2. Асинхронный rs-триггер

- •2.12.3. Синхронный rs-триггер

- •2.12.3. Двухтактный rs-триггер

- •14 Асинхронный и синхронный d-триггеры

- •17. Дешифраторы

- •18 Одноразрядный сумматор

- •Полусумматор

- •19. Многоразрядные сумматоры

- •20 Двоично-десятичные сумматоры

- •21 Мультиплексоры

- •22. Демультиплексоры

- •23. Регистры

- •24 Счетчики

- •25 Двоично-десятичные счетчики

- •26 Классификация архитектур системы команд

- •27 Классификация по составу и сложности команд

- •28 Классификация по месту хранения операндов

- •29 Архитектура с выделенным доступом к памяти

- •30 Типы команд

- •Команды пересылки данных

- •Операции с целыми числами

- •Операции с числами в форме с плавающей запятой

- •Логические операции

- •Операции сдвигов

- •Операции с десятичными числами

- •Simd-команды

- •Команды для работы со строками

- •Команды преобразования

- •Команды ввода/вывода

- •Команды управления системой

- •Команды управления потоком команд

- •31 Формат команд

- •Длина команды

- •Разрядность полей команды

- •32 Выбор адресности команд

- •33. Способы адресации операндов

- •Непосредственная адресация

- •Прямая адресация

- •Косвенная адресация

- •Регистровая адресация

- •34 Косвенная регистровая адресация

- •Адресация со смещением

- •Относительная адресация

- •35 Базовая регистровая адресация

- •Индексная адресация

- •Страничная адресация

- •Блочная адресация

- •36 Распространенность различных видов адресации

- •Способы адресации в командах управления потоком команд

- •37 Функциональная организация фон-неймановской вычислительной машины

- •38 Устройство управления

- •39 Арифметико-логическое устройство

- •40 Основная память

- •Модуль ввода/вывода

- •41. Стандартный цикл команды

- •42 Организация шин

- •43 Шины «процессор-память»

- •Шина ввода/вывода

- •44 Системная шина

- •45 Иерархия шин

- •46 Арбитраж шин

- •47 Протокол шины

- •48 Методы повышения эффективности шин

- •49 Стандартизация шин

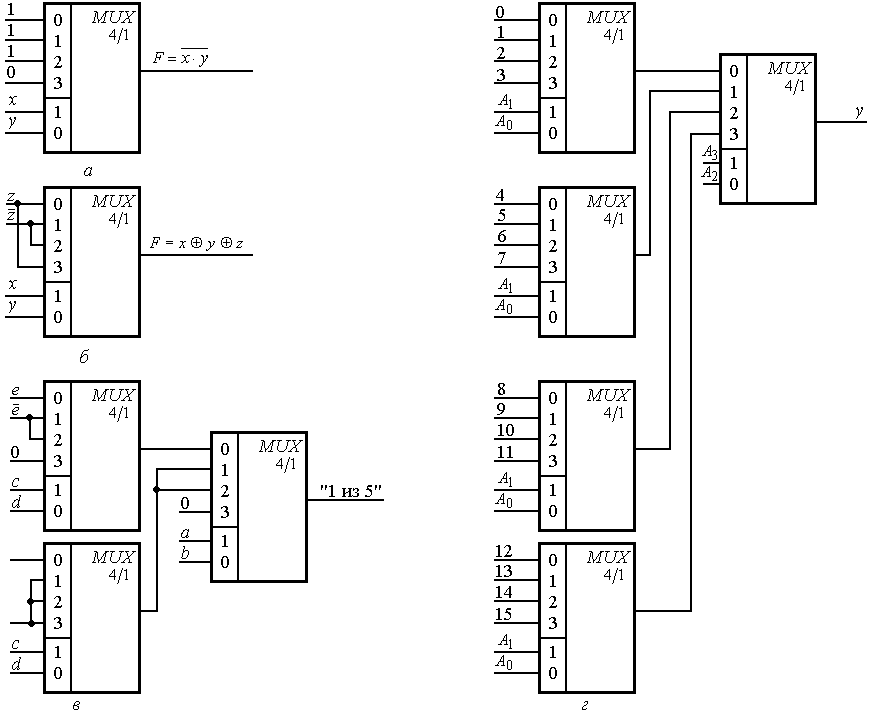

21 Мультиплексоры

Мультиплексор представляет собой комбинационную схему с несколькими входами и одним выходом. Входы мультиплексора делятся на информационные и управляющие (адресные). Мультиплексор передает данные с одного из информационных входов на выход. Номер (адрес) подключаемого входа задается на управляющих входах. Мультиплексор с k управляющими входами может иметь до 2k информационных входов. Для выбора подключаемого входа используется дешифратор. Функциональная схема мультиплексора с двумя управляющими (A0 и A1) и четырьмя информационными (D0 ... D3) входами показаны на рис. 2.31, а. Схема мультиплексора включает в себя дешифратор на два входа и выходную схему. При поступлении адреса A1 A0 на входы дешифратора на одном из его выходов формируется сигнал «1», который подключает вход Di с заданным адресом к выходу схемы. Условное графическое обозначение мультиплексора приведено на рис. 3.24, б.

Рис. 2.31. Мультиплексор:

а – функциональная схема; б – условное графическое обозначение

Используя теорему разложения булевой функции, на мультиплексорах можно реализовать любую логическую функцию. Из мультиплексоров с небольшим числом входов можно построить мультиплексор с необходимым числом входов, используя каскадные схемы (рис. 2.32).

Схема (рис. 2.32, а) реализует таблицу истинности элемента И-НЕ на два входа, так как на входах схемы зафиксированы значения функции И-НЕ, а на адресные входы подаются значения переменных х и у. Для выполнения операции сложения переменных х, y и z по модулю 2 входные сигналы подаются так, как это показано на рис. 2.32, б. Если, например, х = 0, у = 1, z = 0, то на адресные входы поступит адрес «01», будет выбран вход 1, и на выход будет выдан сигнал F = z = 1, т.е. F = x у z = 0 1 0= 1. Если на вход схемы (рис. 2.32, в) подать комбинацию сигналов abcde = 00100, то cd = 10 и, следовательно, на мультиплексорах первого яруса будет выбран вход 2. При этом на вход 0 мультиплексора второго яруса поступит сигнал е, а на входы 1 и 2 – сигнал «0». Так как ab = 00, будет выбран нулевой вход этого мультиплексора. На выходе схемы возникнет сигнал е = 1, т.е. будет обнаружен код, содержащий одну единицу. Пример каскадного мультиплексора на 16 входов приведен на рис. 2.32, г.

Рис. 2.32. Схемы реализации логических функций:

а – функция И-НЕ; б – сложение по модулю 2;

в – выделение наборов пяти переменных, содержащих единицу;

г – каскадный мультиплексор на 16 входов

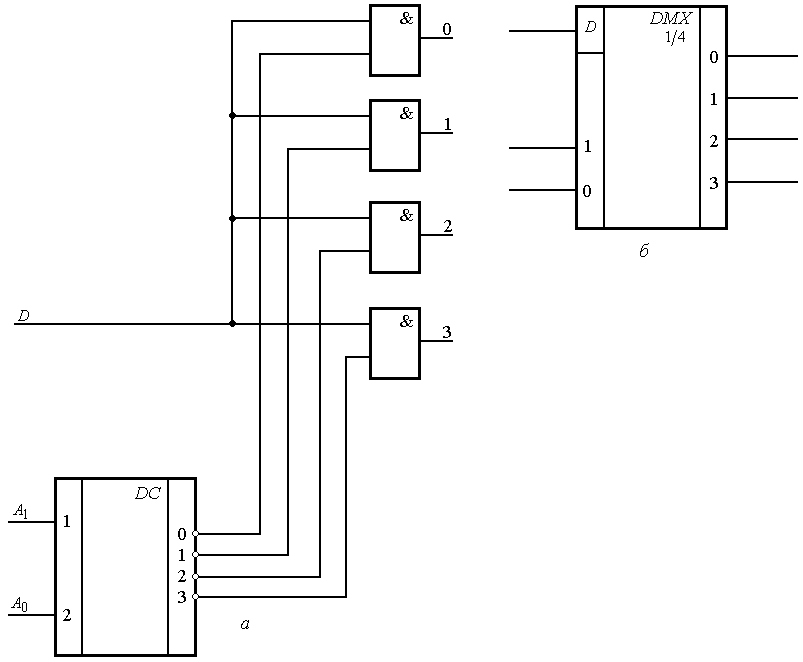

22. Демультиплексоры

Демультиплексор – комбинационная схема с одним информационным входом, несколькими управляющими (адресными) входами и несколькими выходами. Демультиплексор передает сигнал с информационного входа на один из выходов, номер (адрес) которого задается сигналом на адресных входах. Таким образом, демультиплексор выполняет функцию, обратную по отношению к функции мультиплексора. Так как мультиплексор и демультиплексор выполняют функции, связанные с выбором одного из входов или выходов, их называют также селекторами. Максимальное число выходов демультиплексора составляет 2k, где k – число адресных входов. Функциональная схема демультиплексора с четырьмя информационными выходами и его условное графическое обозначение показаны на рис. 2.33. Входной сигнал D подается на входы всех выходных ключей, выполненных на элементах И. На вторые входы ключей поступают сигналы с выхода дешифратора, которые открывают один из ключей и разрешают входному сигналу пройти на выход схемы с заданными адресом.

Рис. 2.33. Демультиплексор:

а – функциональная схема; б – условное графическое обозначение