- •Дослідження методів та інструментальних засобів проектування цифрових пристроїв на основі пліс

- •1. Огляд елементної бази, що застосовується для побудови логічних керуючих автоматів з паралельною архітектурою

- •1.1 Класифікація

- •1.2 Стандартні програмовані логічні пристрої (spld)

- •1.3 Складні програмовані логічні пристрої (cpld)

- •1.4 Матриці елементів гнучкої логіки (flex)

- •1.5 Вентильні матриці, що програмуються користувачем (fpga)

- •1.6 Пліс типу «система на кристалі»

- •2. Аналіз систем автоматизованого проектування логічних керуючих автоматів на основі пліс

- •2.1 Системи автоматизованого проектування фірми Xilinx

- •2.2 Системи автоматизованого проектування фірми Altera

- •2.3 Тенденції розвитку систем автоматизованого проектування логічних керуючих автоматів на основі пліс

- •3. Аналіз мов опису апаратури, що використовуються для моделювання архітектури логічних керуючих автоматів

- •3.1 Загальні відомості про мови опису апаратури

- •3.2 Мова опису апаратури vhdl

- •3.3 Мова опису апаратури ahdl

Дослідження методів та інструментальних засобів проектування цифрових пристроїв на основі пліс

1. Огляд елементної бази, що застосовується для побудови логічних керуючих автоматів з паралельною архітектурою

1.1 Класифікація

Для побудови логічних керуючих автоматів з паралельною архітектурою використовують пристрої з регулярною архітектурою, які представляють собою набір стандартних елементів та вузлів, що інтегровані на одному кристалі. Існує багато різновидів таких пристроїв, але всі вони об’єднуються однією назвою – програмовані логічні інтегральні схеми.

Настроювання ПЛІС на виконання заданих функцій здійснюються користувачем шляхом вільного компонування цих елементів і вузлів програмним способом. Завдяки зазначеним особливостям ПЛІС в останні роки успішно завойовують ринок і в ряді предметних областей становлять гідну конкуренцію мікропроцесорам і мікроконтролерам. Залежно від використовуваної архітектури ПЛІС можуть бути класифіковані таким чином (рис. 1).

Структури ПЛІС мають високий рівень регулярності: основу кристала ПЛІС становить матриця однотипних функціональних вузлів, на базі яких користувач може створювати цілі системи керування складними технологічними об'єктами. Завдяки цьому ПЛІС характеризуються високою швидкодією і надійністю, а також широкими можливостями в частині резервування і діагностики.

Найбільш ефективними областями застосування ПЛІС є:

1. синтез (моделювання) нетрадиційних архітектур керуючих автоматів (навіть якщо надалі планується використання іншої елементної бази);

2. побудова надшвидкодіючих керуючих пристроїв;

3. реалізація автономних систем керування критичного застосування, до яких пред'являються жорсткі вимоги в частині забезпечення надійності, безпеки, електромагнітної сумісності й т.ін.

Рис. 1. Класифікація ПЛІС

1.2 Стандартні програмовані логічні пристрої (spld)

До перших ПЛІС, які з'явилися на початку 70-х років, відносяться програмовані постійні запам'ятовуючі пристрої (ППЗП – Programmable Read Only Memory – PROM). Перший час PROM використовували винятково для зберігання інформації, пізніше їх стали застосовувати для реалізації логічних функцій.

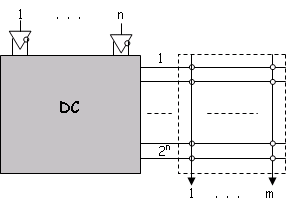

Структура PROM (рис. 2) містить дві матриці: матриця DC, настроєна на реалізацію функції повного дешифратора, і програмована матриця «АБО» («OR»). PROM дозволяє реалізувати логічні функції, представлені в довершеній диз'юнктивній нормальній формі.

Рис. 2. Структура ППЗП – Programmable Read Only Memory

З 1971 р. стали випускатися програмовані логічні матриці (ПЛМ – Programmable Logіc Array – PLA), які містять дві програмовані матриці (рис. 3), одна з яких настроєна на реалізацію функції «І» («AND»), а інша – функції «АБО» («OR»).

Рис. 3. Структура ПЛМ – Programmable Logic Array – PLA

Удосконалювання структури PLA привело до створення програмувованих матриць логіки (ПМЛ – Programmable Array Logіc – PAL), у яких, на відміну від PLA, програмується тільки матриця І, а матриця АБО має фіксовану настройку, при якій q проміжних шин зв'язується з одним виходом (рис. 4). Це дозволяє матрицю АБО реалізувати у вигляді сукупності q-входових дизъюнкторів. Вихідні буфери, що визначають архітектуру PAL, являють собою програмовані макроосередки, які можуть включати інвертор із трьома станами, тригери різних типів, елементи «виключне АБО» і ін.

Рис. 4. Структура ПМЛ – Programmable Array Logic – PAL

Описані вище структури ПЛІС відносяться до стандартних програмованих логічних пристроїв (стандартних ПЛП, Standard Programmable Logіc Devіces, SPLD).