- •Проектирование цифровых устройств на плис

- •Содержание

- •Список сокращений, условных обозначений и терминов

- •Введение

- •1 Обзор существующих пакетов проектирования цу на плис

- •Программные средства фирмы Xilinx

- •1.2 Моделирование цифровых устройств и разработка плис в

- •Системы разработки фирмы Altera

- •2 Система проектирования

- •2.2.2 Создание нового проекта

- •2.2.3 Проектирование цифрового устройства

- •2.2.4 Создание элемента в MegaWizard Plug-In Manager.

- •2.2.5 Создание исходных данных для проектирования устройства.

- •2.2.6 Компиляция проекта

- •2.2.7 Верификация проекта

- •2.2.8 Задание для самостоятельной разработки

- •Общие сведения о языке описания аппаратуры ahdl

- •Элементы языка ahdl

- •Управление синтезом.

- •Использование чисел и констант в языке ahdl

- •Комбинационная логика

- •Описание цифровой схемы на языке ahdl

- •Задание для самостоятельной разработки

2.2.6 Компиляция проекта

Таким образом мы задались входными данными. Теперь можно начать процесс реализации данного устройства на ПЛИС фирмы Altera.

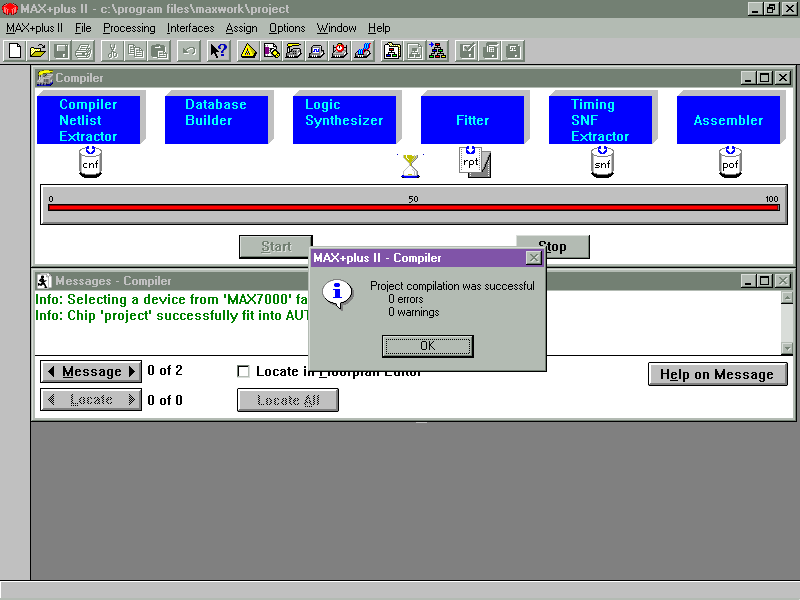

Сначала выполним компиляцию проекта. Для этого выберем на инструментальной панели пиктограмму Compiler. В компиляторе, в меню Processing нужно выбрать пункт Generate AHDL TDO File, чтобы сформировать AHDL описание. Нажав кнопку Start, запускаем компиляцию. По окончании компиляции можно видеть какие файлы были сформированы, какое семейство и конкретное устройство были выбраны автоматически. Также выводится сообщение об успешном прохождении компиляции (рисунок 2.20).

Рисунок 2.20 – Компиляция проекта

Компилятор генерирует файл отчёта (.rpt) (report file), в котором задокументирована информация о разбиении проекта, именах входных и выходных контактов, временных параметрах проектах и неиспользованных ресурсах для каждого устройства в проекте. Он также автоматически формирует файл трассировки (.fit). В нём документируются назначения ресурсов и устройств для всего проекта, а также информация о трассировке. Компилятор создаёт файл (.snf) для функционального тестирования и тестирования временных параметров в симуляторе.

2.2.7 Верификация проекта

Дальше следует заняться верификацией проекта. Для этого используем симулятор (Simulator), анализатор временных параметров (Timing Analizer) и сигнальный редактор

(Waveform Editor).

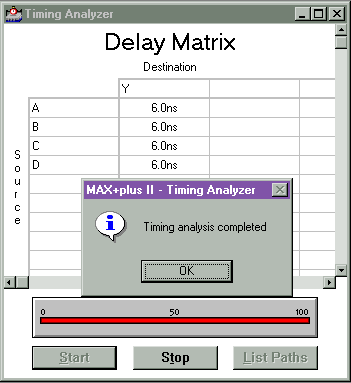

Ч тобы

узнать временные задержки сигнала при

прохождении от входа к выходу используем

анализатор временных параметров, который

запускается пиктограммой с инструментальной

панели.

тобы

узнать временные задержки сигнала при

прохождении от входа к выходу используем

анализатор временных параметров, который

запускается пиктограммой с инструментальной

панели.

Рисунок 2.21 – Завершение временного анализа

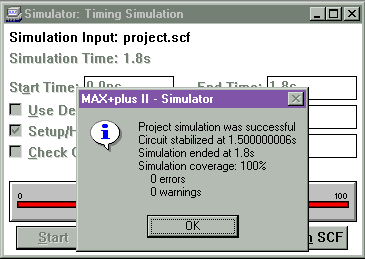

С имулятор

запускается посредством выбора на

инструментальной панели пиктограммы

“Simulator”.

Полученный в процессе компиляции файл

SNF

загружается автоматически при открытии

симулятора. В качестве источника входных

векторов используется графический

сигнальный файл каналов тестирования

– Simulator

Channel

File

(.scf),

созданный в сигнальном редакторе. Нажав

“Start”

– проведём тестирование логических

операций и внутреннюю синхронизацию

проекта.

имулятор

запускается посредством выбора на

инструментальной панели пиктограммы

“Simulator”.

Полученный в процессе компиляции файл

SNF

загружается автоматически при открытии

симулятора. В качестве источника входных

векторов используется графический

сигнальный файл каналов тестирования

– Simulator

Channel

File

(.scf),

созданный в сигнальном редакторе. Нажав

“Start”

– проведём тестирование логических

операций и внутреннюю синхронизацию

проекта.

Рисунок 2.22 – Завершение симуляции

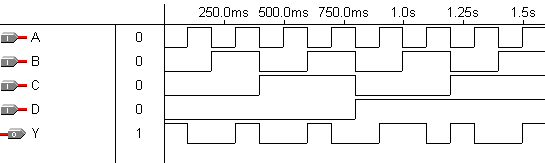

По завершении симуляции проекта откроем файл SCF кнопкой Open SCF.

Рисунок 2.23 – Смоделированные значения выходного сигнала

Выбрав в меню File команду Create Table File можно сформировать табличный файл, содержащий результаты моделирования, с расширением .tbl, который можно просматривать в текстовом редакторе.

Сравнив параметры выходного сигнала с таблицей истинности, можно сказать, что устройство, реализованное на ПЛИС Altera семейства MAX7000 – EPM7032LC44-6, работает правильно.

2.2.8 Задание для самостоятельной разработки

По заданному булеву выражению построить таблицу истинности устройства. Построить схему, состоящую из двоичных логических элементов, в графическом редакторе Graphic Editor. В сигнальном редакторе Waveform Editor построить входные сигналы проекта. Осуществить компиляцию и симуляцию проекта на ПЛИС с созданием всех необходимых файлов. По результатам моделирования сделать вывод о правильности реализации цифрового устройства на ПЛИС.

Таблица 2.3 – Варианты заданий для самостоятельной разработки.

Номер варианта |

Булево выражение |

1 |

|

2 |

|

3 |

|

4 |

|

5 |

|

продолжение таблицы 2.3

Номер варианта |

Булево выражение |

6 |

|

7 |

|

8 |

|

9 |

|

10 |

|

11 |

|

12 |

|

13 |

|

14 |

|

15 |

|

Лабораторная работа №2. Описание цифровых схемы на языке AHDL

Цель и содержание работы: В этой работе изучается процесс описания цифрового устройства на языке AHDL и создание нового элемента на базе этого описания. С помощью редактора Text Editor создаётся текстовый файл описания схемы на языке AHDL. На основе текстового файла создаётся символьный файл, который с помощью редактора Graphic Editor включается в иерархический проект. После этого выполняется трансляция проекта, формирование тестовых векторов и симуляция в последовательности, аналогичной предыдущей работе.