- •Введение

- •1. Сбор данных (согласно инструкции по выполнению работы).

- •2. Оформление отчета.

- •3. Защита лабораторной работы

- •Практическая работа №1 «Перевод чисел из одной системы счисления в другую»

- •Основные положения

- •Порядок выполнения работы

- •Практическая работа №2 «Анализ и синтез комбинационных схем с одним выходом»

- •Основные положения

- •Порядок выполнения работы

- •Практическая работа №3 «Синтез логических схем в базисах имс»

- •Основные положения Лабораторная работа №1 «Изучение работы дешифратора»

- •Основные положения

- •Выполнение работы

- •Лабораторная работа №2 «Изучение принципа работы мультиплексора»

- •Основные положения

- •Выполнение работы

- •Лабораторная работа №3 «Изучение принципа работы многоразрядного сумматора»

- •Основные положения

- •Выполнение работы

- •Лабораторная работа №4 «Изучение принципа работы цифровых компараторов»

- •Основные положения

- •Выполнение работы

- •Лабораторная работа №5 «Изучение принципа работы rs-триггера»

- •Основные положения

- •Выполнение работы

- •Лабораторная работа №6 «Изучение принципа работы т и d триггеров»

- •Основные положения и расчетные формулы

- •Выполнение работы

- •Лабораторная работа №7 «Изучение принципов работы и способов включения jk-триггера»

- •Основные положения

- •Выполнение работы

- •Лабораторная работа №8 «Изучение принципа работы регистров параллельного действия»

- •Основные положения

- •Выполнение работы

- •Лабораторная работа №9 «Изучение принципа работы регистров последовательного действия»

- •Основные положения

- •Выполнение работы

- •Лабораторная работа №10 «Изучение принципа работы счетчика»

- •Основные положения

- •Выполнение работы

- •Лабораторная работа №11 «Изучение режимов работы цап»

- •Основные положения

- •Выполнение работы

- •Лабораторная работа №12 «Изучение режимов работы ацп»

- •Основные положения

- •Выполнение работы

Выполнение работы

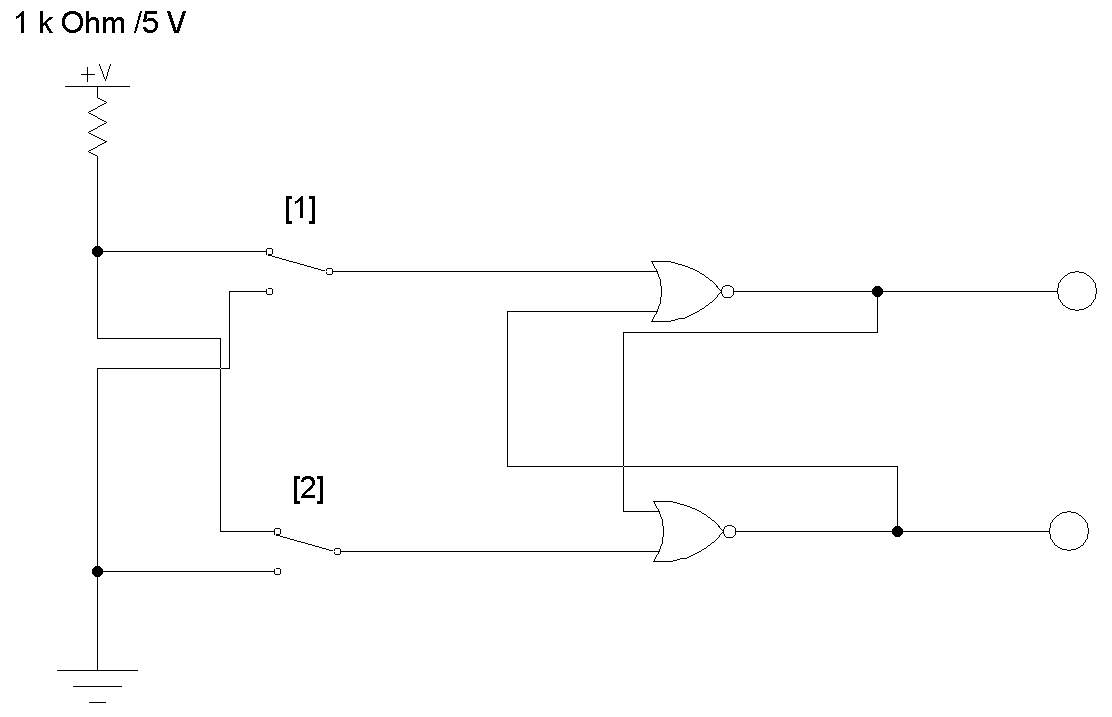

В программе Electronics Workbench собрать схему асинхронного RS-триггера, представленную на рис. 2. Произвести моделирование составленной схемы, переключив в положение «1» кнопку . Управляя клавишами «1», «2» и наблюдая за индикаторами, убедиться в правильности таблицы 1.

Убедиться в наличии запрещенного состояния у RS-триггера. Обосновать его возникновение и предложить методы по его устранению.

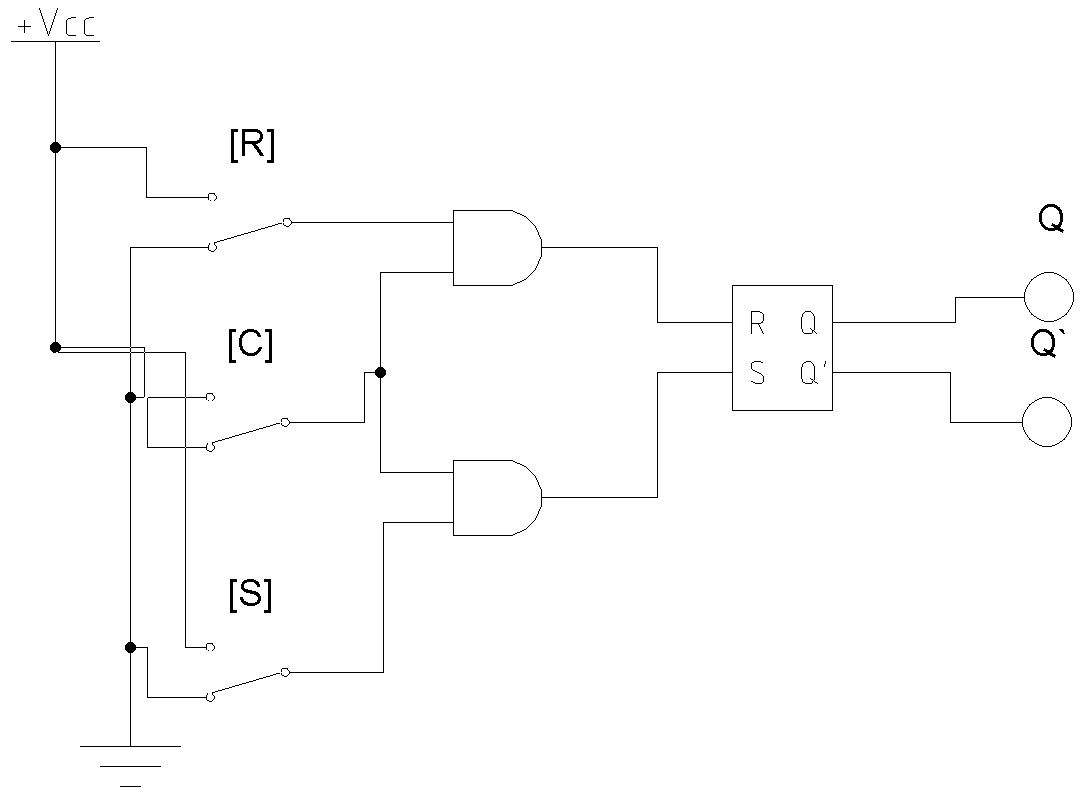

В программе Electronics Workbench собрать схему синхронного RСS-триггера, представленную на рис. 3. Произвести моделирование составленной схемы, переключив в положение «1» кнопку . Управляя клавишами «R», «C», «S» и наблюдая за индикаторами, составить таблицу истинности для синхронного RСS-триггера.

Оформить отчет по работе.

Рис. 8.2

Рис. 8.3

Лабораторная работа №6 «Изучение принципа работы т и d триггеров»

Цель работы: Исследовать принцип работы Т-триггера и D-триггера.

Оборудование: ПЭВМ

Программное обеспечение: Electronics Workbench

Основные положения и расчетные формулы

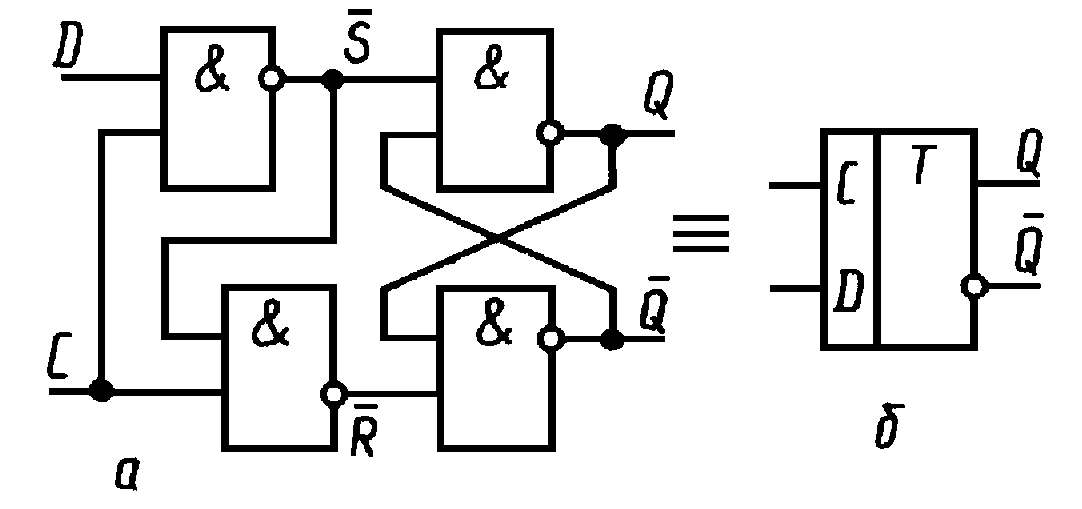

Синхронный D-триггер свободен от недостатков RS-триггера. D-триггер (рис. 9.1, а) образован из RS-триггера и входной комбинационной схемы на двух логических элементах. Сигналы, предназначенные для занесения в триггер, поступают на информационный вход D. На вход синхронизации С подают синхроимпульсы, определяющие момент записи информации. Описание работы триггера при различных комбинациях входных сигналов представлено в таблице 9.1. Из таблицы иллюстрирующих описанный процесс хранения и записи информации, видно, что D-триггер находится в режиме хранения при С = 0 и в режиме записи при С = 1. Такой триггер задерживает выходной сигнал до окончания того такта, в который он был записан. Так, входной сигнал D = 1 кончается между первым и вторым, четвертым и пятым синхроимпульсами, а состояние Q = 1 сохраняется до конца второго и пятого тактов. Отсюда произошло и название D-триггера (от англ. delay – задержка). Если сигнал на входе изменится во время действия синхроимпульса, то в триггере окажется записанной та информация, которая предшествовала окончанию синхроимпульса. Благодаря этому свойству (изменение информации в течение всего времени, пока С = 1) рассмотренный триггер называется статическим синхронным D-триггером. Для нормальной работы статического D-триггера необходимо, чтобы изменение информации на D-входе происходило только при С = 0.

Рис. 9.1

Таблица 9.1

C |

D |

|

|

Q |

Режим работы |

0

|

0

|

|

|

Предыдущее значение |

Хранение

|

0 |

1 |

|

|

Предыдущее значение |

Хранение |

1 |

0 |

|

|

0 |

Запись 0 |

1 |

1 |

|

|

1 |

Запись 1 |

Счетный T-триггер имеет один управляющий вход и два выхода. Информация на выходах такого триггера меняется на противоположную при каждом положительном перепаде напряжения на счетном входе Т, поэтому счетный триггер используется в качестве делителя частоты входного сигнала. Триггер такого типа может быть создан из D-триггера с динамическим управлением, если его инверсный выход соединить с информационным входом. При этом, если в начальный момент времени на выходе Q был нулевой уровень, то на входе D был уровень = 1. По фронту первого синхроимпульса единица с D-входа перепишется (с опозданием, равным задержке одного логического элемента; рис. 3.14, в и 3.12, б) на выход Q. Соответственно на выходе и на входе D появится нулевой уровень (с опозданием, равным задержкам двух логических элементов). В следующем такте на выход Q будет переписано нулевое значение с входа D и т. д.

Создать счетный триггер на базе статического D-триггера таким, же образом (обратной связью с выхода на вход D) нельзя. Так как статический триггер имеет потенциальное управление, то при С = 1 напряжение на выходе за счет влияния обратной связи будет постоянно меняться на обратное, т. е. возникнут высокочастотные колебания.