- •Введение

- •1. Сбор данных (согласно инструкции по выполнению работы).

- •2. Оформление отчета.

- •3. Защита лабораторной работы

- •Практическая работа №1 «Перевод чисел из одной системы счисления в другую»

- •Основные положения

- •Порядок выполнения работы

- •Практическая работа №2 «Анализ и синтез комбинационных схем с одним выходом»

- •Основные положения

- •Порядок выполнения работы

- •Практическая работа №3 «Синтез логических схем в базисах имс»

- •Основные положения Лабораторная работа №1 «Изучение работы дешифратора»

- •Основные положения

- •Выполнение работы

- •Лабораторная работа №2 «Изучение принципа работы мультиплексора»

- •Основные положения

- •Выполнение работы

- •Лабораторная работа №3 «Изучение принципа работы многоразрядного сумматора»

- •Основные положения

- •Выполнение работы

- •Лабораторная работа №4 «Изучение принципа работы цифровых компараторов»

- •Основные положения

- •Выполнение работы

- •Лабораторная работа №5 «Изучение принципа работы rs-триггера»

- •Основные положения

- •Выполнение работы

- •Лабораторная работа №6 «Изучение принципа работы т и d триггеров»

- •Основные положения и расчетные формулы

- •Выполнение работы

- •Лабораторная работа №7 «Изучение принципов работы и способов включения jk-триггера»

- •Основные положения

- •Выполнение работы

- •Лабораторная работа №8 «Изучение принципа работы регистров параллельного действия»

- •Основные положения

- •Выполнение работы

- •Лабораторная работа №9 «Изучение принципа работы регистров последовательного действия»

- •Основные положения

- •Выполнение работы

- •Лабораторная работа №10 «Изучение принципа работы счетчика»

- •Основные положения

- •Выполнение работы

- •Лабораторная работа №11 «Изучение режимов работы цап»

- •Основные положения

- •Выполнение работы

- •Лабораторная работа №12 «Изучение режимов работы ацп»

- •Основные положения

- •Выполнение работы

Выполнение работы

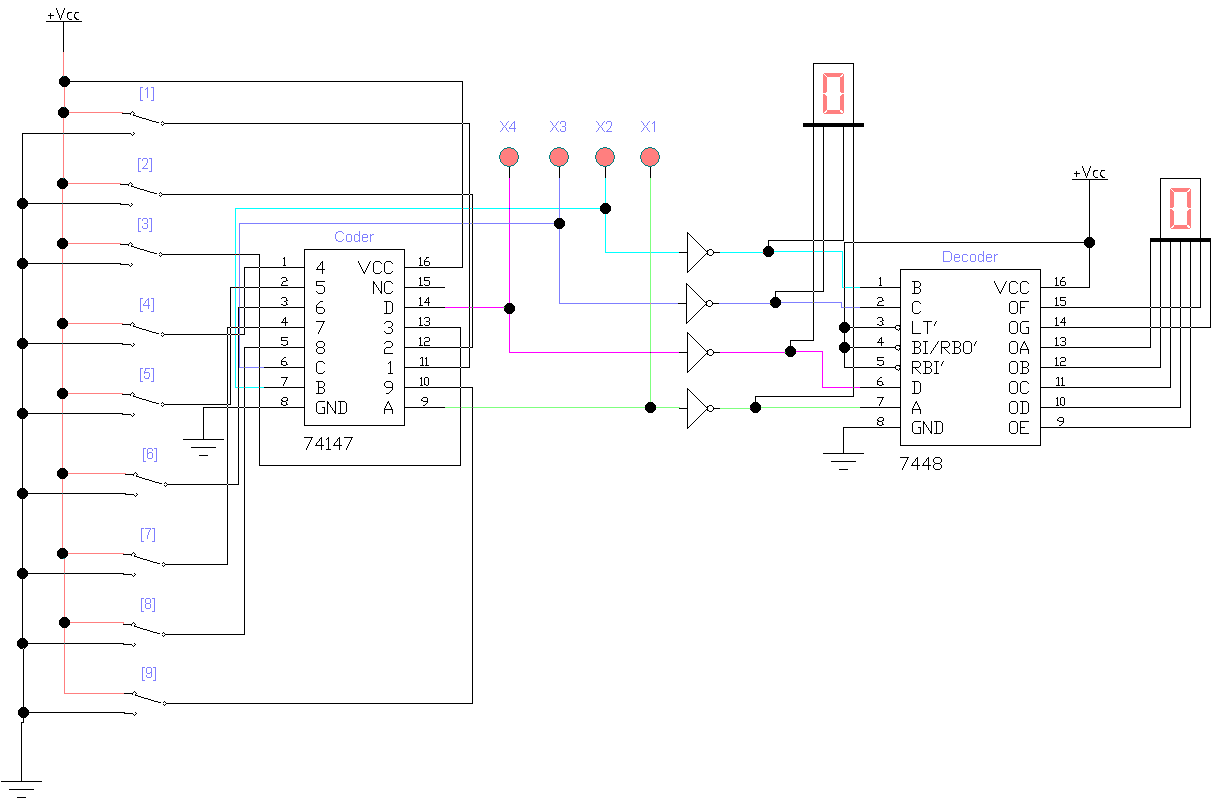

В программе Electronics Workbench собрать схему канала передачи сигнала, состоящего из шифратора и дешифратора представленную на рис. 4.2. Произвести моделирование составленной схемы, переключив в положение «1» кнопку

.

Управляя клавишами «1 - 9» и наблюдая за

индикаторами, убедиться в правильности

работы схемы.

.

Управляя клавишами «1 - 9» и наблюдая за

индикаторами, убедиться в правильности

работы схемы.

Рис. 4.2

Оформить отчет и сделать выводы по работе.

Лабораторная работа №2 «Изучение принципа работы мультиплексора»

Цель работы:

Оборудование: ПЭВМ

Программное обеспечение: Electronics Workbench

Основные положения

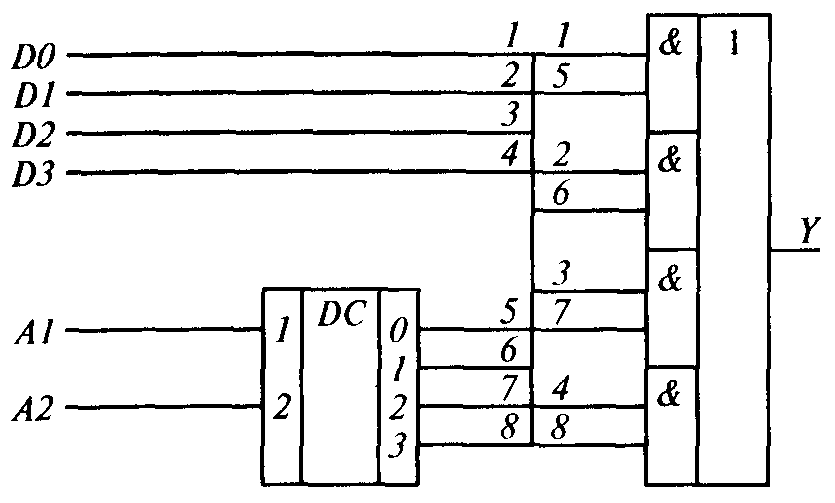

Мультиплексор (рис. 5.1) в вычислительных устройствах используется, например, для записи в регистр кодов, поступающих из разных запоминающих устройств или устройств ввода. Подсоединение к источникам сигналов производится последовательно (в так называемых системах обегающего контроля) или адресно – по выбору оператора.

Показанный на рис. 5.1 мультиплексор позволяет подключать к выходу Y один из четырех информационных входов D0, D1, D2, D3. Выбор информационного входа осуществляется подачей на два адресных входа А1 и А2 соответствующего кода: 00, 01, 10, 11. Например, при подаче на адресные входы сигнала 10 (т.е. десятичная двойка) на выходе 2 дешифратора DC появляется 1, которая по входу 7 поступает на двухвходовый логический элемент И. На другой вход этого элемента поступает информационный сигнал по каналу D2.

Значит, именно этот второй информационный вход будет подключен к выходу Y мультиплексора. С помощью мультиплексора может быть организована передача сигналов по одному и тому же каналу (выходу Y) от нескольких источников информации, но не одновременно.

Рис. 5.1. Мультиплексор

При подаче на адресные входы А1 и А2 кода 00 информация передается от входа D0, при подаче кода 01 – от входа D1 и т.д. Следовательно, можно сказать, что выход Y представляет собой канал с временным разделением сигналов.

После получения информации по такому единственному каналу связи Y ее необходимо разделить между соответствующими приемниками.

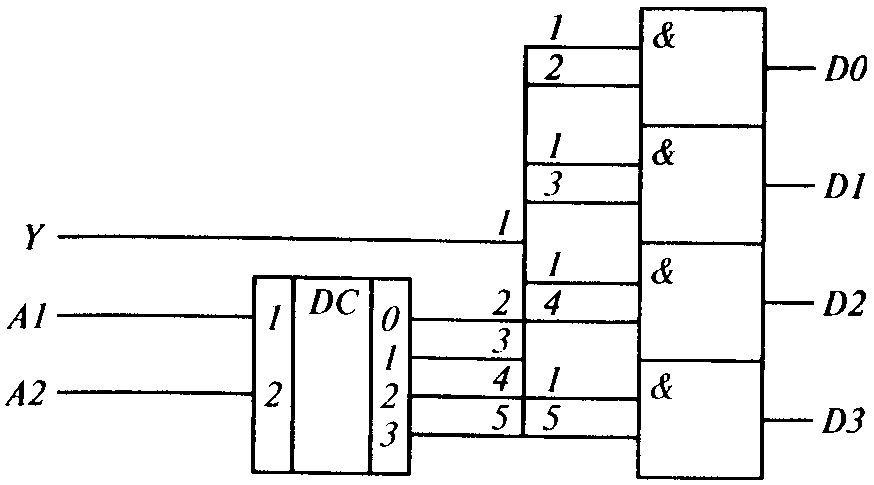

Эту задачу решает демультиплексор (рис. 5.2). Выбор соответствующего информационного выхода осуществляется с помощью адресного входа. Как и в схеме мультиплексора, используется дешифратор DC.

При подаче на адресные входы A1 и А2 сигнала 10 на выходе 2 появляется 1 и входной сигнал Y проходит на информационный выход D2.

Рис. 5.2. Демультиплексор

Выполнение работы

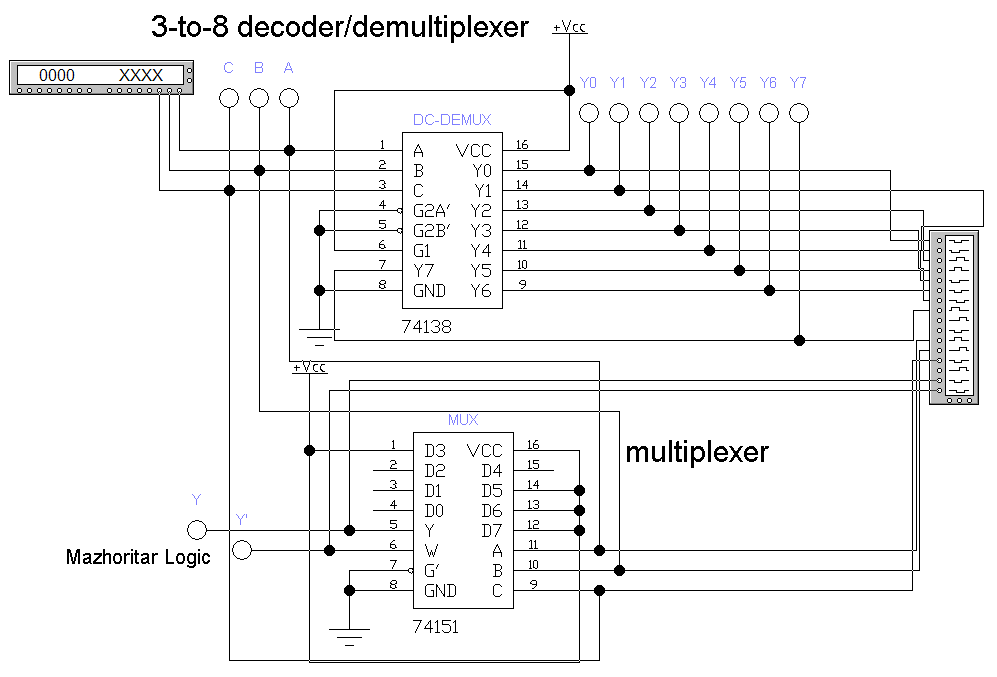

В программе Electronics Workbench собрать схему мультиплексорно-демультиплексорного канала связи, представленного на рис. 5.3. Произвести моделирование составленной схемы, переключив в положение «1» кнопку . Наблюдая за работой генератора двоичного кода и построителя временных диаграмм, убедиться в правильности работы схемы.

Рис. 5.3.

Оформить отчет и сделать выводы по работе.

Лабораторная работа №3 «Изучение принципа работы многоразрядного сумматора»

Цель работы: Изучение принципа работы многоразрядного сумматора

Оборудование: ПЭВМ

Программное обеспечение: Electronics Workbench

Основные положения

Сумматор представляет собой комбинационное цифровое устройство, предназначенное в основном для суммирования двоичных чисел. Кроме того, с помощью сумматора могут выполняться вычитание, умножение, деление, преобразование чисел в дополнительный код и некоторые другие операции. Обычно сумматор состоит только из логических элементов, а результат операции направляется затем для записи в регистр.

Классификация сумматоров может быть проведена по трем основным признакам: числу входов (полусумматоры, одноразрядные и многоразрядные сумматоры). Многоразрядные сумматоры, в свою очередь, подразделяются на последовательные и параллельные; последние по способу организации межразрядных переносов подразделяются на сумматоры с последовательным и параллельным переносом и с групповой структурой; способу тактирования (синхронные и асинхронные сумматоры); системе счисления (двоичные, двоично-десятичные и др.).

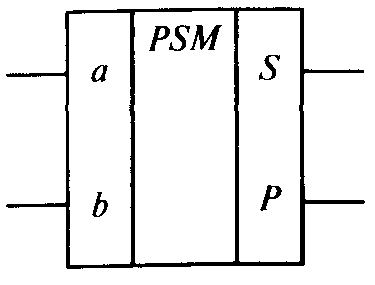

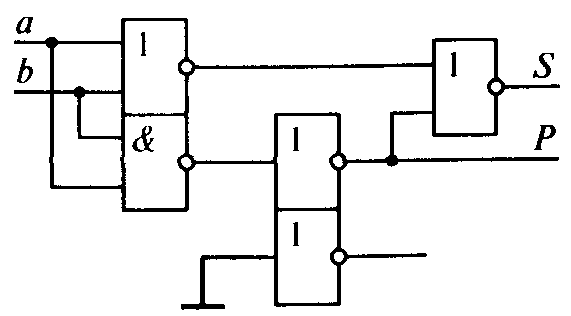

Полусумматорами (рис. 6.1, 6.2) называют устройства с двумя входами (а, b) и двумя выходами, на одном из которых вырабатывается сигнал суммы (выход S), а на другом – сигнал переноса (выход Р). Табл. 6.1 является таблицей истинности полусумматора.

Рис. 6.1. Условное обозначение полусумматора

Рис. 6.2. Схема полусумматора на логических элементах

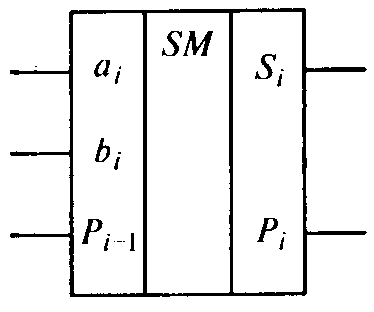

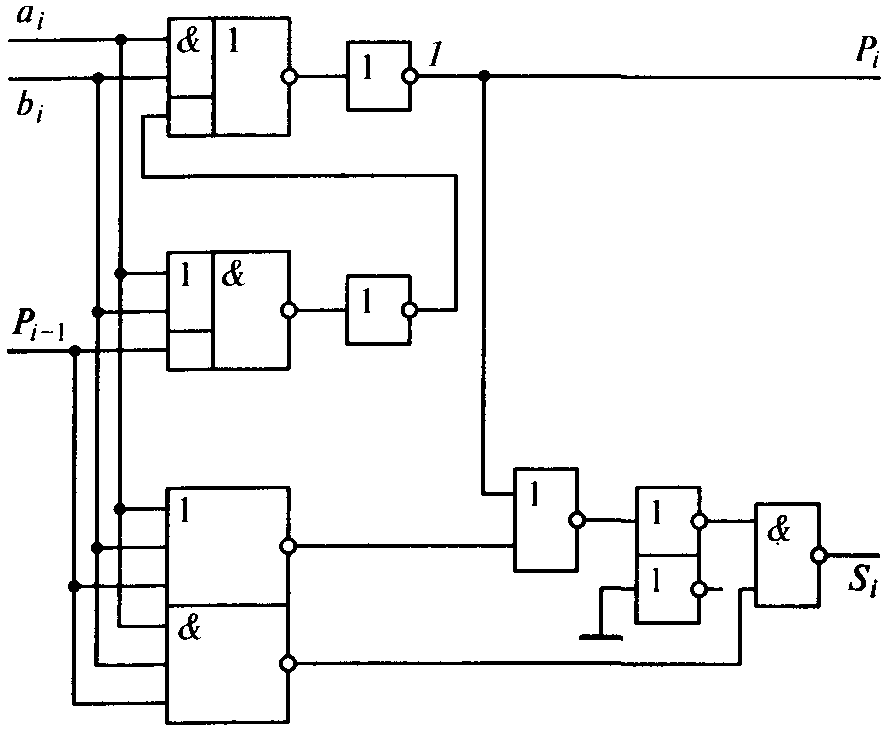

Полным одноразрядным сумматором (рис. 6.3, 6.4) называют устройство с тремя входами и двумя выходами. Кроме двух входов для чисел он имеет третий вход, на который подается сигнал переноса из предыдущего разряда. Одноразрядный сумматор является основным элементом многоразрядных сумматоров. Он выполняет арифметическое сложение одноразрядных двоичных чисел ai и bi и перенос Pi-1 из предыдущего разряда с образованием на выходе суммы Si и переноса Pi в старший разряд (табл. 6.2).

Таблица 6.1

Таблица истинности полусумматора

а |

b |

S |

P |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

Рис. 6.3. Условное обозначение одноразрядного сумматора

Рис. 6.4. Схема одноразрядного сумматора на логических элементах 134

Операции сложения бывают последовательными и параллельными. В данном случае под последовательностью понимается поочередное, разряд за разрядом, сложение (или вычитание) на одноразрядной схеме с задержкой переносов (или займов) для использования их как третьих аргументов в следующем такте, т. е. в разряде.

Таблица 6.2

Таблица истинности одноразрядного сумматора

аi |

bi |

Pi-1 |

Si |

Pi |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

Используя различные варианты преобразования этих функций, можно реализовать большое число структур одноразрядных двоичных сумматоров (например по схеме, показанной на рис. 6.5).

Для обработки многоразрядных чисел объединяется соответствующее число одноразрядных сумматоров. При этом отдельные разряды обрабатываемых чисел А и В подаются на входы ai и bi. На вход Pi подается перенос из предыдущего, более младшего разряда. Формируемый в данном разряде перенос Pi+1 передается в следующий, более старший разряд. Такая организация процесса формирования переноса, называемая последовательным переносом, снижает быстродействие многоразрядного сумматора, так как получение результата в старшем разряде сумматора обеспечивается только после завершения распространения переноса по всем разрядам. Поэтому иногда организуется параллельный перенос.

Рис. 6.5. Схема одноразрядного двоичного сумматора