- •Машины общего назначения (пк и др.).

- •Специализированные эвм.

- •Проблемно-ориентированные машины.

- •Арифметико-логическое устройство эвм как операционное устройство.

- •2. Умножение , начиная с младших разрядов множителя со сдвигом множимого.

- •Умножение, начиная со старших разрядов множителя со сдвигом множимого.

- •Синхронный метод

- •Асинхронный метод

- •2Такт – y(-)(сдвиг)

Типовая архитектура и взаимодействие устройств ЭВМ

Архитектура ЭВМ – это совокупность свойств и характеристик ЭВМ, рассматриваемых с точки зрения пользователя.

Архитектура ЭВМ – это принцип работы вычислительной системы на функциональном уровне без относительной физической реализации.

Архитектура - это точно определенный интерфейс между программой и аппаратурой вычислительный систем.

При структурном описании устройства выделяются элементы и связи между ними.

Шина содержит линии адреса, данных и управляющие линии.

Процессор – это устройство, которое выполняет определенный набор команд (система команд) и обрабатывает сигналы для управления, взаимодействия всех устройств.

Процессор включает в себя следующие операционные устройства:

АЛУ (если оно встроено);

РК (регистр команд) для хранения текущей исполняемой команды;

СЧАК хранит продвинутый адрес команды;

Блок РОН;

РФ;

Блок РСФТ (регистры специальных функций);

РПр (регистр признаков).

Виды команд:

Команды пересылки информации (загрузка регистров, запись информации в память).

Команды преобразования информации (арифметические, логические операции и т.д.).

Операции передачи управления (различные переходы).

Операции ввода-вывода.

Операции управления состоянием машин (управление режимом работы).

Оперативная память предназначена для хранения команд и данных программы, выполняемой в текущий момент, хранит информацию только при наличии напряжения. Состоит из ячеек (слов), имеющих адрес.

Фон-Неймовская (Принстонская архитектура) предполагает, что в ОП хранятся и команды, и данные.

Гарвардская архитектура предполагает аппаратное и логическое разделение памяти данных и команд.

Требование к ОП:

Быстродействие;

Большой объем;

Низкая стоимость.

КЭШ – это сверхоперативная память. В нее копируются наиболее часто использующиеся области ОП, что повышает быстродействие системы в целом.

СОП быстродействинен засчет триггеров.

ВЗУ (внешние запоминающие устройства) нужны для хранения большого количества информации.

УВВ (устройства ввода-вывода) предназначены для обмена информации.

Сопроцессор – это процессор, специализирующийся на заданном множестве операций (арифметический сопроцессор, видеопроцессор).

ПЗУ (постоянно запоминающее устройство) – сохранность информации не зависит от питания(BIOS).

В ПЗУ содержатся следующие программы:

Программы начального запуска;

Тест начальной загрузки;

Драйверы внешних устройств.

Сетевой адаптер служит для подсоединения ЭВМ в вычислительную сеть.

Взаимодействие устройств ЭВМ в процессе выполнения операции (рабочий цикл процессора).

Старшие k-разрядов содержат код операции, а младшие адрес операндов в ОП.

Демонстрация на простейшей ЭВМ.

Выборка команды.

Адрес команды, которую нужно выбрать находится в СЧАК.

РАОП: = СЧАК (у1)

Чтение (у2)

РК: = РСОП (у3)

Загрузка операндов.

Регистр команд = регистру кода операции + регистр адреса

РАОП: = РА (у1)

Чтение (у2)

РАЛУ: = РСОП (у3)

Исполнение команды.

Дешифратор расшифровывает код операции. В ответ на сигнал xi=1 устройство управления вырабатывает управляющий сигнал yiалу, соответствующий коду исполняемой команды. Сигнал yiалу инициируют в АЛУ соответствующую операцию, которая выполняется над операндом, находящимся в регистре АЛУ. Результат выполнения операции находится в сумматоре.

Запись результата в ОП.

{xi} – {yi}

РАОП: = РА (у4)

РСОП: = СМ (у6)

Запись (у7)

Модификация СЧАК.

СЧАК: = СЧАК+L, (у8)

где L – длина команды.

у1 у2 у3 у4 у2 у5 уiалу у6 у7 у8 - микропрограмма работы устройства (рабочий цикл).

Анализ прерывания.

Действие прерывания по сигналам прерывания.

Процессор анализирует состояния регистра флагов. Каждый разряд РФ соответствует определенному виду прерывания, следовательно, определенной программе обработки прерываний.

Прерывания: деление на ноль, переполнение, прерывание внешнего устройства и т.д..

Процессор запоминает состояние ЭВМ в момент прерывания в определенных ячейках памяти (в стеке или по определенному адресу в ОП). Запоминается СЧАК, признак результата, РОНы – слово состояния программ (ССП – PSW).

Из ОП загружается новое слово состояния программ (ССП). Оно считывается по адресу, определенному причиной прерывания (единичным разрядом РФ).

Новое ССП распределяется по управляющим регистрам, при этом в СЧАК появляется адрес первой команды программы обработки прерываний.

Процессор опять выполняет свои рабочий цикл (п.1). В программе обработки прерываний это последовательная программа возврата в первоначальную программу (RET). По этой команде загружается старое ССП.

Режимы работы ЭВМ.

Однопрограммный режим;

Мультипрограммный режим:

пакетная обработка программ

режимы разделения времени.

Пакетный режим.

На входе машины формируется пакет задач. Задачи в пакет подбираются так, чтобы равномерно загрузить оборудование.

Режим разделения времени.

Это способ организации вычислительного процесса, при котором несколько программ реализуются одновременно, каждой программе для работы выделяется τ=1\30 сек. времени.

Для реализации этого режима необходима мощная система обслуживания прерываний и система защиты памяти.

Характеристики ЭВМ.

емкость ОП (в ПК до 512 МБ).

шина выборки – число регистров РСОП или число разрядов шины.

операционные ресурсы – это система команд процессора.

типы данных характеризуют разрядность слов, над которыми выполняются операции.

быстродействие характеризуется средним временем выполнения операции, либо количеством операций в секунду. Зависит от тактовой частоты процессора (от технологии и архитектуры вычислительных систем).

1 t1 k1

2 t2 k2

. . .

n tn kn

ki – относительная частота использования операции.

Рср. – среднее количество операций выполняемых в единицу времени.

Рср.=1/tср.

Такая характеристика быстродействия не учитывает:

конкретные виды взаимодействия устройств ЭВМ при выполнении команд различных форматов;

использование параллелизма в вычислениях;

процесса выполнения прерываний и стратегии Кэширования.

производительность ЭВМ – это объем времени, требуемый для решения типового пакета программ. Из двух ЭВМ производительней считается та, у которой

математическое (программное) обеспечение расширяет операционные ресурсы ЭВМ.

надежность – вероятность в произвольный момент времени застать ЭВМ в работоспособном состоянии.

Сбои – кратковременная самоустраняющаяся неисправность.

Отказ – долговременная неисправность, требующая ремонта.

Надежность определяется средним количеством сбоев и отказов в единицу времени.

САКДН – система автоматического контроля и диагностики неисправности, отвечает за работу ЭВМ.

К САКДН относятся тесты начальной загрузки, схемы контроля при выполнении арифметической операции, схемы контроля по четности и т.д..

Классификация ЭВМ.

Машины общего назначения (пк и др.).

Это машины с универсальной системой команд, применяется при решении любых типов задач. Машины характеризуются высокой производительностью, работа в мультипрограммном режиме. Используются в больших вычислительных центрах общего пользования.

Специализированные эвм.

Применяются для быстрого решения задач конкретного класса. Быстродействие достигается расчет специальных архитектур (матричные архитектуры, систолические процессоры, ассоциативные процессоры, нейронные сети) этих машин. Процессоры семейства ТМС применяются для обработки изобретения и звука (дифференциаторы, анализаторы и др.).

Проблемно-ориентированные машины.

Это микро устройства встроенные в другие приборы и контуры управления. Они управляют технологическими процессами, бортовыми системами и т.д. для них не важно высокое быстродействие. У этих машин невысокая тактовая частота и ограниченная система команд.

Уровни представления и описания ЭВМ.

ЭВМ – это сложная система, которая характеризуется большим числом элементов, которые сильно взаимосвязаны. Вся система в целом представляет собой нечто качественно новое, отличное от элементов ее составляющих.

Элемент системы – это объект, который в свою очередь может быть разбит на более мелкие структурные элементы и описанные определенным функциональным аппаратом.

Уровень |

Объекты |

Структурный базис |

Функциональный базис

|

Тип схемы |

Единицы информа- ции |

0. |

логические и запоминающие элементы

|

электронные компоненты |

ТОЭ |

электрическая принципиальная |

|

1. |

операционные элементы и управляющие автоматы |

логические и запоминающие элементы

|

ПТЦА |

электрическая функциональная |

биты |

2. |

операционные устройства |

операционные элементы и управляющие автоматы |

микропрограммы |

электрические функциональные структурные |

слова поля |

3. |

ЭВМ, сети ЭВМ |

операционные устройства |

программы |

структурные |

слова поля массивы |

Операционное устройство.

ОУ – это устройство, выполняющее множество операций F над множеством входных слов А, с целью получения множества результирующих слов В.

ЭВМ – совокупность взаимосвязанных ОУ.

О перационный

автомат (ОА) предназначен для преобразования

информации под воздействием управляющих

сигналов yi,

формируемых управляющим автоматом

(УА).

перационный

автомат (ОА) предназначен для преобразования

информации под воздействием управляющих

сигналов yi,

формируемых управляющим автоматом

(УА).

В УА сосредоточены все функции, выполняемые ОА, описанные аппаратом микропрограмм.

Синтез ОА упрощается за счет того, что методы ПТЦА применяются к синтезу одного типового разряда, а нужная разрядность слова набирается путем собирания схем типовых разрядов.

Принцип микропрограммного управления.

Каждая сложная операция (+, / , * и т.д.) реализуется как микропрограмма, т.е. как последовательность элементарных операций, выполняемых операционными элементами под воздействием управляющих сигналов yi.

Эти элементарные операции, которые выполняются за один такт, называются микрооперациями.

Пример:

y1: P1(1:n);

y2: C(1:n):=C(1:n)+1;

ys: P(1:n):=P(n)P(1:n-1);

Чтобы в микропрограмме предусмотреть возможность разветвления из ОА в УА поступают осведомительные сигналы xj.

Пример:

xj Є {0,1}

Осведомительные сигналы xj характеризуют промежуточные результаты выполнения микропрограмм.

x1=(P(1:n)=00..0)

x2=P(1)

x3=(P1(1:n)>P2(1:n))

Способы представления микропрограмм. Граф-схема алгоритма (ГСА).

DCL - формальный язык представления микропрограмм.

Граф-схема алгоритма предусматривает представление микропрограммы в виде графа.

Четыре типа вершин ГСА:

начало

конец

![]()

микрокоманда – это набор микроопераций, которые выполняются в одном такте, одновременно.

условная вершина

y – сигнал микрооперации;

Y – сигнал микрокоманды.

Микрооперации, которые можно объединить в одном такте, называются совместными (микрооперации над разной аппаратурой).

Пример:

Построить

ГСА микропрограммы и структурную схему

ОУ, вычисляющего число единиц в слове

А.

А – сдвиговый регистр

С – счетчик

k =

![]()

Содержательный ГСА для ситеза ОА, для синтеза УА содержание микроопераций неважно, важна последовательность.

Синтаксис языка ГСА.

Правила ГСА:

Каждая ГСА должна содержать одну начальную и одну конечную вершину.

Каждый выход вершины соединяется дугой только с одним входом.

Любой выход соединяется по крайней мере с одним и только одним входом. Не может быть висящих вершин ГСА.

Ждущая вершина используется там, где нужно приостановить реализацию микропрограммы до получения ответа Х.

Из любой вершины графа должен существовать хотя бы один путь в конечную вершину.

В любую вершину графа должен вести хотя бы один путь из начальной вершины.

Структура и методы проектирования ОА.

Два типа структур ОА:

1). ОА с закрепленными микрооперациями.

2). ОА с общими микрооперациями.

Этапы синтеза ОА с закрепленными микрооперациями.

Если в микрооперации упоминается слово Ai(1:ki), то в структуре ОА резервируется регистр Ai. Если слов много, то имеем следующую композицию регистров:

Если есть передача информации Ai : = As, тогда два эти регистра

связываются между собой управляющей шиной.

Если над словом Ai выполняется микрооперация yj , предусматриваются соответствующие схемы выполнения микрооперации.

Xi – множество осведомительных сигналов, выполняемых над регистром Ai

Fi – множество микроопераций yj, выполняемых над i–тым регистром.

F1,F2,…,Fn – множество всех микроопераций, выполняемых ОА.

Если над словом Ai вычисляется некоторый осведомительный сигнал xl=f(Ai), то в схему Ai включаются соответствующие цепи вычисления xl.

Xi – множество осведомительных сигналов, вычисляемых над регистром Ai.

Для каждого операционного элемента (ОЭ) Ai , выполняющего множество операций Fi в справочниках ищут типовое решение. Например: сдвиговой разряд, счетчик и т.д. Если список Fi обширен и такого элемента в справочнике нет, то он подлежит проектированию. Три способа проектирования ОЭ:

комбинирование из типовых ОЭ,

синтез типового разряда и набор нужной разрядности,

комбинирование первых двух.

Пример:

Синтезировать ОЭ, выполняя микрооперации сдвига и счета.

способ

сдвиг за 1 такт, если снимаем результат с регистра

для счета 3 такта

y1 yсч y2

Проектируем n-разрядный комбинационный счетчик путем синтеза типового разряда и соединяем регистр с комбинационным счетчиком.

Пример:

Синтезировать ОЭ, выполняя микрооперации сдвига и счета.

способ

сдвиг за 1 такт, если снимаем результат с регистра

для счета 3 такта

y1 yсч y2

Проектируем n-разрядный комбинационный счетчик путем синтеза типового разряда и соединяем регистр с комбинационным счетчиком.

Шины.

Шина – операционный элемент (ОЭ), служащий для выполнения микрооперации передачи информации, например, между регистрами:

y1: B(1:n):= A(1:n),

y2: B(1:n):= A(1:n) (инверсная передача).

Регистр А называют источником информации, а регистр B – приемником.

Шины состоят из цепей.

Цепь – ОЭ, служащий

для передачи одного бита информации. В

простейшем случае цепь – это проводник.

Информация на его концах совпадает (![]() ,

рисунок 19, а). На рисунке 19, б показана

управляемая цепь. Информация передается

по цепи только при наличии управляющего

сигнала у (

,

рисунок 19, а). На рисунке 19, б показана

управляемая цепь. Информация передается

по цепи только при наличии управляющего

сигнала у (![]() ).

Условное изображение управляемой шины

на структурных схемах ОУ приведено на

рисунке 19, в.

).

Условное изображение управляемой шины

на структурных схемах ОУ приведено на

рисунке 19, в.

В иды

цепей:

иды

цепей:

однофазные,

парафазные.

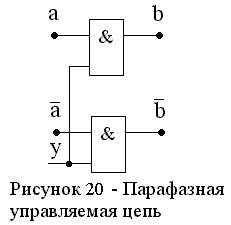

Однофазные цепи (управляемые или неуправляемые) передают только прямое или только инверсное значение сигнала. Парафазные цепи передают оба значения сигнала (рисунок 20).

Сложность парафазной шины увеличивается в два раза по сравнению с однофазной, что позволяет достичь выигрыша по быстродействию, если приемниками информации являются RS-триггеры (JK-триггеры). В данном случае парафазная шина позволяет передать информацию за один такт.

Для однофазной шины используется два такта.

В первом такте приемный регистр обнуляется (на R-входы всех триггеров регистра подаются единицы Ri:=1).

Во втором такте устанавливаются только единицы в нужных разрядах регистра (Si:= a).

П роектирование

однотактных и двухтактных (парафазных

и однофазных) цепей приема и установки

кода рассматривалось выше в примере 1

(синтез регистра на раздельных триггерах).

роектирование

однотактных и двухтактных (парафазных

и однофазных) цепей приема и установки

кода рассматривалось выше в примере 1

(синтез регистра на раздельных триггерах).

Прием информации на D-триггер с помощью однофазной цепи осуществляется за один такт.

N-разрядная шина состоит из N одноразрядных цепей.

Шины могут быть раздельными и общими. При реализации передач в системе регистров раздельными шинами каждая передача осуществляется по собственной шине, связывающей соответствующий источник с соответствующим приемником, при подаче в схему соответствующего управляющего сигнала уi. Общая шина (магистраль) – это схемное решение, в котором все возможные передачи между регистрами осуществляются по единственной шине.

Раздельные шины

Если необходимо на один регистр-приемник передать информацию с нескольких регистров-источников, то соответствующие цепи объединяются при помощи логических элементов. Пусть на регистр В может передаваться информация с регистров A1, A2, … , Ak:

y1: B(1: n):= A1(1: n);

y2: B(1: n):= A2(1: n);

… …

yk: B(1:n):= Ak(1:n).

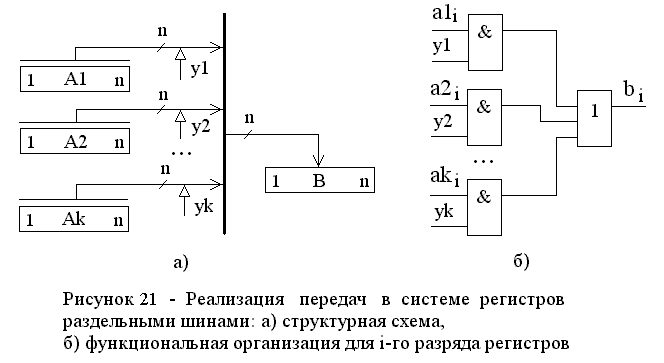

Рисунок 21,а иллюстрирует идеологию раздельной шины для осуществления указанных микроопераций. На рисунке 21,б приведена схема связей между i-ми разрядами регистров без привязки к конкретной серии микросхем.

Оценим сложность

схемы, приведенной на рисунке 21,б , по

числу входов логических элементов. Для

n-разрядных регистров она

составит

![]() ,

где k – количество

источников. В общем случае, если в системе

не один, а m приемников,

сложность схемы составит

,

где k – количество

источников. В общем случае, если в системе

не один, а m приемников,

сложность схемы составит

![]() .

Если количество передач между регистрами

.

Если количество передач между регистрами

![]() в системе достаточно велико, то реализация

этих передач раздельными шинами может

быть сравнительно дорогой. В связи с

этим появилась идея реализации всех

передач одной – общей – шиной.

в системе достаточно велико, то реализация

этих передач раздельными шинами может

быть сравнительно дорогой. В связи с

этим появилась идея реализации всех

передач одной – общей – шиной.

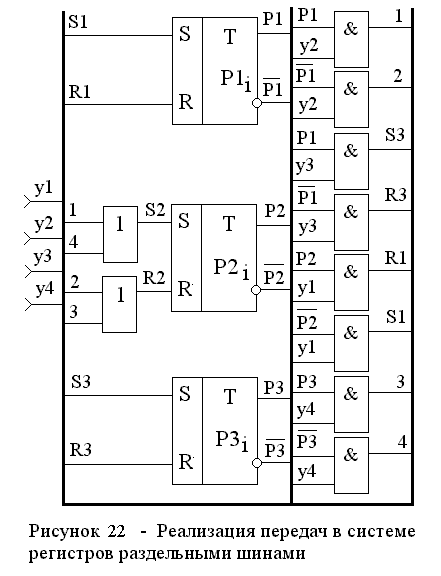

Пример: Синтезировать раздельные парафазные шины (функциональная схема i-го разряда) для осуществления следующих передач в системе из трех регистров:

![]()

Парафазные шины применяются, когда приемником является регистр, построенный на RS (JK)-триггерах для того, чтобы межрегистровые передачи могли быть осуществлены за один такт. Поэтому в схеме в качестве i-го разряда каждого регистра будет использован RS-триггер. Для осуществления прямой передачи на S-вход приемника должно быть передано прямое значение источника, домноженное на соответствующий управляющий сигнал, а на R-вход приемника – инверсное значение источника, домноженное на тот же сигнал.

Для осуществления инверсной передачи на S-вход приемника должно быть передано инверсное значение источника, домноженное на соответствующий управляющий сигнал, а на R-вход приемника – прямое значение источника, домноженное на тот же сигнал.

Функции возбуждения входов триггеров:

![]() ;

;

![]() ;

;

![]()

Функциональная схема i-го разряда раздельных шин, осуществляющих заданные передачи, приведена на рисунке 22. Схема выполнена без привязки к конкретной серии микросхем.

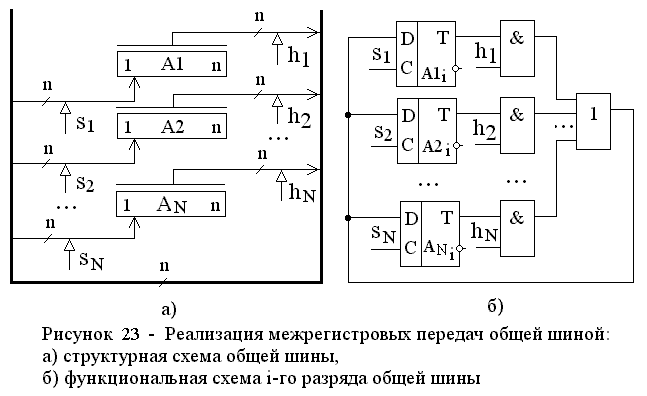

Общая шина (магистраль)

Структурная схема общей шины приведена на рисунке 23,а. Функциональная схема i-го разряда общей шины приведена на рисунке 23,б.

При осуществлении передачи Ak:=Aj через общую шину выход источника подключается ко входу общей по сигналу hj, выход общей шины подключается ко входу приемника по сигналу sk. Для осуществления указанной передачи управляющие сигналы hj и sk должны быть поданы в схему одновременно. Это значит что для осуществления любой передачи управляющий автомат должен выработать два соответствующих этой передаче унитарных кода:

![]() и

и

![]() .

То есть управление в данном случае

осуществляется унитарными управляющими

кодами. Часто на практике УА для

осуществления передачи по общей шине

вырабатывает позиционные коды номера

источника и номера приемника (управление

позиционными управляющими кодами). В

этом случае выбор источника и подключение

его ко входу общей шины осуществляется

посредством мультиплексора, подключением

нужного приемника ко входу общей шины

управляет дешифратор (рисунок 24).

.

То есть управление в данном случае

осуществляется унитарными управляющими

кодами. Часто на практике УА для

осуществления передачи по общей шине

вырабатывает позиционные коды номера

источника и номера приемника (управление

позиционными управляющими кодами). В

этом случае выбор источника и подключение

его ко входу общей шины осуществляется

посредством мультиплексора, подключением

нужного приемника ко входу общей шины

управляет дешифратор (рисунок 24).

Следует отметить, что в рассмотренных схемах общих шин (рисунки 23, 24) передаются только прямые значения с регистров-источников. Если в системе возможны передачи инверсных значений, то число источников увеличивается в общем случае в два раза (так как будут использоваться не только прямые, но и инверсные выходы триггеров). В дальнейшем под источником будем понимать номер регистра и тип передачи (прямая или инверсная).

Операционные автоматы с общими микрооперациями.

Пусть в микропрограмме встречается слово А, над которым необходимо выполнить ряд операций.

счет А:=А+1

сдвиг А:=L1(A)0

формирование кода А:=Аинв.

суммирование А:=А+С

поразрядная логика А:=АV С

дешифрация

шифрация и т.д.

Если регистров в микропрограмме много, цепи будут повторяться много раз, что усложнит схему.

Цепи выполнения микрооперации отделяются от слов и реализуются единожды.

F– множество всех операций.

F=F1 V F2 V F3 V…V FN

Fi – множество микроопераций над словом Ai.

Слова сосредоточены в запоминающей части(ЗЧ). А цепи – в комбинационной части (КЧ).

ЗЧ состоит из N регистров с одинаковой разрядностью n. N=max(n1, n2, … , nN).

Две шины нужны для выполнения двухместной операции.

Номер регистра ЗЧ, подключаемого к шине Рn определяется управляющим сигналом {yi}.

А номер регистра, подключаемого к шине Q , определяется сигналом {yiQ}.

В комбинационном преобразователе над операциями выполняется операция Fl , инициализирующаяся управляющим сигналом yl.

Xj – множество осведомительных сигналов, выдаваемых ОА.

Результат выполнения операции может быть записан на внешний регистр В или в ЗЧ по шине z при наличии сигнала yk. Также в ЗЧ может быть записана информация с внешнего регистра А при наличии сигнала ya.

yA yZ=0

Номер регистра приемнока в ЗЧ определяется сигналами {ykAz}.

A4:=F5(A1, A2)$ y1P y2Qy5 yz y4Az

Структура запоминающей части ОА с общими микрооперациями.

Логика подключения к шине P и Q может быть заменена мультиплексором, на адресные входы которого нужно подавать номер регистра источника.

ЗЧ строится на микросхемах памяти, тогда схема подключения к шинам строится следующим образом:

Структура комбинационного преобразователя.

ФК – формирователь кода позволяет получать инверсные (обратные, дополнительные) коды числа, удваивать знаковые разряды для сложения и вычитания положительных и отрицательных чисел на сумматоре. Управляется множеством сигналов {yiфк}.

КСМ – комбинационный сумматор. Если на вход КСМ подается слово, сформулированное управляющим сигналом yiconst, то КСМ осуществляется множеством управляющих сигналов { yiКСМ}.

КСДВ – комбинационный сдвигатель с двумя малоразрядными регистрами L и R для временного хранения информации выдвигаемой за разрядную сетку. Эта информация может быть использована в следующем такте. Выбор функции КСДВ осуществляется множеством сигналов { yiКСДВ}.

Z – выходной регистр. Регистр z нужен только если ЗЧ ОА реализована на одноступенчатых регистрах. Нужен чтобы разделить процессы чтения с регистра и записи в регистр, когда один и тот же регистр является источником и приемником информации. A1=f(A1,A2).

Сигналы y0фк y0ксм y0ксдв позволяют передавать информацию со входа на выход соответствующего операционного элемента без изменения.

Результат выполнения операции в комбинационном преобразователе можно представить в следующей форме:

Z=G(S(P, Ф(Q)).

Сравнение двух методов построения ОА.

По быстродействию лучше ОА с закрепленными микрооперациями на время требуемое для выборки операндов на *3, где - задержка на одном вентиле.

По стоимости ОА с общими микрооперациями дешевле, когда затраты на реализацию общих шин покрываются экономией комбинационной части.

Обобществление микроопераций целесообразно, когда микропрограмма сложная, когда требуется выполнить большой набор микроопераций.

Синтез формирователей кода (нетиповых ОЭ).

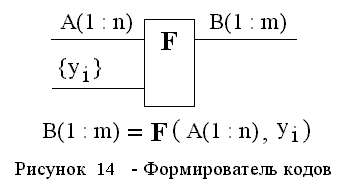

Ф ормирователь

кода (ФК) – это нетиповой ОЭ, выполняющий

набор микроопераций преобразования

входного кода А в выходной код В

в соответствии с управляющими сигналами

уi (рисунок

14).

ормирователь

кода (ФК) – это нетиповой ОЭ, выполняющий

набор микроопераций преобразования

входного кода А в выходной код В

в соответствии с управляющими сигналами

уi (рисунок

14).

ФК является комбинационной схемой.

Примером ФК является комбинационный счетчик, рассмотренный выше. Он формирует на выходе код, который на 1 больше (меньше) кода на входе. Широко используются также формирователи инверсных (обратных и дополнительных) кодов, обеспечивающих правильность выполнения операций с отрицательными числами на двоичном сумматоре [1].

Пример 4. Синтезировать формирователь кодов, выполняющий следующие микрооперации:

![]() - получение

модифицированного кода (удвоение

знакового разряда), который используется

для выявления ситуации переполнения

при сложении на двоичном сумматоре

чисел с фиксированной точкой;

- получение

модифицированного кода (удвоение

знакового разряда), который используется

для выявления ситуации переполнения

при сложении на двоичном сумматоре

чисел с фиксированной точкой;

![]() - удвоение и

инвертирование знакового разряда;

- удвоение и

инвертирование знакового разряда;

![]() - получение

модифицированного обратного кода числа;

- получение

модифицированного обратного кода числа;

![]() - сдвиг кода влево

без участия двух старших разрядов с

доопределением нулем освобождающегося

младшего разряда.

- сдвиг кода влево

без участия двух старших разрядов с

доопределением нулем освобождающегося

младшего разряда.

Заметим, что значение обратного кода числа с фиксированной точкой А(1:n) определяется значением знакового(старшего) разряда числа – A1. Если число положительное (А1=0), то обратный код числа равен его прямому коду. То же справедливо и для дополнительного кода. Если число отрицательное (А1=1), то для получения обратного кода нужно проинвертировать все разряды числа кроме знакового. Для получения дополнительного кода отрицательного числа нужно к его обратному коду прибавить единицу.

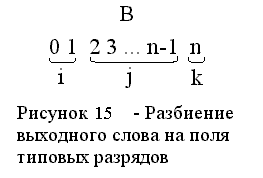

Основной подход при синтезе ФК – выделение и синтез типового разряда.

Этапы синтеза:

1) Выходное слово

разбивается на поля однородных разрядов

(т.е. разрядов, формируемых одинаково).

Для каждого поля значение любого разряда

bi

этого поля описывается одной и той же

функцией

![]() .

Для указанного примера слово B(1:n)

можно разбить на 3 поля:

.

Для указанного примера слово B(1:n)

можно разбить на 3 поля:

![]()

;

;

![]() ;

;

![]() (рисунок 15).

(рисунок 15).

2)Синтез типового разряда (построение таблицы выходов). Зависимость значений выходов ФК от значений входного кода и управляющих сигналов представлена в таблице 2.

Таблица 2

-

0

3) Получение выходных функций.

![]() ;

;

![]()

![]() ;

;

![]()

Для упрощения функций обычно стараются вынести за скобку прямые и инверсные значения текущего разряда входного кода. Тогда в скобках остаются части, общие для всех выходных разрядов соответствующей группы. Введем следующие обозначения:

![]()

Тогда

![]() ;

;

![]()

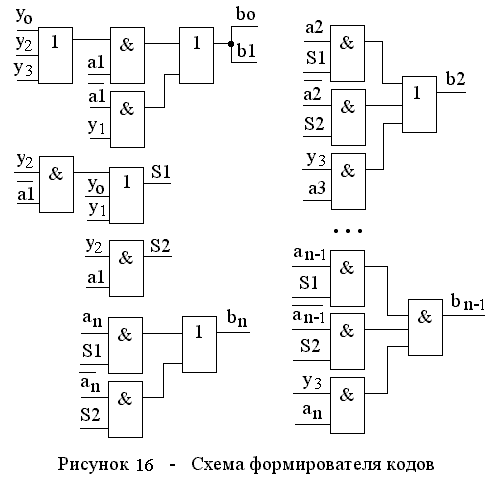

4) Реализация функций, полученных на третьем этапе проектирования. Функциональная схема формирователя кодов, выполненная без привязки к конкретной серии микросхем, представлена на рисунке 16.

При разработке ФК был применен стандартный метод синтеза ОА – синтез типового разряда методами булевой алгебры и дублирования схемы типового разряда для обеспечения требуемой разрядности операционного элемента (ОЭ).

Если набор микроопераций, выполняемых ОЭ, невелик, то его можно скомбинировать из типовых решений, приведенных в справочнике.

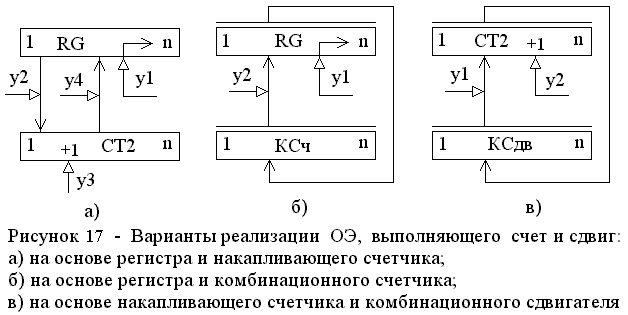

Например, нет

типового решения для ОЭ, выполняющего

микрооперации счета и сдвига. Такой

элемент может быть реализован, в

частности, путем комбинации типового

накапливающего счетчика и типового

сдвигающего регистра (рисунок 17,а).

Микрооперация сдвига

![]() реализуется

управляющим сигналом

реализуется

управляющим сигналом

![]() .

Операция счета

.

Операция счета

![]() выполняется за три такта как

последовательность микроопераций

выполняется за три такта как

последовательность микроопераций

![]() .

Операнд, а затем результат, представлен

в регистре, счетчик является вспомогательным

элементом. Недостаток схемы: счет

осуществляется за три такта. Для

преодоления этого недостатка можно

предложить схемные решения, изображенные

на рисунке 17,б, в.

.

Операнд, а затем результат, представлен

в регистре, счетчик является вспомогательным

элементом. Недостаток схемы: счет

осуществляется за три такта. Для

преодоления этого недостатка можно

предложить схемные решения, изображенные

на рисунке 17,б, в.

Примечание На рисунке 17, не показаны сигналы, инициирующие микрооперации сброса ОЭ и загрузки операнда. В реальной схеме они должны быть предусмотрены.

На рисунке 17,б

представлена схема на основе регистра

сдвига и комбинационного счетчика.

Операнд, а затем результат, находится

в регистре. Для исполнения микрооперации

сдвига (

)

используется режим сдвига регистра, а

для реализации микрооперации счета (![]() )

– режим параллельной загрузки регистра.

)

– режим параллельной загрузки регистра.

На рисунке 17,в представлена схема на основе накапливающего счетчика и комбинационного сдвигателя. Операнд, а затем результат, находится в счетчике. Для исполнения микрооперации сдвига ( ) используется режим параллельной загрузки счетчика, а для реализации микрооперации счета ( ) – режим счета на увеличение.