- •Учебно-методическое пособие исследование цифровых схем в лабораторном комплексе на базе настольной рабочей станции ni elvis II

- •1. Введение 1

- •2. Особенности построения и функционирования лабораторного комплекса на базе настольной рабочей станции ni elvis II 14

- •3. Принципы работы и инструкции по взаимодействию с виртуальными и реальными приборами 32

- •4. Методические указания по выполнению лабораторных работ по дисциплине «Схемотехника» 61

- •5. Методические рекомендации по разработке курсового проекта с использованием среды ni Multisim и рабочей станции ni elvis II 136

- •1.Введение

- •1.1.Лабораторный комплекс для исследования цифровых схем как измерительная система и устройство сбора данных

- •1.2.Структура измерительной системы в методологии компании National Instruments (ni)

- •1.3.О принципах функционирования осциллографов

- •1.4.О частоте дискретизации

- •1.5.Типы источников сигналов и схемы измерений

- •1.4. Плавающий источник сигнала

- •2.Особенности построения и функционирования лабораторного комплекса на базе настольной рабочей станции ni elvis II

- •2.1.Общая характеристика и структура лабораторного комплекса

- •2.2.Аппаратная часть комплекса

- •2.3.Включение рабочей станции

- •3.Принципы работы и инструкции по взаимодействию с виртуальными и реальными приборами

- •3.1.Функциональный генератор (Functional Generator, fGen) – fgen.Exe

- •Порядок использования функционального генератора

- •3.2.Регулируемые источники питания (Variable Power Supplies, vps) – vps.Exe

- •Порядок использования регулируемых источников питания

- •3.3.Цифровой мультиметр (Digital MultiMeter, dmm) – dmm.Exe

- •Порядок использования цифрового мультиметра

- •3.4.Осциллографы, используемые в лаборатории «Схемотехника»

- •3.5.Встроенный цифровой осциллограф рабочей станции (ni scope) – scope.Exe

- •Порядок использования встроенного осциллографа ni scope

- •3.6.Модульный цифровой осциллограф ni pci-5114

- •Порядок использования

- •Курсорные вычисления

- •3.7.Аналоговый осциллограф с1-99

- •Порядок использования осциллографа с1-99

- •3.8.Краткие сведения о платах ni pci-6533 и cb-68lpr

- •3.9.Счетчики/таймеры (Counters/Timers)

- •3.10.Конфликты ресурсов

- •4.Методические указания по выполнению лабораторных работ по дисциплине «Схемотехника»

- •4.1.Лабораторная работа 1. Изучение рабочей станции, работы функционального генератора и осциллографов

- •Порядок выполнения работы

- •Варианты заданий

- •4.2.Лабораторная работа 2. Исследование работы формирователя логического сигнала 1-го типа

- •Варианты заданий

- •Порядок выполнения работы

- •1. Получение передаточной характеристики (хвв) для ненагруженной схемы (Рис. 4 .29).

- •4. Измерение динамических параметров сигнала при отсутствии нагрузки на выходе схемы (Рис. 4 .32).

- •5. Получение зависимости динамических параметров сигнала на выходе схемы от величины емкостной нагрузки (Рис. 4 .33).

- •Содержание отчета

- •Задание по уирс

- •4.3.Лабораторная работа 3. Исследование работы формирователя логического сигнала 2-го типа

- •Варианты заданий

- •Порядок выполнения работы

- •Содержание отчета

- •Задание по уирс

- •4.4.Лабораторная работа 4. Исследование работы инвертора ттл

- •Порядок выполнения работы

- •1. Получение передаточной характеристики (хвв) для ненагруженной схемы.

- •Содержание отчета

- •Варианты заданий

- •Задание по уирс

- •4.5.Лабораторная работа 5. Исследование работы инвертора кмоп

- •Краткое описание принципов работы элементов кмоп

- •Порядок выполнения работы

- •Содержание отчета

- •Задание по уирс

- •4.6.Лабораторная работа 6. Изучение виртуального датчика временных последовательностей (виртуального двп)

- •Порядок работы с виртуальным двп

- •4.7.Лабораторная работа 7. Изучение работы синхронных rs- и d-триггеров

- •Порядок выполнения работы

- •Содержание отчета

- •4.8.Лабораторная работа 8. Изучение работы мультиплексоров

- •Порядок выполнения работы

- •Содержание отчета

- •4.9.Лабораторная работа 9. Изучение работы регистров (сдвигателей)

- •Порядок выполнения работы

- •Содержание отчета

- •4.10.Лабораторная работа 10. Изучение работы счетчиков

- •Варианты заданий для к155ие6

- •Варианты заданий для к155ие7

- •Порядок выполнения работы

- •Содержание отчета

- •5.Методические рекомендации по разработке курсового проекта с использованием среды ni Multisim и рабочей станции ni elvis II

- •Порядок моделирования схем

- •Пример разработки курсового проекта

- •Литература, ссылки на источники информации по рабочей станции, дополнительному оборудованию и программному обеспечению

Содержание отчета

титульный лист

предварительная подготовка

по части 8.1: временные диаграммы входных и выходных сигналов, осциллограмма одного из выходов счетчика, осциллограмма сигнала переноса, микровременная диаграмма счетчика

по части 8.2 - для счетчика К155ИЕ7 - аналогично части 8.1

по части 8.3 - временные диаграммы управляющих и выходных сигналов

5.Методические рекомендации по разработке курсового проекта с использованием среды ni Multisim и рабочей станции ni elvis II

Для разработки и моделирования работы курсового проекта предлагается воспользоваться средой NI Multisim, интерактивным симулятором схем, а для отладки – рабочей станцией ELVIS. В среде осуществляется разработка схемы и моделирование ее работы с использованием обширной библиотеки компонентов и виртуальных приборов (встроенных симуляторов измерительных приборов).

NI Multisim входит в пакет приложений Circuit Design Suite (CDS) от компании National Instruments Electronics Workbench Group, разработанных для ОС Windows.

Общие характеристики NI Multisim 11.044:

более 17000 активных и пассивных электронных компонентов, которые можно использовать при моделировании работы схемы,

более 90 различных символов для выводов компонентов,

моделирование с использованием SPICE,

полная интеграция с NI Ultiboard,

интеграция с LabVIEW,

контроль ошибок в принципиальных схемах.

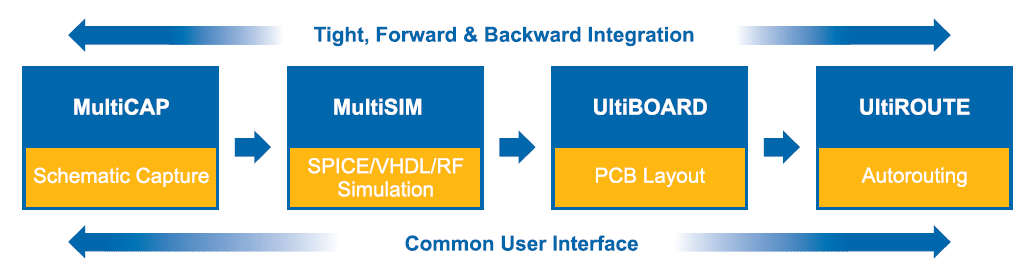

На Рис. 5 .59 показана структура взаимодействия модулей CDS (редакция официального руководства к 9 версии).

Рис.

5.59. Взаимодействие

модулей CDS

Рис.

5.59. Взаимодействие

модулей CDS

Порядок моделирования схем

Перед моделированием курсового проекта в приложении NI Multisim составьте принципиальную схему.

Запустите приложение NI Multisim (Пуск-Все программы-National Instruments-Circuit Design Suite-Multisim).

Расположите компоненты, используемые в вашем курсовом проекте45, в рабочем пространстве и соедините их между собой.

Расположите в рабочем пространстве требуемые устройства измерения (осциллографы, мультиметр) и соедините их выводы с входом и выходом схемы, нужными промежуточными точками. Не забывайте соединять один из выводов осциллографа с общей точкой (землей).

Откройте окна устройств двойным кликом по пиктограмме устройства.

Нажмите кнопку «Пуск». Если при соединении компонентов не было допущено ошибок, моделирование работы схемы будет проходить успешно. В статусной строке можно наблюдать время от начала моделирования, в окнах приборов – значения сигналов.

Пример разработки курсового проекта

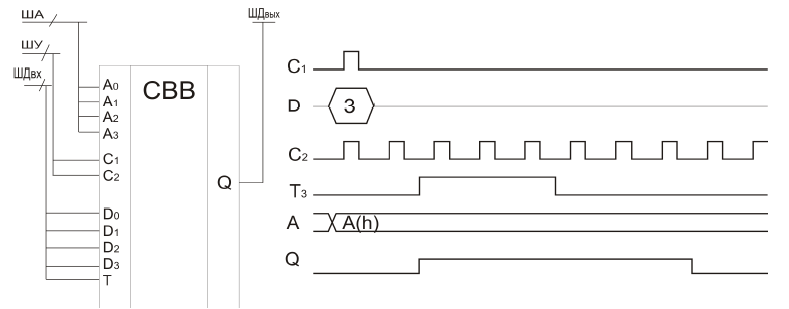

Задание: спроектировать схему выдержки времени (СВВ), обеспечивающую задержку сигнала на заданную величину (Рис. 5 .60).

Рис. 5.60. Функциональная схема и макровременная диаграмма

На входы D0-D3 по синхросигналу С1 поступает четырёхразрядный код D. При поступлении сигнала Т на выходе Q также появляется сигнал, однако после окончания Т на выходе Q сигнал продолжается некоторое количество тактов, определяемое принятым ранее числом D.

На временной диаграмме (Рис. 5 .60. Функциональная схема и макровременная диаграмма Рис. 5 .60) показан пример, когда принимается число D=3 и после окончания Т сигнал Q оканчивается через 3 такта. Адрес устройства ← A(h).

Технические характеристики устройства:

система элементов – К155.

длительность сигналов С1,С2 - 1 мкс.

все выходы (кроме Q) сопрягаются со схемами К155.

параметры сигнала Q:

- при I0вых = 22мА, U0≤2,5 В

- при I1вых = 1мА, U1≥7 В

Задание для УИРС

Смонтировать и отладить на учебной плате устройство СВВ и ФЛС.

Исследовать ФЛС

снять характеристики (ХВВ, входную, выходную )

снять совмещённые осциллограммы Uвх, Uвых

исследовать влияние помехоустойчивости при различной величине нагрузки (для U1вых)

Исследовать СВВ

снять осциллограммы в узловых точках

исследовать схемы, если повторно (пока Q=1) придёт сигнал Т.

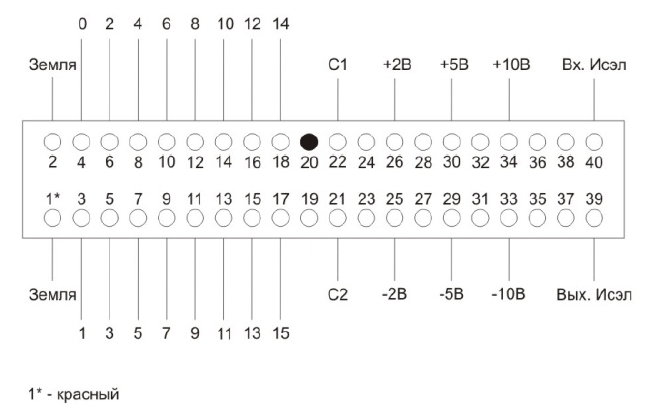

На Рис. 5 .61 представлено назначение выводов разъема стенда ДВП. Для подключения и отладки курсового проекта использовался ATA (IDE) шлейф. Как видно из рисунка, была возможность подключения к 16 информационным линиям, питанию ИС, Епитания и Ебазы для работы ФЛС, общему выводу, двум синхросигналам С1 и С2, а также входу и выходу стенда ИСЭЛ, что позволяло определить нагрузочные характеристики.

Рис. 5.61. Назначение выводов разъема стенда ДВП

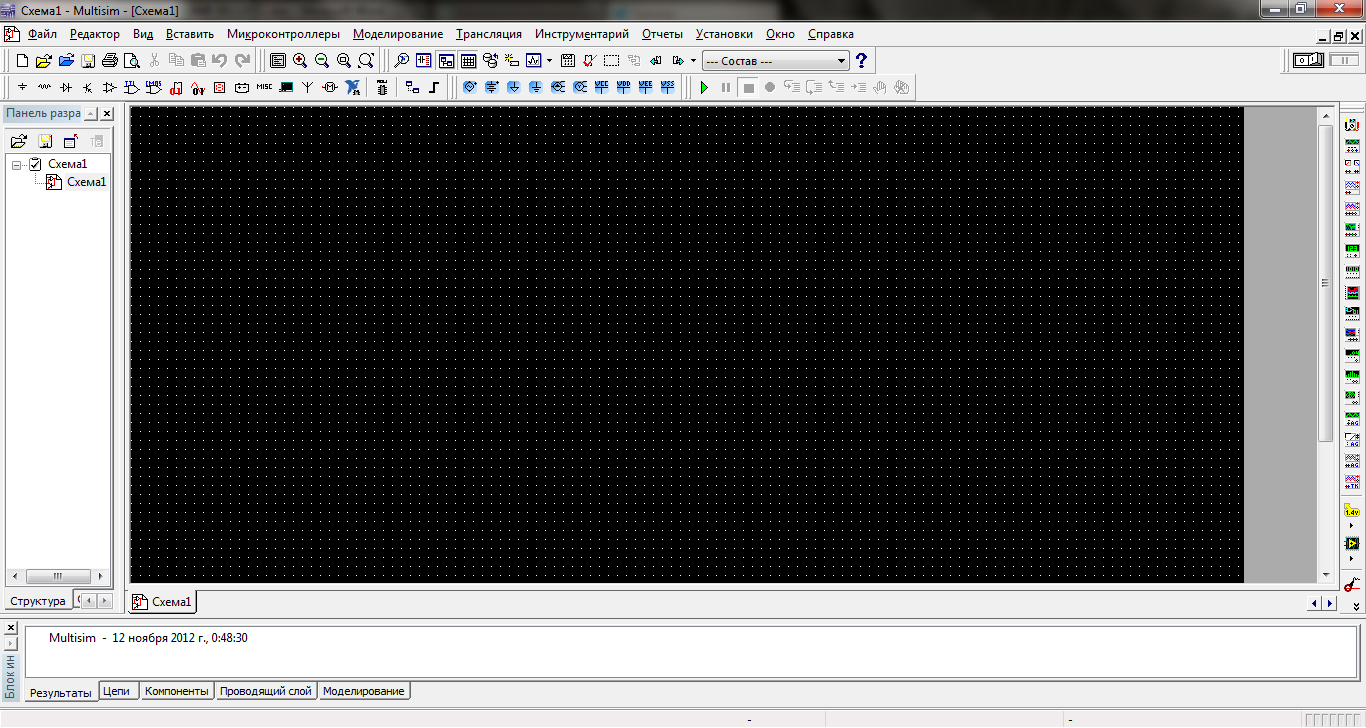

После разработки принципиальной схемы на бумаге (рис…) и визуальной проверки ее преподавателем можно приступить к этапу разработки с использованием САПР. Это позволяет промоделировать работу схемы перед сборкой прототипа, что уменьшает временные затраты на отладку. Для разработки проекта предлагается использовать среду NI Multisim, скриншот окна которой представлен на Рис. 5 .62.

Рис. 5.62. Скриншот окна NI Multisim 11.0

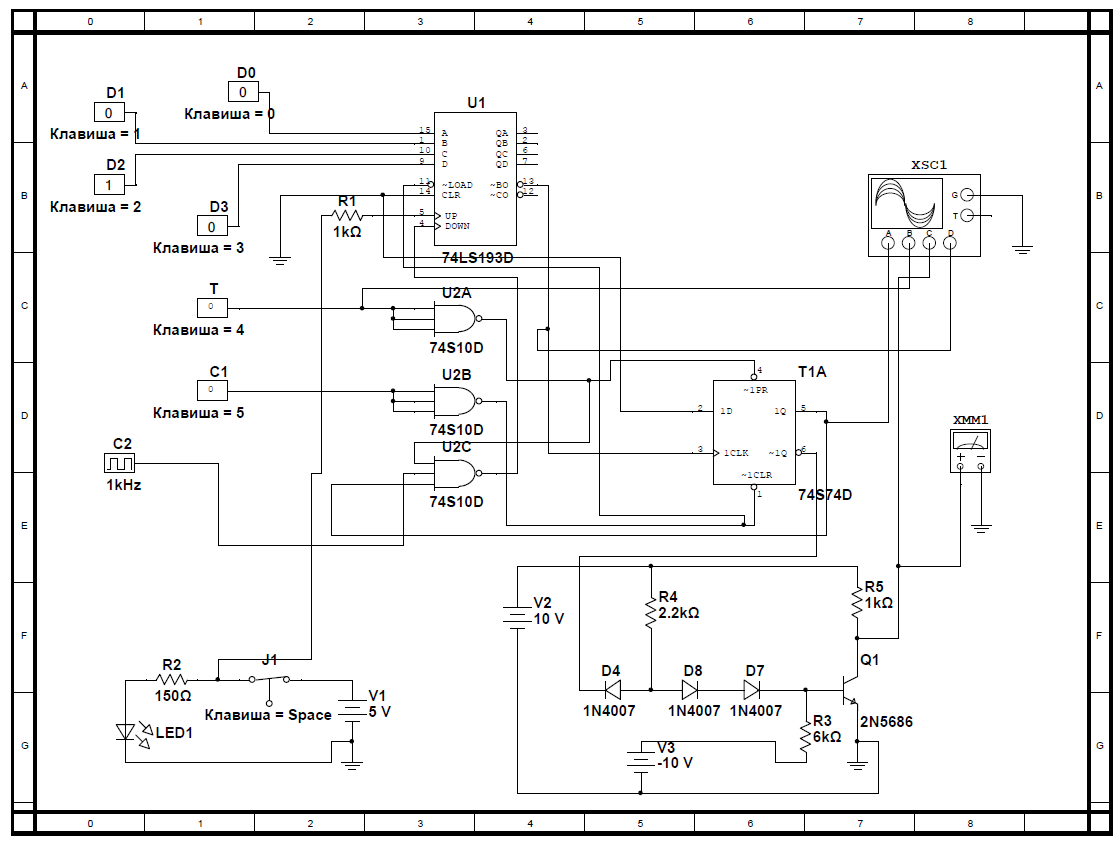

На Рис. 5 .63 – вид распечатанного из среды чертежа схемы. Обратите внимание на обозначения, выбор стандарта отображения ANSI/DIN осуществляется в меню Установки-Общие установки-Компоненты.

Рис. 5.63. Вид распечатанной принципиальной схемы