- •1.1. Память и процессор

- •1.2. Распределение адресного пространства

- •1.3. Регистры процессора

- •1.4. Сегментная структура программ

- •1.5. Стек

- •1.6. Система прерываний

- •1.7. Система ввода-вывода

- •Разница между директивами и командами Ассемблера

- •Описание сегмента — директива segment

- •Директива группирования сегментов Group

- •Директива Assume

- •Стандартные модели памяти

- •Директива model

- •Директивы упрощенного описания сегментов

- •Описание процедур

- •Описание внешних ссылок

- •Директива описания общих имен public

- •Директива описания внешних имен extrn

- •Xchg (eXcHanGe) Обмен

- •Xadd назначение,источник — обмен местами и сложение.

- •Команды условного перехода и регистр ecx/cx

- •Аппаратная реализация Кэш центрального процессора

- •Уровни кэша

- •Ассоциативность кэша

Ассоциативность кэша

Одна из фундаментальных характеристик кэш-памяти — уровень ассоциативности — отображает её логическую сегментацию которая вызвана тем, что последовательный перебор всех строк кэша в поисках необходимых данных потребовал бы десятков тактов и свёл бы на нет весь выигрыш от использования встроенной в ЦП памяти. Поэтому ячейки ОЗУ жёстко привязываются к строкам кэш-памяти (в каждой строке могут быть данные из фиксированного набора адресов), что значительно сокращает время поиска.

При одинаковом объёме кэша, схема с большей ассоциативностью будет наименее быстрой, но наиболее эффективной (после четырёхпотоковой реализации, прирост «удельной эффективности» на один поток растет мало).

Конве́йер — способ организации вычислений, используемый в современных процессорах и контроллерах с целью повышения их производительности (увеличения числа инструкций, выполняемых в единицу времени), технология, используемая при разработке компьютеров и других цифровых электронных устройств.

Идея заключается в разделении обработки компьютерной инструкции на последовательность независимых стадий с сохранением результатов в конце каждой стадии. Это позволяет управляющим цепям процессора получать инструкции со скоростью самой медленной стадии обработки, однако при этом намного быстрее, чем при выполнении эксклюзивной полной обработки каждой инструкции от начала до конца.

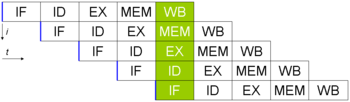

Простой пятиуровневый конвейер в RISC-процессорах

На иллюстрации справа показан простой пятиуровневый конвейер в RISC-процессорах. Здесь:

IF (англ. Instruction Fetch) — получение инструкции,

ID (англ. Instruction Decode) — раскодирование инструкции,

EX (англ. Execute) — выполнение,

MEM (англ. Memory access) — доступ к памяти,

WB (англ. Register write back) — запись в регистр.

Вертикальная ось — последовательные независимые инструкции, горизонтальная — время. Зелёная колонка описывает состояние процессора в один момент времени, в ней самая ранняя, верхняя инструкция уже находится в состоянии записи в регистр, а самая последняя, нижняя инструкция только в процессе чтения.

СПИСОК РЕКОМЕНДОВАННОЙ ЛИТЕРАТУРЫ

Поворознюк А.И – Архитектура комп'ютера/ А.И Поворознюк. – Х: Торнадо, 2004. – 355 с.

Гук М. Інтерфейси РС/М. Гук. – СПб.: Питер, 2000. – 418 с.

Танненбаум Е. Архітектура комп'ютера. 5 видання/ Е. Таненбаум. – СПб.: Питер, 2011. – 844 с.

Финогенов К.Г. Основы языка Ассемблера. /К.Г. Финогенов. — М.: Радио и связь, 2000. — 288 с.: ил.

Голубь Н.Г. Искусство программирования на Ассемблере/ Н.Г. Голубь.- М:DiaSoft, 2002. – 656 с.