- •Оглавление

- •Задание

- •1. Реализация усд на принципах схемной логики.

- •1.1 Структурная схема и состав усд

- •1.2 Разработка блока выработки адреса зу

- •1.3 Разработка блока выработки адресов каналов коммутатора.

- •1.4 Синтез управляющего устройства

- •2. Составление полной схемы усд.

- •3. Оценка быстродействия.

- •4. Список использованной литературы.

МИНИСТЕРСТВО РОССИЙСКОЙ ФЕДЕРАЦИИ ПО СВЯЗИ И ИНФОРМАТИЗАЦИИ

Московский Технический Университет Связи и Информатики

Кафедра вычислительной техники и управляющих систем

Курсовая работа

УСТРОЙСТВО СБОРА ДАННЫХ

По дисциплине

ВЫЧИСЛИТЕЛЬНАЯ ТЕХНИКА И ИНФОРМАЦИОННЫЕ ТЕХНОЛОГИИ

Вариант 18

Выполнила студентка

группы СС0601

Никифорова А.П.

Москва 2009

Оглавление

Оглавление……………………………………………………………………………………………………….2

Задание……………………………………………………………………………………………………......….3

1. Реализация УСД на принципах схемной логики…………………………………………4

1.1 Структурная схема и состав УСД ………………………………………………………………4

1.2 Разработка блока выработки адреса ЗУ…………………………………………………..5

1.3 Разработка блока выработки адресов каналов коммутатора…………………6

1.4 Синтез управляющего устройства…………………………………………………………….7

Общая структурная схема УУ и принцип его работы………………………………7

Описание работы УСД………………………………………………………………………………8

Блок-схема алгоритма функционирования ЦУ в микрооперациях и микрокомандах………………………………………………………………………………..………………..9

Построение графа функционирования УСД…………………………………………..11

Этап структурного синтеза УУ…………………………………………………………………12

2. Составление полной схемы УСД ………………………………………………………………..16

3. Оценка быстродействия………………………………………………………………………………17

4. Список используемой литературы……………………………………………………………..18

Задание

Спроектировать устройство сбора данных (АЦП). Имеется F аналоговых информационных каналов. Необходимо, опрашивая их, получаемые из каналов аналоговые величины с помощью АЦП преобразовать в цифровую форму (в двоичные слова стандартной длины 1 байт=8 бит) и помещать в последовательные ячейки некоторой области оперативного запоминающего устройства (ОЗУ), начиная с ячейки, имеющий адрес G.

Цифровая процессорная система, фрагментом которой является проектируемое УСД, в своем составе имеет ОЗУ емкостью Q с форматом адресного слова до двух байт в зависимости от Q.

Синхронизация работы процессорного устройства осуществляется от генератора тактовых импульсов (ГТИ). Частота синхроимпульсов f=500 кГц.

Требуется:

1. Исходя из задания, разработать ОЗУ цифровой системы.

2. Разработать системы формирования адресов ячеек ОЗУ и номеров опрашиваемых каналов.

3. Реализовать УСД в виде процессорного устройства, построенного на принципах схемной логики, и привести его функциональную схему.

4. Синтезировать схему управляющего устройства.

5. Составить полную электрическую схему УСД.

6. Оценить быстродействие УСД.

Исходные данные:

Количество опрашиваемых каналов F10=11

Емкость памяти Q=2048х8

Начальный адрес ячейки памяти G16=00А5

Двухразрядные коды состояний управляющего устройства:

а0=01; а1=00; а2=11; а3=10

Порядок опроса каналов: 5, 3, 11, 10, 8, 9, 7, 4, 6, 2, 1

1. Реализация усд на принципах схемной логики.

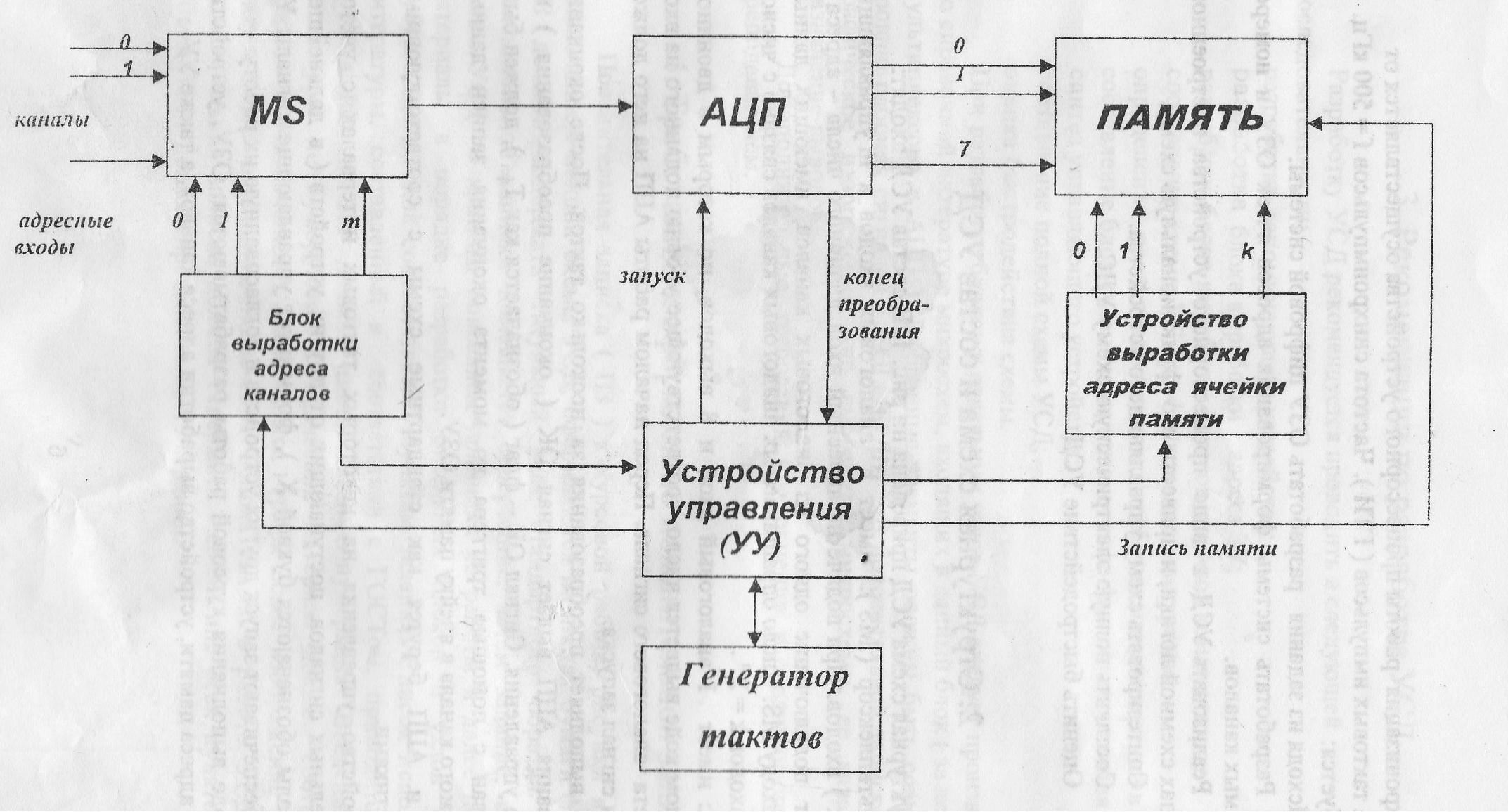

1.1 Структурная схема и состав усд

рисунок 1

В состав УСД входят:

Мультиплексор

(MS):

имеет F

аналоговых входов и m

управляющих (адресных) входов. При подаче

на адресный вход двоичного числа –

адреса – происходит подключение одного

из аналоговых каналов, имеющих данный

адрес, к выходу MS.

Число опрашиваемых аналоговых каналов

связано с числом адресных входов K= .

.

АЦП: имеет 1 аналоговый вход и 8 выходов, по которым в двоичном параллельном коде выдается число, соответствующее уровню поданного на вход АЦП отсчета аналогового сигнала. Перед началом работы АЦП на него должен быть подан сигнал запуска.

АЦП выполняет преобразование за несколько тактов. После окончания преобразования АЦП выдает сигнал ОК (окончание преобразования) на устройство управления. Сигнал ОК – флаг (обозначается так Тфл), должен быть зафиксирован с помощью триггера до момента окончания записи данных опрашиваемого канала в ячейку памяти ОЗУ.

MS и АЦП берутся как стандартные схемы с соответствующими характеристиками.

Устройство управления на некоторых тактовых интервалах с учетом осведомительных сигналов, поступающих от других устройств (в дальнейшем такие сигналы обозначаются буквой Хi), формирует управляющие сигналы Yn, которые обеспечивают запуск других устройств и согласованную их работу.