- •Двнз «Чернівецький індустріальний коледж» архітектура комп’ютерів

- •Чернівці,

- •1.Історія розвитку обчислювальної техніки

- •2. Поняття про архітектуру еом. Принцип функціонування еом

- •38. Процесор векторного комп'ютера.

- •47. Функції арифметико-логічного пристрою. Способи обробки даних в арифметико-логічному пристрої

- •63. Частково-асоціативне відображення

- •82. Універсальна послідовна шина usb

- •1.Історія розвитку обчислювальної техніки

- •Покоління процесорів x86

- •Поняття архітектури і структурної організації комп’ютера

- •2. Поняття про архітектуру еом. Принцип функціонування еом Структура й принципи функціонування еом

- •3. Склад і призначення основних блоків

- •4. Архітектурні принципи Джона фон Неймана. Ненейманівські архітектури комп'ютерів

- •5. Апаратні і програмні засоби. Класифікація еом

- •Стандартні додатки Windows

- •Службові програми

- •Методи класифікації комп'ютерів.

- •Класифікація за призначенням

- •Великі еом (Main Frame)

- •МікроЕом

- •Персональні комп'ютери

- •Класифікація по рівню спеціалізації

- •Класифікація за розміром

- •Класифікація за сумісністю

- •6. Основні характеристики еом. Пк, особливості, класифікація, основні характеристики Основні характеристики пк

- •7. Персональні комп'ютери

- •8. Робочі станції. Багатотермінальні системи. Сервери

- •9. Кластерні комп'ютерні системи.

- •10. Суперкомп'ютери. Мікроконтролери. Спеціалізовані комп'ютери

- •11. Позиційні системи числення. Двійкові, вісімкові та шістнадцяткові числа

- •Двійкові, вісімкові та шістнадцяткові числа

- •12. Переведення чисел із системи числення з основою k у десяткову систему

- •13. Переведення чисел із десяткової системи у систему числення з основою k.

- •14. Прямий код. Обернений код. Доповняльний код. Способи представлення чисел

- •15. Числа з фіксованою комою. Числа із рухомою комою

- •16. Арифметичні операції. Ділення двійкових чисел

- •17. Арифметичні операції над двійковими числами у форматі з рухомою комою

- •18. Стандарт іеее-754. Розширений двійково-кодований десятковий код обміну ebcdic

- •19. Кодування алфавітно-цифрової інформації. Двійково-кодовані десяткові числа.

- •20. Американський стандартний код інформаційного обміну ascii. Стандарт кодування символів Unicode.

- •21. Кодування та виконання команд в комп'ютері

- •22. Виконання команд на рівні регістрів процессора.

- •23. Конвеєрне виконання команд

- •24. Класифікація архітектури комп'ютера за типом адресованої пам'яті.

- •25. Безпосередня адресація. Пряма адресація. Непряма адресація.

- •26. Відносна адресація. Базова адресація. Індексна адресація.

- •27. Сторінкова адресація. Неявна адресація. Стекова адресація. Використання стекової адресації.

- •28. Одношинна структура процесора.

- •29. Основні операції процесора. Вибірка слова з пам'яті. Запам'ятовування слова в пам'яті. Обмін даними між регістрами.

- •30. Багатошинна структура процесора.

- •31. Приклади виконання операцій в процесорі. Виконання операції додавання двох чисел.

- •32. Вимоги до процесора комп'ютера з простою системою команд. Базові принципи побудови процесора комп'ютера з простою системою команд.

- •33. Взаємодія процесора з пам'яттю в комп'ютері з простою системою команд.

- •34. Виконання команд в процесорі комп'ютера з простою системою команд. Фаза вибирання команди. Фаза декодування команди.

- •35. Конвеєрний процессор.

- •36. Мікродії ярусів конвеєрного процесора.

- •37. Суперскалярні процесори.

- •38. Процесор векторного комп'ютера.

- •39. Класифікація архітектури комп'ютера за рівнем суміщення опрацювання команд та даних.

- •40. Логічні операції.

- •1. Формальна логіка

- •2. Математична логіка

- •3. Програмування

- •41. Операція заперечення. Логічна 1. Логічне або. Виключне або.

- •42. Операції зсуву.

- •43. Операції відношення.

- •44. Арифметичні операції.

- •45. Операції обчислення елементарних функцій.

- •46. Операції перетворення даних.

- •47. Функції арифметико-логічного пристрою. Способи обробки даних в арифметико-логічному пристрої.

- •48. Елементарні операції арифметико-логічного пристрою.

- •49. Складні операції арифметико-логічного пристрою.

- •50. Структура арифметико-логічного пристрою.

- •51. Функції та методи побудови пристрою керування.

- •52. Пристрій керування з жорсткою логікою.

- •53. Пристрій керування на основі таблиць станів.

- •54. Пристрій мікропрограмного керування.

- •55. Порівняння пристроїв керування з жорсткою логікою та пристроїв мікропрограмного керування.

- •56 Ієрархічна організація пам'яті комп'ютера

- •57. Принцип ієрархічної організації пам'яті. Характеристики ефективності ієрархічної організації пам'яті

- •58. Кеш пам'ять в складі комп'ютера. Порядок взаємодії процесора і основної пам'яті через кеш пам'ять

- •59. Забезпечення ідентичності вмісту блоків кеш пам'яті і основної пам'яті

- •60. Функція відображення. Типи функцій відображення

- •61. Повністю асоціативне відображення

- •62. Пряме відображення

- •63. Частково-асоціативне відображення

- •64. Порядок заміщення блоків в кеш пам'яті з асоціативним відображенням

- •65. Підвищення ефективності кеш пам'яті

- •66. Статичний та динамічний розподіл пам'яті. Розподіл основної пам'яті за допомогою базових адрес

- •67. Віртуальна пам'ять. Сторінкова організація пам'яті

- •68. Основні правила сторінкової організації пам'яті. Реалізація сторінкової організації пам'яті

- •69. Апаратна реалізація сторінкової таблиці

- •70. Сегментна організація віртуальної пам'яті

- •71. Захист пам'яті від несанкціонованих звернень

- •72. Захист пам'яті за значеннями ключів

- •73. Кільцева схема захисту пам'яті

- •74. Архітектура системної плати

- •75. Синхронізація

- •76. Система шин

- •77. Особливості роботи шини

- •78. Характеристики шин пк

- •79. Шина pcmcia, vbl

- •80. Шина pci

- •82. Універсальна послідовна шина usb

- •83.Типи передач і формати інформації що передається

- •84. Шина scsi

- •85. Адресація пристроїв і передача даних

- •86. Система команд

- •87. Конфігурування пристроїв scsi

- •88. Ігровий адаптер Game-порт

- •89. Відеоадаптери

- •90. Послідовний інтерфейс. Сом-порт

- •91. Програмна модель сом-порта

- •92. Програмування послідовного зв’язку

- •93. Ініціалізація послідовного порта. Передача і прийом даних

- •95. Паралельний інтерфейс lpt-порт. Стандартний режим spp

- •96. Режим epp

- •97. Режим ecp

- •98. Узгодження режимів

- •99. Приклад програмування

- •100. Клавіатура

- •101. Під'єднання зовнішніх пристроїв до комп'ютера

- •102. Розпізнавання пристроїв введення-виведення

- •103. Методи керування введенням-виведенням

- •104. Програмно-кероване введення-виведення.

- •105. Система переривання програм та організація введення-виведення за перериваннями

- •106. Прямий доступ до пам'яті. Введення-виведення під керуванням периферійних процесорів

- •107. Мультиплексний та селекторний канали введення-виведення

- •108. Використання принципів паралельної обробки інформації в архітектурі комп'ютера

- •109. Вибір кількості процесорів в багатопроцесорній системі

- •110. Багатопотокова обробка інформації. Окр

- •111. Класифікація Шора. Класифікація Фліна

- •112. Типи архітектур систем окмд. Типи архітектур систем мкмд

- •113.Організація комп'ютерних систем із спільною пам'яттю

- •114. Організація комп'ютерних систем із розподіленою пам'яттю

- •115. Комунікаційні мережі багатопроцесорних систем

110. Багатопотокова обробка інформації. Окр

Звичайно, перераховані вище підходи до підвищення продуктивності комп’ютерних систем, використовуючи паралельну обробку інформації, не виключають необхідність підвищення продуктивності однопроцесорних систем шляхом нарощування ресурсів процесора, наприклад, шляхом нарощування ємності кеш пам’яті та добавлення нових операційних пристроїв. Хоча зрозуміло, що це тягне за собою зростання кількості транзисторів та площі кристалу, ускладнення процесора, і відповідно, вартості.

Іншим підходом є підвищення ефективності використання наявних ресурсів комп’ютерних систем з одним та декількома процесорами. Існує декілька дешевших, ніж масове розпаралелювання варіантів, які також дозволяють прискорити обчислення, а саме:

Багатопроцесорність на одному кристалі (Chip Multiprocessing). Два процесорні ядра фізично розташовані на одному кристалі із використанням спільної або розподіленої кеш пам’яті. Природно, що розмір кристала отримують досить великим, що є причиною великої вартості цього кристала. В багатопроцесорній системі можуть функціонувати декілька таких кристалів.

Багатопотокова обробка з квантуванням часу (Time-Slice Multithreading). Процесор перемикають поміж програмними потоками через фіксовані проміжки часу. Накладні витрати часом виходять досить значними, особливо якщо який-небудь процес знаходиться в стані очікування

Багатопотокова обробка з перемиканням за подіями (Switch-on-Event Multithreading). Перемикання задач при наявності тривалих пауз, наприклад “невлучень” до кеш пам’яті, велике число яких притаманне серверним аплікаціям. Тут процес, що чекає на завантаження даних з порівняно повільної основної пам’яті до кеш пам’яті, пригальмовують, вивільняючи тим самим ресурси процесора на користь інших процесів. Проте багатопотокова обробка з перемиканням за подіями, як і багатопотокова обробка з квантуванням часу, не завжди дозволяє досягти оптимального використання ресурсів процесора, зокрема через помилки в передбаченні розгалужень, існуючі залежності поміж командами тощо

Одночасна багатопотокова обробка (Simultaneous Multithreading). Тут програмні потоки виконуються на одному процесорі “одночасно”, тобто без переключення між ними. Ресурси процесора розподіляються динамічно, за принципом “не використовуєш - віддай іншому”

Одночасна багатопотокова обробка покладена в основу технології гіперпотокової обробки (Hyper-Threading) фірми Intel, яку розглянемо детальніше

Багатопотокові обчислення використовуються не лише в серверах, де багатопотоко- вість існує первинно, але і в робочих станціях і настільних персональних комп’ютерах. Потоки можуть відноситися як до однієї, так і до різних прикладних програм, але майже завжди активних потоків більше від одного (аби переконатися в цьому, достатньо у Windows 2000/ХР відчинити Task Manager та увімкнути відбиття ним числа виконуваних потоків). Разом з тим відомо, що стандартний процесор може одночасно опрацьовувати лише один з декількох існуючих потоків, тому і змушений постійно перемикатися поміж цими потоками

Технологію гіперпотокової обробки реалізовано в процесорі Intel Xeon МР (Foster МР), на якому і відбувалося дослідження ефективності цієї технології. Процесор Xeon МР використовує притаманне Pentium 4 ядро Willamette, містить 256 КВ кеш пам’яті другого рівня L2, 512 КВ кеш пам’яті третього рівня L3, та підтримує функціонування в чотири- процесорних конфігураціях. Підтримка технології гіперпотокової обробки також присутня у процесорі для робочих станцій Intel Xeon (ядро Prestonia, 512 KB кеш пам’яті другого рівня L2), що поступив на ринок дещо раніше від процесора Xeon МР. Далі розглянемо можливості технології гіперпотокової обробки на прикладі саме процесора Intel Xeon.

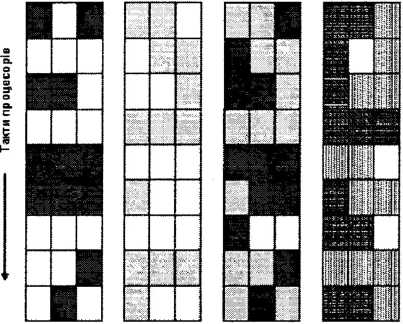

На рис. 12.5 а показано завантаженість процесорів комп’ютерної системи, яка складається з двох суперскалярних процесорів. Кожен процесор може виконувати по 3 команди в одному циклі. Незадіяні (позначено білим) прямокутники свідчать про неоптимальну утилізацію системних ресурсів В той же ж час технологія гіперпотокової обробки не лише дозволяє опрацьовувати паралельно декілька потоків, але і зменшує при цьому наявне число незадіяних виконавчих часових інтервалів. На рис. 12.5 b показано завантаженість процесорів комп’ютерної системи, яка також складається з двох фізичних процесорів, та в якій використовується технологія гіперпотокової обробки. Кожен з процесорів тут опрацьовує по два потоки інформації, що дозволило наблизити систему до пікової продуктивності.

a b

Рис.

12.5. Завантаженість процесорів комп'ютерної

системи, яка складається з двох

суперскалярних процесорів без

використання технологіїгіперпотокової

обробки (а) та з використанням технології

гіперпотокової обробки (Ь)

Технологія гіперпотокової обробки ґрунтується на тому, що одночасно тільки частина ресурсів процесора використовується на опрацювання програмного коду. Не використовувані ресурси можна завантажити іншою роботою, наприклад, задіяти на паралельне виконання ще одного додатку (або іншого потоку з того ж додатку). Заради цього в одному фізичному процесорі Intel Xeon формують два логічні процесори (LP - Logical Processor), що поділяють поміж собою обчислювальні ресурси єдиного фізичного процесора. Операційна система та прикладна програма “відчувають” саме два логічні процесори та спроможні розподіляти роботу між ними так само, як і у випадку повноцінної двопроцесорної системи. Поділ ресурсів (зокрема, виконавчих вузлів) поміж двома потоками подано на рис. 12.5b.

Потрібно відзначити, що технологією гіперпотокової обробки передбачено, аби при наявності лише одного активного потоку дозволити йому виконуватися з швидкодією, як і на звичайному процесорі, тобто щоб ефективність використання процесора не зменшувалася. Заради цього у процесорі передбачено два режими роботи: однозадачний (03) та багатозадачний (БЗ). У режимі 03 активним є лише один логічний процесор, який без обмежень користується наявними ресурсами. Інший логічний процесор призупинено командою HALT. Із появою другого програмного потоку логічний процесор, що не був задіяний, активується (за допомогою переривання поточного стану HALT). При цьому фізичний процесор перемикається до стану БЗ. Пригальмовування незадіяних логічних процесорів командою HALT покладено на операційну систему, яка, до речі, і відповідає за таке ж швидке виконання одного потоку, як і у випадку без використання технології Hyper-Threading.

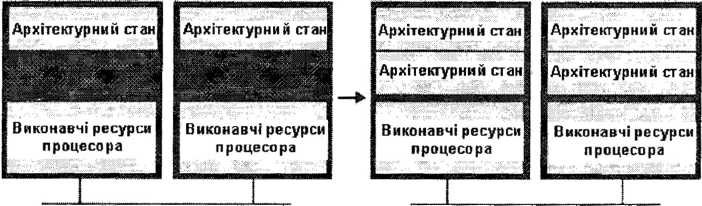

Для кожного з двох логічних процесорів зберігають так званий архітектурний стан (Architecture State), який складено із станів регістрів різного типу - загального призначення, керуючих, регістрів контролера переривань і службових (рис. 12.6). У кожного логічного процесора є свій контролер переривань і множина регістрів, для коректної роботи з якими введена таблиця альтернативних назв регістрів, яка відслідковує від повідність процесора.

Рис. 12.6. Традиційна двопроцесорна система (а) та альтернативна система з підтримкою технологіїгіперпотокової обробки (б)

При паралельному опрацюванні двох потоків підтримується вміст двох лічильників команд. Переважна частка команд отримується з таблиці Trace Cache (ТС), де ці команди зберігають в декодованому (трансльованому до рівня мікрооперацій) виді. Доступ до ТС обидва активні логічні процесори отримують за чергою, через такт. У той же час, коли активним є лише один логічний процесор, він отримує монопольний доступ до ТС, без чергування за тактами. Так само відбувається і доступ до пам’яті команд, коли треба опрацювати складну команду, що не має динамічно компільованого варіанту для подання на безпосереднє виконання. Буфери перетворення з передісторією ITLB (Instruction Translation Look-aside Buffer), задіяні за умови відсутності необхідних команд у кеш пам’яті команд, дублюються і постачають команди за правилом “кожен для свого потоку”. Блок декодування команд є поділюваним і у випадку, коли потрібне декодування команд для обох потоків, обслуговує їх за чергою (знову-таки через такт). Блоки черги мікрооперацій та їх розміщення поділено навпіл, аби розподілити елементи для кожного логічного процесора. Блоки диспетчерів у кількості 5 штук опрацьовують черги декодованих команд, незважаючи на приналежність до LP0 або LP1, і спрямовують команди на виконання цільовим виконавчим блокам залежно від готовності до виконання операндів команд і наявності вільного стану цільових виконавчих блоків (динамічне виконання). Кеш пам’яті усіх рівнів (L1/L підвищення продуктивності однопроцесорних систем шляхом нарощування ресурсів процесора, наприклад, шляхом нарощування ємності кеш пам’яті та добавлення нових операційних пристроїв. Хоча зрозуміло, що це тягне за собою зростання кількості транзисторів та площі кристалу, ускладнення процесора, і відповідно, вартості.

Іншим підходом є підвищення ефективності використання наявних ресурсів комп’ютерних систем з одним та декількома процесорами. Існує декілька дешевших, ніж масове розпаралелювання варіантів, які також дозволяють прискорити обчислення, а саме:

Багатопроцесорність на одному кристалі (Chip Multiprocessing). Два процесорні ядра фізично розташовані на одному кристалі із використанням спільної або розподіленої кеш пам’яті. Природно, що розмір кристала отримують досить великим, що є причиною великої вартості цього кристала. В багатопроцесорній системі можуть функціонувати декілька таких кристалів.для Хеоп, а також L3 для Xeon МР) є цілком поділюваними поміж двома логічними процесорами, проте для забезпечення когерентності (цілісності) даних записи до буферів перетворення з передісторією DTLB (Data Translation Look-aside Buffer) забезпечуються дескрипторами у вигляді ідентифікаторів логічних процесорів.

Таким чином, команди обох логічних процесорів можна виконувати одночасно на ресурсах одного фізичного процесора, причому ці ресурси поділено на чотири наступні класи: дубльовані, цілком поділювані, із дескрипторами елементів, динамічно поділювані залежно від режиму роботи: однозадачний режим першого або другого логічного процесора чи багатозадачний режим.

Більшість прикладних програм, що отримують прискорення у багатопроцесорних системах, можуть також прискорюватися і на процесорі із увімкнутим режимом гіпер потокової обробки без будь-яких змін власних машинних кодів. Але існують і проблеми. Наприклад, якщо один процес знаходиться в стані очікування, то він спроможний захопити усі ресурси фізичного процесора, перешкоджаючи тим самим функціонуванню другого логічного процесора. Таким чином, продуктивність при використанні технології гіперпотокової обробки може іноді й знижуватися (до 20%).

Ще однією метою реалізації технології гіперпотокової обробки було зведення до мінімуму зростання числа транзисторів, площі кристала та енергоспоживання при помітному зростанні продуктивності. І це завдання вдалося виконати. Додання до Хеоп/ Хеоп-МР підтримки технології гіперпотокової обробки збільшило площу кристала та енергоспоживання лише на 5%.

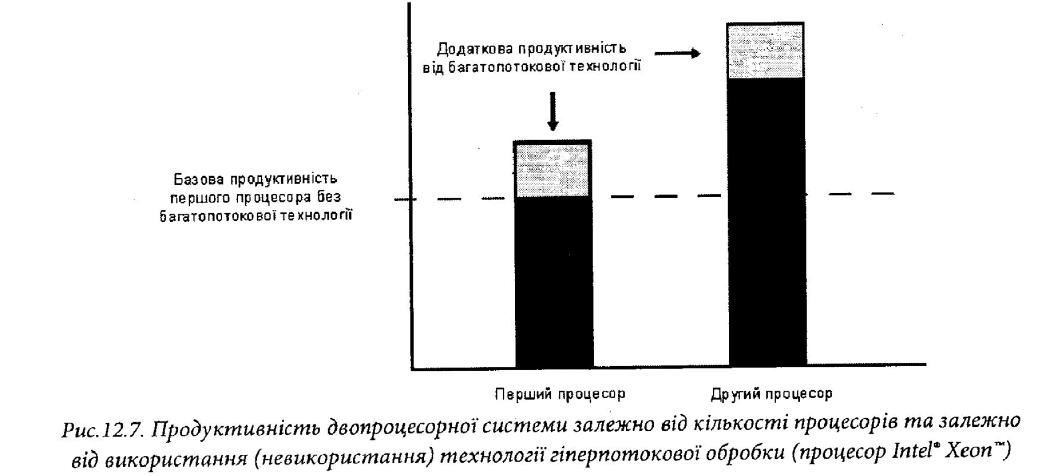

Загалом ефективність багатопотокової технології підтверджується зростанням продуктивності. Наступним рисунком (рис. 12.7) подано порівняльну продуктивність, що забезпечує двопроцесорна система без використання багатопотокової технології та із використанням цієї технології

Бачимо зростання продуктивності (темний колір) при використанні другого процесора в порівнянні із базовим її рівнем для одного задіяного процесора, та додатковий приріст продуктивності за рахунок увімкнення багатопотокової обробки (світлий колір).