- •Двнз «Чернівецький індустріальний коледж» архітектура комп’ютерів

- •Чернівці,

- •1.Історія розвитку обчислювальної техніки

- •2. Поняття про архітектуру еом. Принцип функціонування еом

- •38. Процесор векторного комп'ютера.

- •47. Функції арифметико-логічного пристрою. Способи обробки даних в арифметико-логічному пристрої

- •63. Частково-асоціативне відображення

- •82. Універсальна послідовна шина usb

- •1.Історія розвитку обчислювальної техніки

- •Покоління процесорів x86

- •Поняття архітектури і структурної організації комп’ютера

- •2. Поняття про архітектуру еом. Принцип функціонування еом Структура й принципи функціонування еом

- •3. Склад і призначення основних блоків

- •4. Архітектурні принципи Джона фон Неймана. Ненейманівські архітектури комп'ютерів

- •5. Апаратні і програмні засоби. Класифікація еом

- •Стандартні додатки Windows

- •Службові програми

- •Методи класифікації комп'ютерів.

- •Класифікація за призначенням

- •Великі еом (Main Frame)

- •МікроЕом

- •Персональні комп'ютери

- •Класифікація по рівню спеціалізації

- •Класифікація за розміром

- •Класифікація за сумісністю

- •6. Основні характеристики еом. Пк, особливості, класифікація, основні характеристики Основні характеристики пк

- •7. Персональні комп'ютери

- •8. Робочі станції. Багатотермінальні системи. Сервери

- •9. Кластерні комп'ютерні системи.

- •10. Суперкомп'ютери. Мікроконтролери. Спеціалізовані комп'ютери

- •11. Позиційні системи числення. Двійкові, вісімкові та шістнадцяткові числа

- •Двійкові, вісімкові та шістнадцяткові числа

- •12. Переведення чисел із системи числення з основою k у десяткову систему

- •13. Переведення чисел із десяткової системи у систему числення з основою k.

- •14. Прямий код. Обернений код. Доповняльний код. Способи представлення чисел

- •15. Числа з фіксованою комою. Числа із рухомою комою

- •16. Арифметичні операції. Ділення двійкових чисел

- •17. Арифметичні операції над двійковими числами у форматі з рухомою комою

- •18. Стандарт іеее-754. Розширений двійково-кодований десятковий код обміну ebcdic

- •19. Кодування алфавітно-цифрової інформації. Двійково-кодовані десяткові числа.

- •20. Американський стандартний код інформаційного обміну ascii. Стандарт кодування символів Unicode.

- •21. Кодування та виконання команд в комп'ютері

- •22. Виконання команд на рівні регістрів процессора.

- •23. Конвеєрне виконання команд

- •24. Класифікація архітектури комп'ютера за типом адресованої пам'яті.

- •25. Безпосередня адресація. Пряма адресація. Непряма адресація.

- •26. Відносна адресація. Базова адресація. Індексна адресація.

- •27. Сторінкова адресація. Неявна адресація. Стекова адресація. Використання стекової адресації.

- •28. Одношинна структура процесора.

- •29. Основні операції процесора. Вибірка слова з пам'яті. Запам'ятовування слова в пам'яті. Обмін даними між регістрами.

- •30. Багатошинна структура процесора.

- •31. Приклади виконання операцій в процесорі. Виконання операції додавання двох чисел.

- •32. Вимоги до процесора комп'ютера з простою системою команд. Базові принципи побудови процесора комп'ютера з простою системою команд.

- •33. Взаємодія процесора з пам'яттю в комп'ютері з простою системою команд.

- •34. Виконання команд в процесорі комп'ютера з простою системою команд. Фаза вибирання команди. Фаза декодування команди.

- •35. Конвеєрний процессор.

- •36. Мікродії ярусів конвеєрного процесора.

- •37. Суперскалярні процесори.

- •38. Процесор векторного комп'ютера.

- •39. Класифікація архітектури комп'ютера за рівнем суміщення опрацювання команд та даних.

- •40. Логічні операції.

- •1. Формальна логіка

- •2. Математична логіка

- •3. Програмування

- •41. Операція заперечення. Логічна 1. Логічне або. Виключне або.

- •42. Операції зсуву.

- •43. Операції відношення.

- •44. Арифметичні операції.

- •45. Операції обчислення елементарних функцій.

- •46. Операції перетворення даних.

- •47. Функції арифметико-логічного пристрою. Способи обробки даних в арифметико-логічному пристрої.

- •48. Елементарні операції арифметико-логічного пристрою.

- •49. Складні операції арифметико-логічного пристрою.

- •50. Структура арифметико-логічного пристрою.

- •51. Функції та методи побудови пристрою керування.

- •52. Пристрій керування з жорсткою логікою.

- •53. Пристрій керування на основі таблиць станів.

- •54. Пристрій мікропрограмного керування.

- •55. Порівняння пристроїв керування з жорсткою логікою та пристроїв мікропрограмного керування.

- •56 Ієрархічна організація пам'яті комп'ютера

- •57. Принцип ієрархічної організації пам'яті. Характеристики ефективності ієрархічної організації пам'яті

- •58. Кеш пам'ять в складі комп'ютера. Порядок взаємодії процесора і основної пам'яті через кеш пам'ять

- •59. Забезпечення ідентичності вмісту блоків кеш пам'яті і основної пам'яті

- •60. Функція відображення. Типи функцій відображення

- •61. Повністю асоціативне відображення

- •62. Пряме відображення

- •63. Частково-асоціативне відображення

- •64. Порядок заміщення блоків в кеш пам'яті з асоціативним відображенням

- •65. Підвищення ефективності кеш пам'яті

- •66. Статичний та динамічний розподіл пам'яті. Розподіл основної пам'яті за допомогою базових адрес

- •67. Віртуальна пам'ять. Сторінкова організація пам'яті

- •68. Основні правила сторінкової організації пам'яті. Реалізація сторінкової організації пам'яті

- •69. Апаратна реалізація сторінкової таблиці

- •70. Сегментна організація віртуальної пам'яті

- •71. Захист пам'яті від несанкціонованих звернень

- •72. Захист пам'яті за значеннями ключів

- •73. Кільцева схема захисту пам'яті

- •74. Архітектура системної плати

- •75. Синхронізація

- •76. Система шин

- •77. Особливості роботи шини

- •78. Характеристики шин пк

- •79. Шина pcmcia, vbl

- •80. Шина pci

- •82. Універсальна послідовна шина usb

- •83.Типи передач і формати інформації що передається

- •84. Шина scsi

- •85. Адресація пристроїв і передача даних

- •86. Система команд

- •87. Конфігурування пристроїв scsi

- •88. Ігровий адаптер Game-порт

- •89. Відеоадаптери

- •90. Послідовний інтерфейс. Сом-порт

- •91. Програмна модель сом-порта

- •92. Програмування послідовного зв’язку

- •93. Ініціалізація послідовного порта. Передача і прийом даних

- •95. Паралельний інтерфейс lpt-порт. Стандартний режим spp

- •96. Режим epp

- •97. Режим ecp

- •98. Узгодження режимів

- •99. Приклад програмування

- •100. Клавіатура

- •101. Під'єднання зовнішніх пристроїв до комп'ютера

- •102. Розпізнавання пристроїв введення-виведення

- •103. Методи керування введенням-виведенням

- •104. Програмно-кероване введення-виведення.

- •105. Система переривання програм та організація введення-виведення за перериваннями

- •106. Прямий доступ до пам'яті. Введення-виведення під керуванням периферійних процесорів

- •107. Мультиплексний та селекторний канали введення-виведення

- •108. Використання принципів паралельної обробки інформації в архітектурі комп'ютера

- •109. Вибір кількості процесорів в багатопроцесорній системі

- •110. Багатопотокова обробка інформації. Окр

- •111. Класифікація Шора. Класифікація Фліна

- •112. Типи архітектур систем окмд. Типи архітектур систем мкмд

- •113.Організація комп'ютерних систем із спільною пам'яттю

- •114. Організація комп'ютерних систем із розподіленою пам'яттю

- •115. Комунікаційні мережі багатопроцесорних систем

86. Система команд

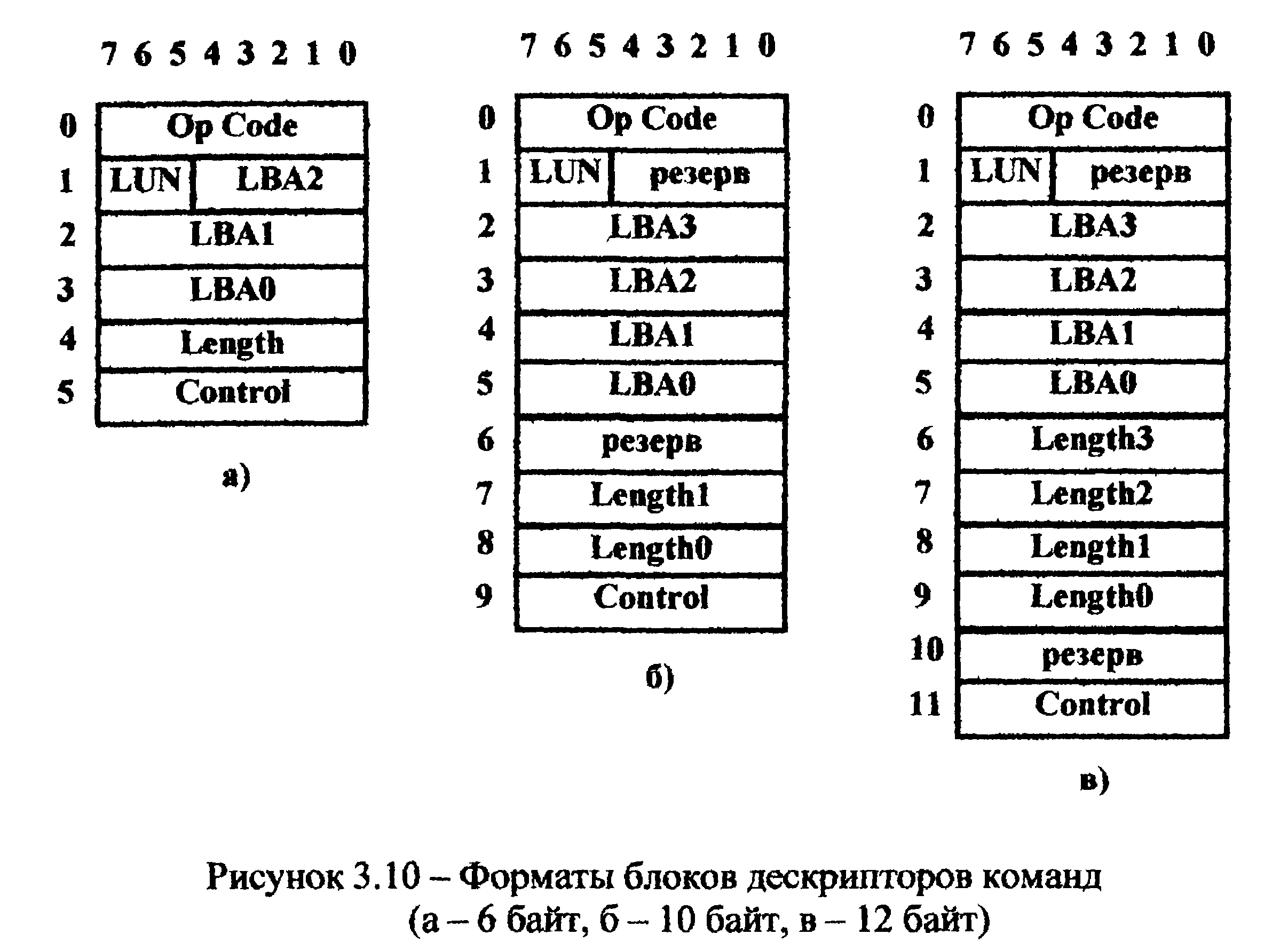

Система команд SCSI включає загальні команди, що застосовуються для пристроїв всіх класів і специфічні для кожного класу. Як загальні, так і специфічні набори команд містять обов'язкові, додаткові та

фірмові команди. Будь SCSI-пристрій повинен підтримувати обов'язкові команди загального набору і свого класу, чим забезпечується високий рівень сумісності. Команда передається ІУ в ЦУ через блок дескриптора команди, який надсилається у фазі Command Деякі команди супроводжуються блоком параметрів, наступним за блоком дескриптора в фазі Data. Формати блоків стандартизовані, довжина блоку (6, 10 або 12 байт) визначається кодом операції (перший байт блоку). Структура блоків дескрипторів команд наведена на рис. 3.10.

Блок містить наступні поля:

- OpCode - код операції. Біти 7-5 визначають групу, а біти 4-0 код команди. У групі 0 блок дескриптора має довжину 6 байт, в групах 1 та 2 - 10 байт, у групі 5-12 байт. Групи 3 і 4 зарезервовані, групи 6 і 7 віддані на розсуд розробників.

- LUN - номер ЛУ (біти 7-5 байта 1). Якщо для ідентифікації використовуються повідомлення Identify, то це поле ігнорується (встановлюється LUN = 0).

- LBA - адреса логічного блоку, 21 біт для 6-байтних блоків і 32 біта для 10-і 12-байтних блоків. У ряді команд поле не використовується.

Length - довжина (кількість блоків або байтів) переданих даних або блоку параметрів. У ряді команд поле не використовується.

Control - байт управління. Біти 7-6 використовуються на розсуд розробника, біти 5-2 зарезервовані, біт 1 - Flag (при Flag = l повідомлення

Linked Command Complete (With Flag) викликатиме переривання між командами ланцюжка), біт 0 - Link (одиничне значення служить ознакою ланцюжка команд).

У полях LBA і Length першими передаються старші байти, потім молодші. Зарезервовані поля для сумісності з майбутніми стандартами повинні мати нульові значення

Виконання команди завершується у фазі Status передачею байта стану Status Byte. У байті стану використовують тільки біти 5-1, можливі стану наведено в табл. 3.12 (біти 7,6, 0 зарезервовані).

Набір команд для пристроїв класів 0-9 наведено у Додатку Д. Будь ЦУ SCSI-2 зобов'язана підтримувати чотири команди: Inquiry, Request Sense, Send Diagnostic, Test Jnit Ready. Вони використовуються для конфігурування системи, тестування пристроїв, а також повідомлень про помилки і виняткових ситуаціях. Команда Inquiry дозволяє отримати інформацію про ЛУ через стандартизований блок даних довжину 96 байт (тип підключеного ПУ, можливість зміни носія, підтримка 32 - або 16-бітного розширення, синхронного обміну, відносної адресації, ланцюжків команд, черг і повідомлення про асинхронних події).

Виконання команд. При виконанні одиночної команди (наприклад команда читання Read), ВП має активний набір покажчиків і кілька збережених наборів, по одному на кожен з процесів. ІУ відновлює покажчики процесу в активний набір і, вигравши арбітраж, вибирає ЦУ. Як тільки ЦУ вибрано, воно бере на себе управління процесом. У фазі Selection ІУ вводить сигнал ATN #, повідомляючи про намір послати повідомлення Identify із зазначенням адресується ЛУ. Таким чином встановлюється зв'язок ІУ з даним процесом і його набором покажчиків. ЦУ переходить у фазу Command і приймає блок дескриптора команди.

Інтерпретувавши команду, ЦУ переходить у фазу Data IN, передає дані, потім переводиться в фазу Status і посилає стан Good Потім у фазі Message IN пристрій посилає повідомлення Command Complete, після чого звільняє шину (фаза Bus Free).

Якщо пристрій, отримавши команду, визначить, що для одержання витребуваних даних необхідно багато часу, воно звільнить шину, надіславши повідомлення Disconnect. Як тільки необхідні дані готові в ЦУ, воно, вигравши арбітраж, вибере ІУ (у фазі Reselect) і у фазі Message IN пошле йому повідомлення Identify. ІУ відновить відповідний набір покажчиків в активний і продовжить виконання процесу, як описано вище. Якщо ЦУ хоче від'єднатися, коли частина даних вже передана (наприклад, головка дійшла до кінця циліндра і потрібен час на позиціонування), воно посилає повідомлення Save Data Pointer а потім Disconnect. Після повторного з'єднання передача даних відновиться з точки, визначеної останнім збереженим значенням покажчика. Якщо сталася помилка чи винятки ЦУ може повторити обмін даними, надіславши повідомлення Restore Pointers або від'єднати без повідомлення Save Data Pointers

У разі використання ланцюжка команд, після успішного завершення кожної команди, ЦУ автоматично переходить до виконання наступного. Усі команди ланцюжка адресуються до однієї і тієї ж зв'язку і є частиною одного процесу. Команди не є повністю незалежними - при використанні біта відносної адресації останній блок, адресований попередньою командою, доступний для наступної (наприклад команда Search Data знаходить на диску потрібний блок, а пов'язана з нею команда читання Read читає цей блок або блоки із зазначеним зсувом щодо знайденого. За виконання пов'язаних команд ЦУ посилає повідомлення Linked Command Complete (можливо, з прапором), а ІУ оновлює набір збережених покажчиків (вказують на чергову команду ланцюжка).

Команди можуть виконуватися з використанням черг. ЦУ можуть підтримувати немарковані та марковані черги. Підтримка немаркованих черг, визначена ще в SCSI-1, дозволяє будь-якому ЛУ (LUN) або цільовій програмі (TRN), зайнятим процесом від одного ІУ, приймати команди (починати процес) з іншими ІУ. Маркіровані черги визначені в SCSI-2 для ЛУ (LUN, але не TRN). Для кожної з цим існує своя чергу розміром до 256 процесів.

Постановка в чергу виконується через механізм повідомлень. Процес, поставлений в чергу з повідомленням Head Of Queue Tag, буде виконуватися

відразу після завершення поточного активного процесу (поза чергою). Процеси, поставлені в чергу з повідомленням Simple Queue Tag, виконуються ЦУ в порядку, який вона вважає оптимальним, а процес, поставлений в чергу з повідомленням Ordered Queue Tag, виповнюється останнім. ІУ може видалити процес з черги. Зміна порядку команд у черзі не стосується порядку в ланцюжку команд, оскільки ланцюжок належить одному процесу.