- •Двнз «Чернівецький індустріальний коледж» архітектура комп’ютерів

- •Чернівці,

- •1.Історія розвитку обчислювальної техніки

- •2. Поняття про архітектуру еом. Принцип функціонування еом

- •38. Процесор векторного комп'ютера.

- •47. Функції арифметико-логічного пристрою. Способи обробки даних в арифметико-логічному пристрої

- •63. Частково-асоціативне відображення

- •82. Універсальна послідовна шина usb

- •1.Історія розвитку обчислювальної техніки

- •Покоління процесорів x86

- •Поняття архітектури і структурної організації комп’ютера

- •2. Поняття про архітектуру еом. Принцип функціонування еом Структура й принципи функціонування еом

- •3. Склад і призначення основних блоків

- •4. Архітектурні принципи Джона фон Неймана. Ненейманівські архітектури комп'ютерів

- •5. Апаратні і програмні засоби. Класифікація еом

- •Стандартні додатки Windows

- •Службові програми

- •Методи класифікації комп'ютерів.

- •Класифікація за призначенням

- •Великі еом (Main Frame)

- •МікроЕом

- •Персональні комп'ютери

- •Класифікація по рівню спеціалізації

- •Класифікація за розміром

- •Класифікація за сумісністю

- •6. Основні характеристики еом. Пк, особливості, класифікація, основні характеристики Основні характеристики пк

- •7. Персональні комп'ютери

- •8. Робочі станції. Багатотермінальні системи. Сервери

- •9. Кластерні комп'ютерні системи.

- •10. Суперкомп'ютери. Мікроконтролери. Спеціалізовані комп'ютери

- •11. Позиційні системи числення. Двійкові, вісімкові та шістнадцяткові числа

- •Двійкові, вісімкові та шістнадцяткові числа

- •12. Переведення чисел із системи числення з основою k у десяткову систему

- •13. Переведення чисел із десяткової системи у систему числення з основою k.

- •14. Прямий код. Обернений код. Доповняльний код. Способи представлення чисел

- •15. Числа з фіксованою комою. Числа із рухомою комою

- •16. Арифметичні операції. Ділення двійкових чисел

- •17. Арифметичні операції над двійковими числами у форматі з рухомою комою

- •18. Стандарт іеее-754. Розширений двійково-кодований десятковий код обміну ebcdic

- •19. Кодування алфавітно-цифрової інформації. Двійково-кодовані десяткові числа.

- •20. Американський стандартний код інформаційного обміну ascii. Стандарт кодування символів Unicode.

- •21. Кодування та виконання команд в комп'ютері

- •22. Виконання команд на рівні регістрів процессора.

- •23. Конвеєрне виконання команд

- •24. Класифікація архітектури комп'ютера за типом адресованої пам'яті.

- •25. Безпосередня адресація. Пряма адресація. Непряма адресація.

- •26. Відносна адресація. Базова адресація. Індексна адресація.

- •27. Сторінкова адресація. Неявна адресація. Стекова адресація. Використання стекової адресації.

- •28. Одношинна структура процесора.

- •29. Основні операції процесора. Вибірка слова з пам'яті. Запам'ятовування слова в пам'яті. Обмін даними між регістрами.

- •30. Багатошинна структура процесора.

- •31. Приклади виконання операцій в процесорі. Виконання операції додавання двох чисел.

- •32. Вимоги до процесора комп'ютера з простою системою команд. Базові принципи побудови процесора комп'ютера з простою системою команд.

- •33. Взаємодія процесора з пам'яттю в комп'ютері з простою системою команд.

- •34. Виконання команд в процесорі комп'ютера з простою системою команд. Фаза вибирання команди. Фаза декодування команди.

- •35. Конвеєрний процессор.

- •36. Мікродії ярусів конвеєрного процесора.

- •37. Суперскалярні процесори.

- •38. Процесор векторного комп'ютера.

- •39. Класифікація архітектури комп'ютера за рівнем суміщення опрацювання команд та даних.

- •40. Логічні операції.

- •1. Формальна логіка

- •2. Математична логіка

- •3. Програмування

- •41. Операція заперечення. Логічна 1. Логічне або. Виключне або.

- •42. Операції зсуву.

- •43. Операції відношення.

- •44. Арифметичні операції.

- •45. Операції обчислення елементарних функцій.

- •46. Операції перетворення даних.

- •47. Функції арифметико-логічного пристрою. Способи обробки даних в арифметико-логічному пристрої.

- •48. Елементарні операції арифметико-логічного пристрою.

- •49. Складні операції арифметико-логічного пристрою.

- •50. Структура арифметико-логічного пристрою.

- •51. Функції та методи побудови пристрою керування.

- •52. Пристрій керування з жорсткою логікою.

- •53. Пристрій керування на основі таблиць станів.

- •54. Пристрій мікропрограмного керування.

- •55. Порівняння пристроїв керування з жорсткою логікою та пристроїв мікропрограмного керування.

- •56 Ієрархічна організація пам'яті комп'ютера

- •57. Принцип ієрархічної організації пам'яті. Характеристики ефективності ієрархічної організації пам'яті

- •58. Кеш пам'ять в складі комп'ютера. Порядок взаємодії процесора і основної пам'яті через кеш пам'ять

- •59. Забезпечення ідентичності вмісту блоків кеш пам'яті і основної пам'яті

- •60. Функція відображення. Типи функцій відображення

- •61. Повністю асоціативне відображення

- •62. Пряме відображення

- •63. Частково-асоціативне відображення

- •64. Порядок заміщення блоків в кеш пам'яті з асоціативним відображенням

- •65. Підвищення ефективності кеш пам'яті

- •66. Статичний та динамічний розподіл пам'яті. Розподіл основної пам'яті за допомогою базових адрес

- •67. Віртуальна пам'ять. Сторінкова організація пам'яті

- •68. Основні правила сторінкової організації пам'яті. Реалізація сторінкової організації пам'яті

- •69. Апаратна реалізація сторінкової таблиці

- •70. Сегментна організація віртуальної пам'яті

- •71. Захист пам'яті від несанкціонованих звернень

- •72. Захист пам'яті за значеннями ключів

- •73. Кільцева схема захисту пам'яті

- •74. Архітектура системної плати

- •75. Синхронізація

- •76. Система шин

- •77. Особливості роботи шини

- •78. Характеристики шин пк

- •79. Шина pcmcia, vbl

- •80. Шина pci

- •82. Універсальна послідовна шина usb

- •83.Типи передач і формати інформації що передається

- •84. Шина scsi

- •85. Адресація пристроїв і передача даних

- •86. Система команд

- •87. Конфігурування пристроїв scsi

- •88. Ігровий адаптер Game-порт

- •89. Відеоадаптери

- •90. Послідовний інтерфейс. Сом-порт

- •91. Програмна модель сом-порта

- •92. Програмування послідовного зв’язку

- •93. Ініціалізація послідовного порта. Передача і прийом даних

- •95. Паралельний інтерфейс lpt-порт. Стандартний режим spp

- •96. Режим epp

- •97. Режим ecp

- •98. Узгодження режимів

- •99. Приклад програмування

- •100. Клавіатура

- •101. Під'єднання зовнішніх пристроїв до комп'ютера

- •102. Розпізнавання пристроїв введення-виведення

- •103. Методи керування введенням-виведенням

- •104. Програмно-кероване введення-виведення.

- •105. Система переривання програм та організація введення-виведення за перериваннями

- •106. Прямий доступ до пам'яті. Введення-виведення під керуванням периферійних процесорів

- •107. Мультиплексний та селекторний канали введення-виведення

- •108. Використання принципів паралельної обробки інформації в архітектурі комп'ютера

- •109. Вибір кількості процесорів в багатопроцесорній системі

- •110. Багатопотокова обробка інформації. Окр

- •111. Класифікація Шора. Класифікація Фліна

- •112. Типи архітектур систем окмд. Типи архітектур систем мкмд

- •113.Організація комп'ютерних систем із спільною пам'яттю

- •114. Організація комп'ютерних систем із розподіленою пам'яттю

- •115. Комунікаційні мережі багатопроцесорних систем

55. Порівняння пристроїв керування з жорсткою логікою та пристроїв мікропрограмного керування.

Вище були розглянуті два основних методи побудови логіки формування сигналів керування. Перший з них, який одержав назву “жорсткої” або “запаяної” логіки, виражається в тому, що для кожної команди процесора існує набір логічних схем, які в потрібних тактах збуджують відповідні сигнали керування. Другий метод, який називають принципом мікропрограмного керування, передбачає формування сигналів керування за вмістом регістра мікрокоманд, в який мікрокоманди записуються із пам’яті мікро- команд. Шляхом послідовного зчитування мікрокоманд із пам’яті в цей регістр організується потрібна послідовність сигналів керування. Завдяки тому, що мікрокоманди записуються до пам’яті, вміст якої при потребі можна частково, або повністю замінити, пристрої мікропрограмного керування мають наступні основні переваги в порівнянні з пристроями керування з жорсткою логікою:

В них можна використовувати мікропрограми, які вже були відлагоджені та апробовані на інших комп’ютерах.

Шляхом заміни мікропрограми в пам’яті мікрокоманд комп’ютер можна модифікувати з метою покращання технічних характеристик чи розширення функцій, і, тим самим, продовжити термін його використання.

Можуть бути використані наробки мікропрограм в наступних поколіннях комп’ютерів однієї сім’ї.

Мікропрограмування є простішим, ніж керування з жорсткою логікою, що спрощує розробку пристрою керування.

Простішим є обслуговування мікропрограмованих комп’ютерів та їх відлагоджен- ня завдяки простішій заміні мікрокоманд та мікропрограм.

В швидкодії мікропрограмне керування програє керуванню з “жорсткою” логікою. Тому, завдяки створенню мов опису апаратних засобів комп’ютера та потужних програмних засобів високорівневого проектування, пристрої керування з жорсткою логікою знайшли ширше застосування в сучасних комп’ютерах.

56 Ієрархічна організація пам'яті комп'ютера

Різниця між продуктивністю процесора та пам’яті

Одним із вузьких місць комп’ютерів з архітектурою Джона фон Неймана є розрив в продуктивності процесора та пам’яті, причому цей розрив неухильно збільшується. Так, продуктивність процесора зростає вдвічі приблизно кожні 1,5 роки. В табл. 10.1 наведено ріст з роками тактової частоти роботи процесора на прикладі процесорів фірми Ігйеі.

Таблиця

10.1

Роки

1980

1985

1990

1995

2000

2005

2005-1980

Тип

процесора

8080

286

386

Pentium

Р

III

P-IV

Тактова

частота (МГц)

1

6

20

150

750

3800

3800

разів

Час

одного такту (не)

1000

166

50

6

1.6

0.26

3800

разів

Разом з тим, для пам’яті приріст швидкодії не є таким високим, як у процесорів. В табл. 10.2 наведено зміну з роками ціни зберігання одного МБ інформації, часу доступу до статичної (ЗЯАМ) і динамічної (БЯАМ) напівпровідникової пам’яті та дискової пам’яті, а також ємність основної та зовнішньої дискової пам’яті.

Таблиця 10.2

'Чч\Роки X ар акт еристики'' |

1980 |

1985 |

1990 |

1995 |

2000 |

2005 |

Ріп протжгем 2005- 1980 |

Ціна (5,МБ) |

19200 |

2900 |

320 |

256 |

100 |

50 |

380 разів |

Час доступу <кс) |

300 |

130 |

35 |

15 ' |

2 |

0.5 |

300 разів |

|

|

|

|

|

|

|

|

Ціна (5 МБ) |

8000 |

880 |

100 |

30 |

1 |

0 1 |

80 000 разів |

Час доступу (не) |

375 |

200 |

100 |

70 |

50 |

30 |

12 разів |

Типобии об’єм ОП на базі БЇІАМ(МБ) |

0.064 |

0.256 |

4 |

16 |

64 |

25S |

4 000 разів |

|

|

|

|

|

|

|

|

Ціна (5 МБ) |

500 |

100 |

8 |

0.3 |

0.05 |

0.01 |

5 000 разів |

Час доступу (не) |

300 |

150 |

35 |

15 |

2 |

0.5 |

300 разів |

Типовий об’єм дискової пам’яті (МБ) |

1 |

10 |

160 |

1000 |

9 000 |

S0000 |

80000 разів |

ram

DRAM

DISC

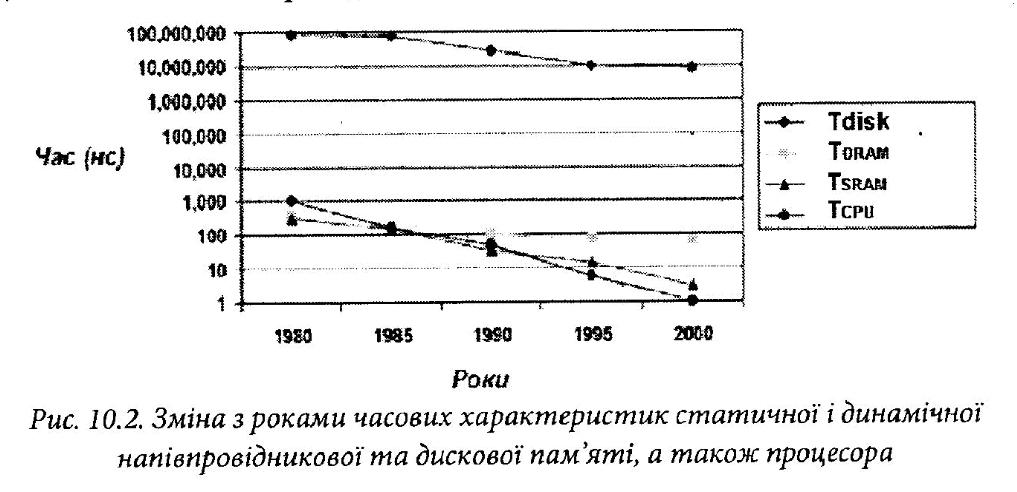

Виходячи з наведених даних в табл. 10.1 та табл. 10.2, нарис. 10.2 показана зміна з роками часу доступу до статичної Т та динамічної Т0КАМ напівпровідникової та дискової ТСІЖ пам’яті, а також тактової частоти роботи процесора Тсиг Як видно з наведеного рисунку, існує значна різниця між тактовою частотою процесора і часом доступу до динамічної пам’яті. Причому з роками розрив у значеннях часових характеристик між процесором і динамічною напівпровідниковою пам’яттю та дисковою пам’яттю зростає.

Особливо важливим з точки зору архітектури комп’ютера є те, що зростає розрив між тактовою частотою процесора і часом доступу до динамічної напівпровідникової пам’яті БРАМ, на основі якої будується основна пам’ять комп’ютера. Адже якраз між цими двома вузлами комп’ютера здійснюється основна частка обмінів інформацією. В той час, коли продуктивність процесора зростає щороку на 60 % (подвоєння за 1,5 року), ріст продуктивності динамічної напівпровідникової пам’яті не перевищує 9 % в рік (подвоєння за 10 років). Це виражається в збільшенні розриву в продуктивності між процесором і динамічною напівпровідниковою пам'яттю на 50 % в рік (рис. 10.3).

Разом з тим, з рис. 10.2 видно, що розрив з роками між продуктивністю процесора і статичної напівпровідникової пам’яті є незначним. Виглядає доцільним побудова основної пам’яті комп’ютера на базі статичної напівпровідникової пам’яті. Однак це не так, оскільки, як видно з табл. 10.2, зберігання 1МБ інформації в такій пам’яті є приблизно в 100 разів дорожчим, аніж в динамічній напівпровідниковій пам’яті. Тому був знайдений наступний вихід з цієї ситуації - включення між основною пам’яттю комп’ютера і процесором додаткової швидкої пам’яті малої ємності, побудованої на основі статичної напівпровідникової пам’яті.

Іще більший розрив існує між продуктивністю зовнішньої дискової і динамічної напівпровідникової пам’яті. Однак, як видно з табл. 10.2, вартість зберігання 1МБ інформації в дисковій пам’яті приблизно в 20 разів менша, ніж в динамічній напівпровідниковій пам’яті. Крім того, вона забезпечує зберігання значно більших об’ємів інформації. Тому і тут виникає потреба пошуку механізму, який би забезпечив прискорення обміну між основною і зовнішньою пам’яттю.