- •Двнз «Чернівецький індустріальний коледж» архітектура комп’ютерів

- •Чернівці,

- •1.Історія розвитку обчислювальної техніки

- •2. Поняття про архітектуру еом. Принцип функціонування еом

- •38. Процесор векторного комп'ютера.

- •47. Функції арифметико-логічного пристрою. Способи обробки даних в арифметико-логічному пристрої

- •63. Частково-асоціативне відображення

- •82. Універсальна послідовна шина usb

- •1.Історія розвитку обчислювальної техніки

- •Покоління процесорів x86

- •Поняття архітектури і структурної організації комп’ютера

- •2. Поняття про архітектуру еом. Принцип функціонування еом Структура й принципи функціонування еом

- •3. Склад і призначення основних блоків

- •4. Архітектурні принципи Джона фон Неймана. Ненейманівські архітектури комп'ютерів

- •5. Апаратні і програмні засоби. Класифікація еом

- •Стандартні додатки Windows

- •Службові програми

- •Методи класифікації комп'ютерів.

- •Класифікація за призначенням

- •Великі еом (Main Frame)

- •МікроЕом

- •Персональні комп'ютери

- •Класифікація по рівню спеціалізації

- •Класифікація за розміром

- •Класифікація за сумісністю

- •6. Основні характеристики еом. Пк, особливості, класифікація, основні характеристики Основні характеристики пк

- •7. Персональні комп'ютери

- •8. Робочі станції. Багатотермінальні системи. Сервери

- •9. Кластерні комп'ютерні системи.

- •10. Суперкомп'ютери. Мікроконтролери. Спеціалізовані комп'ютери

- •11. Позиційні системи числення. Двійкові, вісімкові та шістнадцяткові числа

- •Двійкові, вісімкові та шістнадцяткові числа

- •12. Переведення чисел із системи числення з основою k у десяткову систему

- •13. Переведення чисел із десяткової системи у систему числення з основою k.

- •14. Прямий код. Обернений код. Доповняльний код. Способи представлення чисел

- •15. Числа з фіксованою комою. Числа із рухомою комою

- •16. Арифметичні операції. Ділення двійкових чисел

- •17. Арифметичні операції над двійковими числами у форматі з рухомою комою

- •18. Стандарт іеее-754. Розширений двійково-кодований десятковий код обміну ebcdic

- •19. Кодування алфавітно-цифрової інформації. Двійково-кодовані десяткові числа.

- •20. Американський стандартний код інформаційного обміну ascii. Стандарт кодування символів Unicode.

- •21. Кодування та виконання команд в комп'ютері

- •22. Виконання команд на рівні регістрів процессора.

- •23. Конвеєрне виконання команд

- •24. Класифікація архітектури комп'ютера за типом адресованої пам'яті.

- •25. Безпосередня адресація. Пряма адресація. Непряма адресація.

- •26. Відносна адресація. Базова адресація. Індексна адресація.

- •27. Сторінкова адресація. Неявна адресація. Стекова адресація. Використання стекової адресації.

- •28. Одношинна структура процесора.

- •29. Основні операції процесора. Вибірка слова з пам'яті. Запам'ятовування слова в пам'яті. Обмін даними між регістрами.

- •30. Багатошинна структура процесора.

- •31. Приклади виконання операцій в процесорі. Виконання операції додавання двох чисел.

- •32. Вимоги до процесора комп'ютера з простою системою команд. Базові принципи побудови процесора комп'ютера з простою системою команд.

- •33. Взаємодія процесора з пам'яттю в комп'ютері з простою системою команд.

- •34. Виконання команд в процесорі комп'ютера з простою системою команд. Фаза вибирання команди. Фаза декодування команди.

- •35. Конвеєрний процессор.

- •36. Мікродії ярусів конвеєрного процесора.

- •37. Суперскалярні процесори.

- •38. Процесор векторного комп'ютера.

- •39. Класифікація архітектури комп'ютера за рівнем суміщення опрацювання команд та даних.

- •40. Логічні операції.

- •1. Формальна логіка

- •2. Математична логіка

- •3. Програмування

- •41. Операція заперечення. Логічна 1. Логічне або. Виключне або.

- •42. Операції зсуву.

- •43. Операції відношення.

- •44. Арифметичні операції.

- •45. Операції обчислення елементарних функцій.

- •46. Операції перетворення даних.

- •47. Функції арифметико-логічного пристрою. Способи обробки даних в арифметико-логічному пристрої.

- •48. Елементарні операції арифметико-логічного пристрою.

- •49. Складні операції арифметико-логічного пристрою.

- •50. Структура арифметико-логічного пристрою.

- •51. Функції та методи побудови пристрою керування.

- •52. Пристрій керування з жорсткою логікою.

- •53. Пристрій керування на основі таблиць станів.

- •54. Пристрій мікропрограмного керування.

- •55. Порівняння пристроїв керування з жорсткою логікою та пристроїв мікропрограмного керування.

- •56 Ієрархічна організація пам'яті комп'ютера

- •57. Принцип ієрархічної організації пам'яті. Характеристики ефективності ієрархічної організації пам'яті

- •58. Кеш пам'ять в складі комп'ютера. Порядок взаємодії процесора і основної пам'яті через кеш пам'ять

- •59. Забезпечення ідентичності вмісту блоків кеш пам'яті і основної пам'яті

- •60. Функція відображення. Типи функцій відображення

- •61. Повністю асоціативне відображення

- •62. Пряме відображення

- •63. Частково-асоціативне відображення

- •64. Порядок заміщення блоків в кеш пам'яті з асоціативним відображенням

- •65. Підвищення ефективності кеш пам'яті

- •66. Статичний та динамічний розподіл пам'яті. Розподіл основної пам'яті за допомогою базових адрес

- •67. Віртуальна пам'ять. Сторінкова організація пам'яті

- •68. Основні правила сторінкової організації пам'яті. Реалізація сторінкової організації пам'яті

- •69. Апаратна реалізація сторінкової таблиці

- •70. Сегментна організація віртуальної пам'яті

- •71. Захист пам'яті від несанкціонованих звернень

- •72. Захист пам'яті за значеннями ключів

- •73. Кільцева схема захисту пам'яті

- •74. Архітектура системної плати

- •75. Синхронізація

- •76. Система шин

- •77. Особливості роботи шини

- •78. Характеристики шин пк

- •79. Шина pcmcia, vbl

- •80. Шина pci

- •82. Універсальна послідовна шина usb

- •83.Типи передач і формати інформації що передається

- •84. Шина scsi

- •85. Адресація пристроїв і передача даних

- •86. Система команд

- •87. Конфігурування пристроїв scsi

- •88. Ігровий адаптер Game-порт

- •89. Відеоадаптери

- •90. Послідовний інтерфейс. Сом-порт

- •91. Програмна модель сом-порта

- •92. Програмування послідовного зв’язку

- •93. Ініціалізація послідовного порта. Передача і прийом даних

- •95. Паралельний інтерфейс lpt-порт. Стандартний режим spp

- •96. Режим epp

- •97. Режим ecp

- •98. Узгодження режимів

- •99. Приклад програмування

- •100. Клавіатура

- •101. Під'єднання зовнішніх пристроїв до комп'ютера

- •102. Розпізнавання пристроїв введення-виведення

- •103. Методи керування введенням-виведенням

- •104. Програмно-кероване введення-виведення.

- •105. Система переривання програм та організація введення-виведення за перериваннями

- •106. Прямий доступ до пам'яті. Введення-виведення під керуванням периферійних процесорів

- •107. Мультиплексний та селекторний канали введення-виведення

- •108. Використання принципів паралельної обробки інформації в архітектурі комп'ютера

- •109. Вибір кількості процесорів в багатопроцесорній системі

- •110. Багатопотокова обробка інформації. Окр

- •111. Класифікація Шора. Класифікація Фліна

- •112. Типи архітектур систем окмд. Типи архітектур систем мкмд

- •113.Організація комп'ютерних систем із спільною пам'яттю

- •114. Організація комп'ютерних систем із розподіленою пам'яттю

- •115. Комунікаційні мережі багатопроцесорних систем

53. Пристрій керування на основі таблиць станів.

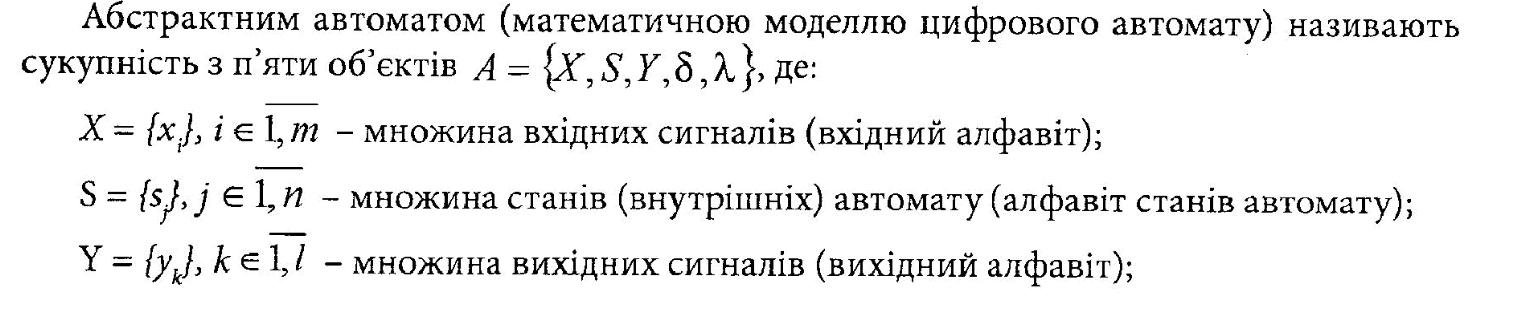

Абстрактні автомати

Метод таблиць станів передбачає розгляд пристрою керування як цифрового автомату, тобто логічного пристрою, який забезпечує формування сигналів керування за відповідним алгоритмом з врахуванням своїх внутрішніх станів.

Цифровий автомат можна подати у вигляді його математичної (абстрактної) і структурної моделей, які відповідно називаються абстрактним та структурним автоматами. Абстрактну модель використовують на першому етапі проектування, коли описують функціонування автомату, тобто правила переробки вхідної інформації у вихідну. На цьому етапі автомат подається у вигляді “чорної скриньки”. Розгляд абстрактної моделі цифрового автомату дозволяє проводити його попередню оптимізацію ще до етапу структурного синтезу. Структурну модель застосовують для побудови схеми цифрового автомату.

В подальшому будемо використовувати так званий скінчений абстрактний автомат, в якого множина внутрішніх станів і множина вхідних сигналів (а, отже, й множина вихідних сигналів) є скінченими множинами, повністю визначений (детермінований) абстрактний автомат, в якого функція переходів 5 і функція виходів X визначені для всіх пар (xnSj ), та ініціальний абстрактний автомат, в якого один із станів s0 є S виділено як початковий стан, з якого автомат завжди починає роботу.

Отже, на абстрактному рівні функціонування цифровий автомат розглядається як перетворювач вхідних слів у вихідні слова, які складаються з букв вхідного і вихідного алфавіту. Внутрішні стани автомату - це інформація про минуле (передісторію) розви-, тку процесу керування в часі. Вона дозволяє використати час як явну вхідну змінну. Потрібно відзначити, що абстрактний автомат функціонує в дискретному часі, а переходи з одного стану в інший проводяться миттєво.

Залежно від способу генерування значень вихідних сигналів розрізняють три типи автоматів: Мілі, Мура, С-автомат.

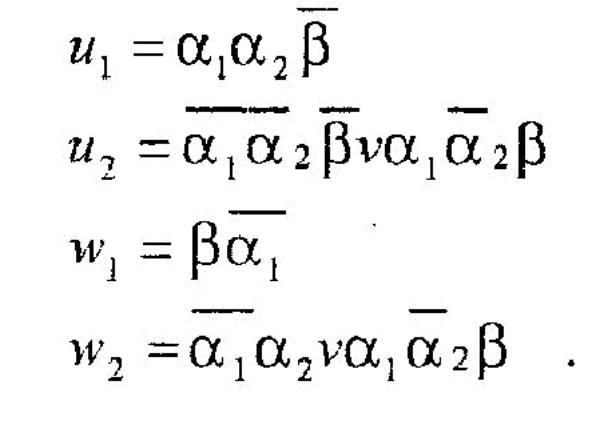

Автомат Мілі описується наступною системою рівнянь:

Автомат Мілі можна представити у вигляді структурної схеми (рис. 8.4), вузли якої представляють відповідно функцію виходів X > функцію переходів 8 і пам’ять станів S, та з’єднані між собою відповідними зв’язками. Значення на його виході в момент часу t визначається значенням в даний момент на його вході та його станом, а також функцією виходів. Стан автомату Мілі в момент часу t+1 визначається значенням в даний момент на його вході та його станом, а також функцією переходів.

y(t) = L(s(t))

s(/ + l) = 8 (x(t) s(0).

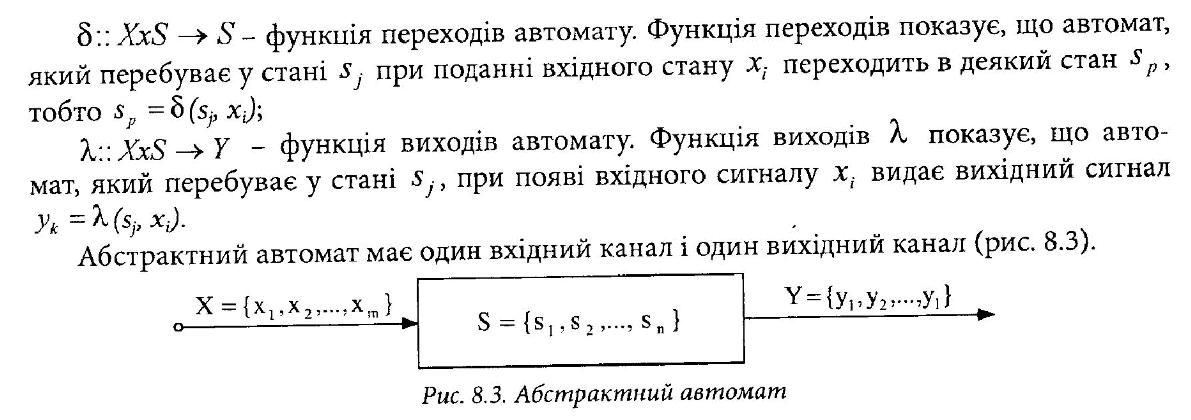

Автомат Мура також можна представити у вигляді структурної схеми (рис. 8.5), вузли якої представляють відповідно функцію виходів А,, функцію переходів 8 і пам’ять станів S, та з’єднані між собою відповідними зв’язками.

Рис. 8.5. Автомат Мура

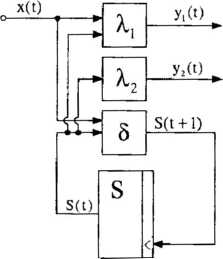

С-автомат можна представити у вигляді структурної схеми (рис. 8.6), вузли якої представляють відповідно функції виходів X 1 та X 2, функцію переходів 8 і пам’ять станів S, та з’єднані між собою відповідними зв’язками. Цей автомат має два виходи. Значення на першому його виході в момент часу t визначається значенням в даний момент на його вході та його станом, а також першою функцією виходів. Значення на його другому виході в момент часу t визначається його станом в даний момент, а також другою функцією виходів. Стан автомату в момент часу t+І визначається значенням в даний момент на його вході та його станом, а також функцією переходів.

Рис. 8.6. С-автомат

Мови опису функціонування автоматів

Для того, щоб задати абстрактний автомат, потрібно задати всі п’ять об’єктів

{л'.яг.бЛ}.

Множини X, Б, У задаються як звичайні множини в математиці, наприклад, простим перелічуванням всіх її елементів, тому їх задання на практиці не викликає ніяких труднощів.

Найбільш трудомістким є задання функцій 5 Д , які власне і визначають алгоритм функціонування автомату. Для опису алгоритму функціонування автомату, тобто для задання 8 Д, існують різні засоби, які часто називають мовами. Існують стандартні та початкові мови. Стандартні мови задають автомат одним із трьох способів: матрично (таблично), графічно, аналітично. До початкових мов відносять первісні таблиці включень, логічні схеми алгоритмів і граф-схеми алгоритмів. Стандартні мови частіше застосовуються для задання автоматів загального виду, в той же час початкові мови знайшли широке застосування для часткових автоматів.

Мова матриць (таблиць) передбачає наявність двох таблиць: таблиці переходів і таблиці виходів, або однієї таблиці з’єднань.

Таблиця переходів задає відображення X х 5 —> 8, тобто задає функцію переходів

Приклад. Нехай на автомат поступають вхідні сигнали, які мають три букви, та нехай він має чотири стани: X = {хр х2, 5 = 5,, 53, 54}. В табл. 8.1 описано повністю визначений автомат для даного прикладу.

Таблиця 8.1

\Х(0 3(0\ |

Х1 |

Х2 |

ХЗ |

Б1 |

Б1 |

Б2 |

Б1 |

Б2 |

БЗ |

Б4 |

Б2 |

БЗ |

БЗ |

Б1 |

Б4 |

Б4 |

БЗ |

Б1 |

52 |

З першого рядка табл. 8.1 видно, що перебуваючи в стані 51 при поступленні вхідного сигналу XI автомат не змінює свого стану, так само як і при поступленні вхідного сигналу ХЗ, а при поступленні вхідного сигналу Х2 він перейде в стан 52. Подібним чином можна провести аналіз інших рядків таблиці.

Якщо автомат частковий, то для пар (х„ $,), для яких стан не визначений, в клітинці таблиці ставиться прочерк. Як видно, вигляд таблиці переходів не залежить від того, який тип автомату використовується: Мілі, Мура чи С-автомат.

Таблиці виходів цих автоматів відрізняються.

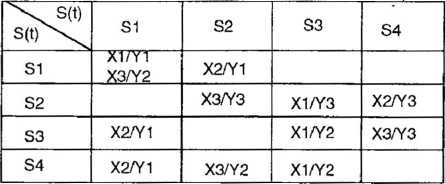

У клітинці таблиці виходів автомату Мілі ставиться вихідний сигнал ук, який формує автомат Мілі, що знаходиться в стані 5;- і на вході якого діє сигнал х.. Приклад повністю визначеного автомату Мілі з вхідним алфавітом X = {х,, х2, х3}, алфавітом станів; 5 = {5Р 52, 53,54/ та вихідним алфавітом У = {у,, у2, у3} наведено в табл. 8.2.

Таблиця

8.2

\Х(1)

Х1

Х2

ХЗ

Є1

У1

У1

У2

32

УЗ

УЗ

УЗ

БЗ

У2

У1

УЗ

Б4

У2

У1

УЗ

З першого рядка табл. 8.2 видно, що перебуваючи в стані Б1 при поступленні вхідного сигналу XI на виході автомату буде сформовано сигнал У1, так само, як і при поступленні вхідного сигналу Х2, а при поступленні вхідного сигналу ХЗ на виході автомату буде сформовано сигнал У2. Подібним чином можна провести аналіз інших рядків таблиці.

В таблиці виходів повністю визначеного автомату Мура кожному стану автомату призначається відповідний вихідний сигналу. Приклад повністю визначеного автомату Мура з алфавітом станів 5 = {$,, $2, 53, та вихідним алфавітом У = {у,, у2, наведено в табл. 8.3.

Таблиця

8.3

3(1)

У(і)

У1

32

У1

гз

У2

34

УЗ

З табл. 8.3 видно, що стану Б1 та Б2 автомату відповідає вихідний сигнал УІ, стану БЗ відповідає вихідний сигнал У2, а стану Б4 відповідає вихідний сигнал УЗ.

С-автомат буде задаватися двома таблицями виходів, перша з яких відповідає таблиці виходів автомату Мілі, а друга - таблиці автомату Мура.

На практиці таблиці переходів і таблиці виходів часто суміщаються в одну суміщену таблицю. Табл. 8.4 є суміщеною таблицею автомату Мілі для вищенаведеного прикладу.

\Х(() 3(1Г\ |

Х1 |

Х2 |

ХЗ |

в1 |

31/У1 |

S2/У^ |

Б1/У2 |

Б2 |

Б З/УЗ |

34/УЗ |

Б2/У3 |

вз |

Б3/У2 |

ві/п |

Б4/У3 |

в4 |

53/У2 |

гі/уі |

Б2/У3 |

З першого рядка табл. 8.4 видно, що перебуваючи в стані Б1 при поступленні вхідного сигналу XI автомат залишиться в тому ж стані, а на виході автомату буде сформовано сигнал У1, при поступленні вхідного сигналу Х2 автомат перейде в стан Б2, а на виході автомату буде сформовано сигнал Уі, при поступленні вхідного сигналу ХЗ автомат залишиться в тому ж стані, а на виході автомату буде сформовано сигнал У2. Подібним чином можна провести аналіз інших рядків таблиці.

Як вже зазначилось вище, можна задати керуючий автомат за допомогою єдиної таблиці з’єднань. Таблиця з’єднань абстрактного автомату є квадратною і містить стільки стовпців та рядків, скільки різних станів має даний автомат. В клітинці ставиться вхідний сигнал, під дією якого відбувається перехід автомату зі стану в стан. Якщо матрицею з’єднань задається автомат Мілі, то разом з вхідним сигналом вказується вихідний сигнал, який автомат Мілі видає, виконуючи перехід (табл. 8,5).

З першого рядка табл. 8.5 видно, що автомат залишається в тому ж стані Б1 при поступленні вхідних сигналів XI та ХЗ, і при цьому на його виході будуть відповідно сигнали У1, та У2, та переходить в стан Б2 при поступленні вхідного сигналу Х2, і при цьому на його виході буде сигнал У1. Подібним чином можна провести аналіз інших рядків таблиці.

Для автомату Мура в матриці з’єднань вихідні сигнали ставляться біля станів автомату, які ідентифікують рядки матриці.

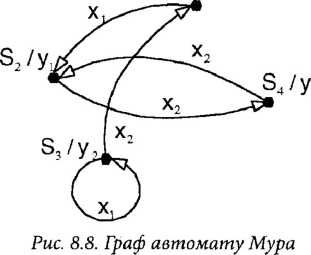

Мова графіки передбачає застосування для задання абстрактного автомату орієнтованого графа. Стан автомату зображається вершинами графа, а переходи між станами - дугами між відповідними вершинами. При цьому конкретній дузі графа приписується буква х1 вхідного алфавіту автомату, яка вказує на перехід при поступленні цього сигналу.

Мова аналітичних виразів передбачає задания автомату шляхом запису для кожного стану автомату відображення , яке містить набори з трьох об’єктів ук, причому тільки таких, які вказують на наявність переходу автомату зі стану 5^. в стан при дії вхідного сигналу хі і видачі при цьому вихідного сигналу ук.

Структурний синтез цифрових автоматів

Процес одержання структурної схеми, яка відображає склад логічних елементів та їхні зв’язки, називають структурним синтезом. В загальному випадку задача структурного синтезу зводиться до композиції деяких простих автоматів, тобто до пошуку способу з’єднань цих автоматів між собою. Як правило, ефективно розв’язується задача структурного синтезу тільки для певного набору простих автоматів певного виду - елементарних автоматів, які складаються з елементів пам’яті, що мають більше одного стійкого стану (елементарних автоматів з пам’яттю) та комбінаційних схем (елементарних автоматів без пам’яті).

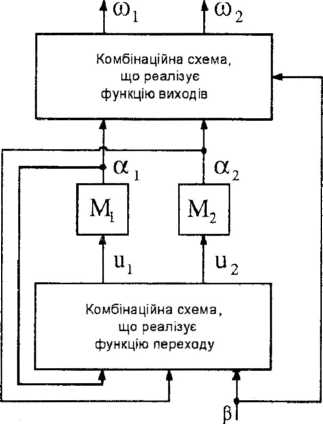

Метод синтезу, в основу якого покладені елементарні автомати, отримав назву канонічного методу структурного синтезу автоматів. Загальна структура елементарного автомату, що складається з пам’яті та комбінаційної схеми, представлена на рис. 8.9.

Елементарний автомат має кх входів р 1 р 2... р кх, ку виходів со,со2 та кБ виходів пам’яті станів ааа2...ак . Сигнали керування пам’яттю м],и2,...ик описуються за допомогою булевих функцій, які називаються функціями збудження. Таким чином, для побудови структурного автомату потрібно мати елементи пам’яті і набір логічних елементів, які утворюють функціонально повну систему для побудови комбінаційної схеми.

Канонічний метод структурного синтезу розділяють на наступні етапи:

кодування,

вибір типу та структури абстрактного автомату,

вибір елементів пам’яті,

побудова рівнянь булевих функцій збудження і виходів автомату,

побудова структурної схеми автомату.

Розглянемо кожен з етапів.

Кодування. Нагадаємо, що абстрактний автомат задається в вигляді А = (аг,5',У,8,Х}. При переході на структурний рівень множини сигналів X та У, а також сигнали Б потрібно зобразити у вигляді двійкового вектору.

Нехай 5 = {$р $2, $4, $9 5^, тоді к5 = ] /о&М, [ = ] log26 / = 3. Тобто для нумерації кожного стану потрібно 3 розряди, тоді s = {000,001,010,011,100,101}. Фізично в структурному автоматі буде три стани, кожен з яких може прийняти тільки два значення 0 або 1. Сукупність значень цих трьох станів буде відповідати одному із станів абстрактного автомату.

Приклад: автомат описується суміщеною таблицею переходів та виходів (табл. 8.6).

\Х(І) |

Х1 |

Х2 |

Э1 |

Б2/У1 |

Э1/У3 |

Б2 |

эз/уг |

Б1/У4 |

ЭЗ |

Є3/У1 |

Б2/У2 |

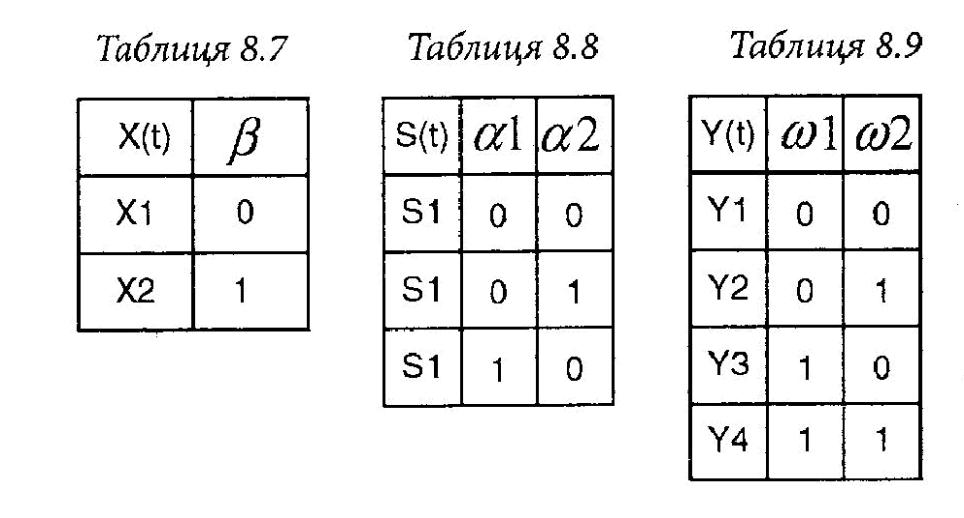

Тобто він має три стани М* = п = 3, два вхідних сигнали Мх = ш = 2 та чотири вихідних сигнали Му = 1 = 4. Вони відповідно можуть бути закодовані наступною кількістю роз- І рядів: К5 = 2, Кх = 1 та Ку = 2.

Результати кодування вхідних сигналів наведено в табл. 8.7, станів - в табл. 8.8, та : вихідних сигналів - в табл. 8.9

Тоді суміщена таблиця переходів та виходів (табл. 8.6) з закодованими входами, станами та виходами, буде мати вигляд табл. 8.10.

Побудова абстрактного автомату

Структурна схема цифрового автомату Мілі для розглядуваного прикладу має вигляд, показаний на рис. 8.10.

В якості елементів пам’яті структурного автомату можуть бути використані всі відомі типи тригерів, зокрема Б-тригери, КБ-тригери, Т-тригери, ДС-тригери.

Якщо в якості елементів пам’яті вибираються тригери, які мають вхід синхронізації, то структурний автомат буде синхронним, а якщо вибираються асинхронні тригери, то автомат буде асинхронним.

Побудова рівнянь булевих функцій збудження і виходів автомату.

Провівши кодування

та вибравши систему логічних елементів,

можна однозначно визначити структуру

комбінаційних схем автомату. Рівняння

булевих функцій будуються на основі

таблиці істинності функції збудження,

яка в свою чергу будується на основі

структурної таблиці переходів і таблиці

переходів елемента пам’яті. Для наведеної

вище таблиці маємо