- •Двнз «Чернівецький індустріальний коледж» архітектура комп’ютерів

- •Чернівці,

- •1.Історія розвитку обчислювальної техніки

- •2. Поняття про архітектуру еом. Принцип функціонування еом

- •38. Процесор векторного комп'ютера.

- •47. Функції арифметико-логічного пристрою. Способи обробки даних в арифметико-логічному пристрої

- •63. Частково-асоціативне відображення

- •82. Універсальна послідовна шина usb

- •1.Історія розвитку обчислювальної техніки

- •Покоління процесорів x86

- •Поняття архітектури і структурної організації комп’ютера

- •2. Поняття про архітектуру еом. Принцип функціонування еом Структура й принципи функціонування еом

- •3. Склад і призначення основних блоків

- •4. Архітектурні принципи Джона фон Неймана. Ненейманівські архітектури комп'ютерів

- •5. Апаратні і програмні засоби. Класифікація еом

- •Стандартні додатки Windows

- •Службові програми

- •Методи класифікації комп'ютерів.

- •Класифікація за призначенням

- •Великі еом (Main Frame)

- •МікроЕом

- •Персональні комп'ютери

- •Класифікація по рівню спеціалізації

- •Класифікація за розміром

- •Класифікація за сумісністю

- •6. Основні характеристики еом. Пк, особливості, класифікація, основні характеристики Основні характеристики пк

- •7. Персональні комп'ютери

- •8. Робочі станції. Багатотермінальні системи. Сервери

- •9. Кластерні комп'ютерні системи.

- •10. Суперкомп'ютери. Мікроконтролери. Спеціалізовані комп'ютери

- •11. Позиційні системи числення. Двійкові, вісімкові та шістнадцяткові числа

- •Двійкові, вісімкові та шістнадцяткові числа

- •12. Переведення чисел із системи числення з основою k у десяткову систему

- •13. Переведення чисел із десяткової системи у систему числення з основою k.

- •14. Прямий код. Обернений код. Доповняльний код. Способи представлення чисел

- •15. Числа з фіксованою комою. Числа із рухомою комою

- •16. Арифметичні операції. Ділення двійкових чисел

- •17. Арифметичні операції над двійковими числами у форматі з рухомою комою

- •18. Стандарт іеее-754. Розширений двійково-кодований десятковий код обміну ebcdic

- •19. Кодування алфавітно-цифрової інформації. Двійково-кодовані десяткові числа.

- •20. Американський стандартний код інформаційного обміну ascii. Стандарт кодування символів Unicode.

- •21. Кодування та виконання команд в комп'ютері

- •22. Виконання команд на рівні регістрів процессора.

- •23. Конвеєрне виконання команд

- •24. Класифікація архітектури комп'ютера за типом адресованої пам'яті.

- •25. Безпосередня адресація. Пряма адресація. Непряма адресація.

- •26. Відносна адресація. Базова адресація. Індексна адресація.

- •27. Сторінкова адресація. Неявна адресація. Стекова адресація. Використання стекової адресації.

- •28. Одношинна структура процесора.

- •29. Основні операції процесора. Вибірка слова з пам'яті. Запам'ятовування слова в пам'яті. Обмін даними між регістрами.

- •30. Багатошинна структура процесора.

- •31. Приклади виконання операцій в процесорі. Виконання операції додавання двох чисел.

- •32. Вимоги до процесора комп'ютера з простою системою команд. Базові принципи побудови процесора комп'ютера з простою системою команд.

- •33. Взаємодія процесора з пам'яттю в комп'ютері з простою системою команд.

- •34. Виконання команд в процесорі комп'ютера з простою системою команд. Фаза вибирання команди. Фаза декодування команди.

- •35. Конвеєрний процессор.

- •36. Мікродії ярусів конвеєрного процесора.

- •37. Суперскалярні процесори.

- •38. Процесор векторного комп'ютера.

- •39. Класифікація архітектури комп'ютера за рівнем суміщення опрацювання команд та даних.

- •40. Логічні операції.

- •1. Формальна логіка

- •2. Математична логіка

- •3. Програмування

- •41. Операція заперечення. Логічна 1. Логічне або. Виключне або.

- •42. Операції зсуву.

- •43. Операції відношення.

- •44. Арифметичні операції.

- •45. Операції обчислення елементарних функцій.

- •46. Операції перетворення даних.

- •47. Функції арифметико-логічного пристрою. Способи обробки даних в арифметико-логічному пристрої.

- •48. Елементарні операції арифметико-логічного пристрою.

- •49. Складні операції арифметико-логічного пристрою.

- •50. Структура арифметико-логічного пристрою.

- •51. Функції та методи побудови пристрою керування.

- •52. Пристрій керування з жорсткою логікою.

- •53. Пристрій керування на основі таблиць станів.

- •54. Пристрій мікропрограмного керування.

- •55. Порівняння пристроїв керування з жорсткою логікою та пристроїв мікропрограмного керування.

- •56 Ієрархічна організація пам'яті комп'ютера

- •57. Принцип ієрархічної організації пам'яті. Характеристики ефективності ієрархічної організації пам'яті

- •58. Кеш пам'ять в складі комп'ютера. Порядок взаємодії процесора і основної пам'яті через кеш пам'ять

- •59. Забезпечення ідентичності вмісту блоків кеш пам'яті і основної пам'яті

- •60. Функція відображення. Типи функцій відображення

- •61. Повністю асоціативне відображення

- •62. Пряме відображення

- •63. Частково-асоціативне відображення

- •64. Порядок заміщення блоків в кеш пам'яті з асоціативним відображенням

- •65. Підвищення ефективності кеш пам'яті

- •66. Статичний та динамічний розподіл пам'яті. Розподіл основної пам'яті за допомогою базових адрес

- •67. Віртуальна пам'ять. Сторінкова організація пам'яті

- •68. Основні правила сторінкової організації пам'яті. Реалізація сторінкової організації пам'яті

- •69. Апаратна реалізація сторінкової таблиці

- •70. Сегментна організація віртуальної пам'яті

- •71. Захист пам'яті від несанкціонованих звернень

- •72. Захист пам'яті за значеннями ключів

- •73. Кільцева схема захисту пам'яті

- •74. Архітектура системної плати

- •75. Синхронізація

- •76. Система шин

- •77. Особливості роботи шини

- •78. Характеристики шин пк

- •79. Шина pcmcia, vbl

- •80. Шина pci

- •82. Універсальна послідовна шина usb

- •83.Типи передач і формати інформації що передається

- •84. Шина scsi

- •85. Адресація пристроїв і передача даних

- •86. Система команд

- •87. Конфігурування пристроїв scsi

- •88. Ігровий адаптер Game-порт

- •89. Відеоадаптери

- •90. Послідовний інтерфейс. Сом-порт

- •91. Програмна модель сом-порта

- •92. Програмування послідовного зв’язку

- •93. Ініціалізація послідовного порта. Передача і прийом даних

- •95. Паралельний інтерфейс lpt-порт. Стандартний режим spp

- •96. Режим epp

- •97. Режим ecp

- •98. Узгодження режимів

- •99. Приклад програмування

- •100. Клавіатура

- •101. Під'єднання зовнішніх пристроїв до комп'ютера

- •102. Розпізнавання пристроїв введення-виведення

- •103. Методи керування введенням-виведенням

- •104. Програмно-кероване введення-виведення.

- •105. Система переривання програм та організація введення-виведення за перериваннями

- •106. Прямий доступ до пам'яті. Введення-виведення під керуванням периферійних процесорів

- •107. Мультиплексний та селекторний канали введення-виведення

- •108. Використання принципів паралельної обробки інформації в архітектурі комп'ютера

- •109. Вибір кількості процесорів в багатопроцесорній системі

- •110. Багатопотокова обробка інформації. Окр

- •111. Класифікація Шора. Класифікація Фліна

- •112. Типи архітектур систем окмд. Типи архітектур систем мкмд

- •113.Організація комп'ютерних систем із спільною пам'яттю

- •114. Організація комп'ютерних систем із розподіленою пам'яттю

- •115. Комунікаційні мережі багатопроцесорних систем

49. Складні операції арифметико-логічного пристрою.

Крім вище перерахованих елементарних операцій, в АЛП виконується велика кількість складних операцій, тобто таких, які реалізуються на основі елементарних. Можна виділити наступний перелік складних операцій АЛП, сформований на основі аналізу системи команд сучасних комп’ютерів:

логічні операції (логічне множення, логічне додавання, інверсія і т. д.) над двійковими числами;

операції зсуву (вправо, вліво) на задану кількість розрядів, причому в одному такті зсув може бути здійснено як на один розряд, так і на декілька розрядів;

арифметичні операції (додавання, віднімання, множення та ділення) над двійковими числами;

операції відношення: менше, більше, рівне, менше-рівне, більше-рівне;

операції обчислення елементарних функцій типу exp X, In X, Sin X, Cos X, Sh X, Ch X, піднесення до степеня Am; arctg y/x;

операції обробки символів та рядків символів.

Потрібно відзначити, що розглянуті в розділі 4 операції перетворення даних (перетворення із формату з фіксованою в формат з рухомою комою і навпаки, перетворення з двійково-десяткового коду в двійковий та навпаки і т. д.), так само як операції реорганізації масивів і визначення їх параметрів: сортування, пошук максимуму або мінімуму, вибір заданого масиву, зсув елементів масиву, стиск масиву, а також операції пошуку символу, зсув, заміна символів в рядку, пакування рядків символів, порівняння рядків символів виконуються в процесорі на основі елементарних та основних арифметичних і логічних операцій. Разом з тим, в останніх комп’ютерах з метою підвищення продуктивності та в зв’язку з широким використанням засобів телекомунікацій та мультимедіа до складу АЛП вводяться окремі блоки для виконання вищеназваних складних операцій, а також операцій типу кодування, компресії, шифрування даних і т. д.

Розглянемо питання реалізації в АЛП складних операцій більш детально.

50. Структура арифметико-логічного пристрою.

В більшості комп’ютерів АЛП виконує операції над двома вхідними даними, тобто є двомісним, та видає один вихідний результат, як це показано на рис. 7.7. При цьому спочатку операнди А та В записуються у вхідні регістри Ргі і Рг2, та поступають на входи АЛП через мультиплексори МП1 і МП2, які керуються сигналами У1 та У2. Після цього в АЛП виконується задана операція, тип якої задається кодом операції. Результат операції поступає на вихід АЛП та записується у вихідний регістр РгЗ. З виходу вказаного регістра результат поступає в регістровий файл процесора, а крім того, якщо він потрібний для виконання наступної операції, він поступає через мультиплексори МП1 або МП2 на один з входів АЛП, що здійснюються шляхом подання відповідних значень керуючих сигналів на ходи мультиплексорів.

Рис. 7.7. Типова

структура АЛП

В сучасних комп’ютерах АЛП є багатоблоковими. В них окремі групи операцій над кожним типом операндів виконуються окремими блоками, які називаються операційними пристроями. Це дозволяє підвищити продуктивність АЛП за рахунок паралельного виконання операцій

До складу АЛП, крім вищеописаного пристрою для виконання елементарних операцій, входять п операційних пристроїв ОП1, ОП2,..., ОПп, які виконують складні операції. Кількість п цих пристроїв та їх функції визначаються конструкторами комп’ютера залежно від сфери його використання. Входи та виходи операційних пристроїв АЛП підключаються до його інформаційних входів та виходів за допомогою комутуючих мереж, якими керує код виконуваної операції. Цим же кодом вибирається тип виконуваної операції в пристрої для виконання елементарних операцій та в операційному пристрої, якщо він може виконувати декілька операцій.

До складу АЛП, крім вищеописаного пристрою для виконання елементарних операцій, входять п операційних пристроїв ОП1, ОП2,..., ОПп, які виконують складні операції. Кількість п цих пристроїв та їх функції визначаються конструкторами комп’ютера залежно від сфери його використання. Входи та виходи операційних пристроїв АЛП підключаються до його інформаційних входів та виходів за допомогою комутуючих мереж, якими керує код виконуваної операції. Цим же кодом вибирається тип виконуваної операції в пристрої для виконання елементарних операцій та в операційному пристрої, якщо він може виконувати декілька операцій.

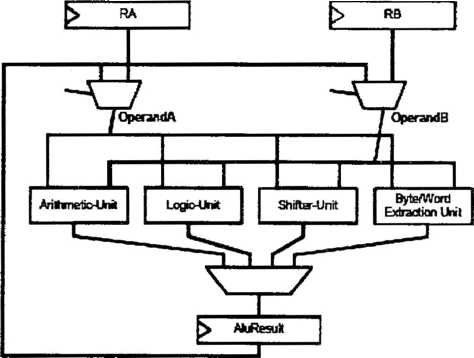

Як приклад АЛП реального комп’ютера, на рис. 7.9 представлено АЛП програмованого процесора NIOS 2.0 фірми Altera. Як бачимо, цей АЛП має наступні блоки: два вхідних регістри RA та RB, два двовходових мультиплексори для подачі даних на обробку або з вхідних регістрів, або з вихідного регістра, операційні пристрої - арифметичний, логічний, зсуву та виділення байтів і слів, а також вихідний мультиплексор, необхідний для підключення до входу вихідного регістра виходу відповідного операційного пристрою, і сам вихідний регістр.

Рис. 7.9. Структура

АЛП програмованого процесора N10S 2.0

фірми Altera

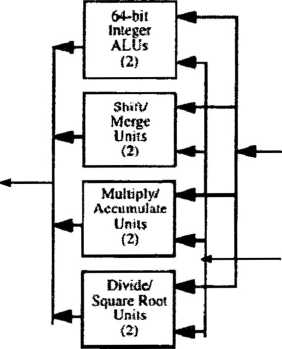

Ще

більшу кількість паралельних блоків

мають АЛП процесорів UltraSPARC фірми Sun

Microsystems та РА-8000 фірми Huwlett-Packard, структури

яких наведено на рис. 7.10а та рис. 7.10b

відповідно.

Ще

більшу кількість паралельних блоків

мають АЛП процесорів UltraSPARC фірми Sun

Microsystems та РА-8000 фірми Huwlett-Packard, структури

яких наведено на рис. 7.10а та рис. 7.10b

відповідно.

Рис. 7.10. Структури

АЛП процесорів UltraSPARC фірми Sun Microsystems

(а) та РА-8000 фірми Huwlett-Packard (b)

АЛП процесора UltraSPARC фірми Sun Microsystems має два блоки для виконання елементарних операцій над цілими числами (ALU1 та ALU2), перемножувач та поділь ник чисел з фіксованою комою (MUL, DIV), два АЛП для обробки даних з рухомою комою (FALU0 та FALU1). АЛП процесора UltraSPARC може виконувати до чотирьох операцій за один такт.

Процесор РА-8000 фірми Huwlett-Packard є суперскалярним процесором з невпо- рядкованим виконанням команд, який може виконувати до чотирьох команд за один такт. Його АЛП включає по два наступних блоки (длоки, розміщені зверху донизу на рис. 7.10Ь): 64-розрядне АЛП для виконання елементарних операцій над цілочисловими даними, операційний пристрій зсуву та сортування, операційний пристрій множення та накопичення, операційний пристрій ділення та добування квадратного кореня.

Функції пристрою для виконання елементарних операцій раніше було розглянуто. Розглянемо далі організацію роботи операційних пристроїв.