- •Двнз «Чернівецький індустріальний коледж» архітектура комп’ютерів

- •Чернівці,

- •1.Історія розвитку обчислювальної техніки

- •2. Поняття про архітектуру еом. Принцип функціонування еом

- •38. Процесор векторного комп'ютера.

- •47. Функції арифметико-логічного пристрою. Способи обробки даних в арифметико-логічному пристрої

- •63. Частково-асоціативне відображення

- •82. Універсальна послідовна шина usb

- •1.Історія розвитку обчислювальної техніки

- •Покоління процесорів x86

- •Поняття архітектури і структурної організації комп’ютера

- •2. Поняття про архітектуру еом. Принцип функціонування еом Структура й принципи функціонування еом

- •3. Склад і призначення основних блоків

- •4. Архітектурні принципи Джона фон Неймана. Ненейманівські архітектури комп'ютерів

- •5. Апаратні і програмні засоби. Класифікація еом

- •Стандартні додатки Windows

- •Службові програми

- •Методи класифікації комп'ютерів.

- •Класифікація за призначенням

- •Великі еом (Main Frame)

- •МікроЕом

- •Персональні комп'ютери

- •Класифікація по рівню спеціалізації

- •Класифікація за розміром

- •Класифікація за сумісністю

- •6. Основні характеристики еом. Пк, особливості, класифікація, основні характеристики Основні характеристики пк

- •7. Персональні комп'ютери

- •8. Робочі станції. Багатотермінальні системи. Сервери

- •9. Кластерні комп'ютерні системи.

- •10. Суперкомп'ютери. Мікроконтролери. Спеціалізовані комп'ютери

- •11. Позиційні системи числення. Двійкові, вісімкові та шістнадцяткові числа

- •Двійкові, вісімкові та шістнадцяткові числа

- •12. Переведення чисел із системи числення з основою k у десяткову систему

- •13. Переведення чисел із десяткової системи у систему числення з основою k.

- •14. Прямий код. Обернений код. Доповняльний код. Способи представлення чисел

- •15. Числа з фіксованою комою. Числа із рухомою комою

- •16. Арифметичні операції. Ділення двійкових чисел

- •17. Арифметичні операції над двійковими числами у форматі з рухомою комою

- •18. Стандарт іеее-754. Розширений двійково-кодований десятковий код обміну ebcdic

- •19. Кодування алфавітно-цифрової інформації. Двійково-кодовані десяткові числа.

- •20. Американський стандартний код інформаційного обміну ascii. Стандарт кодування символів Unicode.

- •21. Кодування та виконання команд в комп'ютері

- •22. Виконання команд на рівні регістрів процессора.

- •23. Конвеєрне виконання команд

- •24. Класифікація архітектури комп'ютера за типом адресованої пам'яті.

- •25. Безпосередня адресація. Пряма адресація. Непряма адресація.

- •26. Відносна адресація. Базова адресація. Індексна адресація.

- •27. Сторінкова адресація. Неявна адресація. Стекова адресація. Використання стекової адресації.

- •28. Одношинна структура процесора.

- •29. Основні операції процесора. Вибірка слова з пам'яті. Запам'ятовування слова в пам'яті. Обмін даними між регістрами.

- •30. Багатошинна структура процесора.

- •31. Приклади виконання операцій в процесорі. Виконання операції додавання двох чисел.

- •32. Вимоги до процесора комп'ютера з простою системою команд. Базові принципи побудови процесора комп'ютера з простою системою команд.

- •33. Взаємодія процесора з пам'яттю в комп'ютері з простою системою команд.

- •34. Виконання команд в процесорі комп'ютера з простою системою команд. Фаза вибирання команди. Фаза декодування команди.

- •35. Конвеєрний процессор.

- •36. Мікродії ярусів конвеєрного процесора.

- •37. Суперскалярні процесори.

- •38. Процесор векторного комп'ютера.

- •39. Класифікація архітектури комп'ютера за рівнем суміщення опрацювання команд та даних.

- •40. Логічні операції.

- •1. Формальна логіка

- •2. Математична логіка

- •3. Програмування

- •41. Операція заперечення. Логічна 1. Логічне або. Виключне або.

- •42. Операції зсуву.

- •43. Операції відношення.

- •44. Арифметичні операції.

- •45. Операції обчислення елементарних функцій.

- •46. Операції перетворення даних.

- •47. Функції арифметико-логічного пристрою. Способи обробки даних в арифметико-логічному пристрої.

- •48. Елементарні операції арифметико-логічного пристрою.

- •49. Складні операції арифметико-логічного пристрою.

- •50. Структура арифметико-логічного пристрою.

- •51. Функції та методи побудови пристрою керування.

- •52. Пристрій керування з жорсткою логікою.

- •53. Пристрій керування на основі таблиць станів.

- •54. Пристрій мікропрограмного керування.

- •55. Порівняння пристроїв керування з жорсткою логікою та пристроїв мікропрограмного керування.

- •56 Ієрархічна організація пам'яті комп'ютера

- •57. Принцип ієрархічної організації пам'яті. Характеристики ефективності ієрархічної організації пам'яті

- •58. Кеш пам'ять в складі комп'ютера. Порядок взаємодії процесора і основної пам'яті через кеш пам'ять

- •59. Забезпечення ідентичності вмісту блоків кеш пам'яті і основної пам'яті

- •60. Функція відображення. Типи функцій відображення

- •61. Повністю асоціативне відображення

- •62. Пряме відображення

- •63. Частково-асоціативне відображення

- •64. Порядок заміщення блоків в кеш пам'яті з асоціативним відображенням

- •65. Підвищення ефективності кеш пам'яті

- •66. Статичний та динамічний розподіл пам'яті. Розподіл основної пам'яті за допомогою базових адрес

- •67. Віртуальна пам'ять. Сторінкова організація пам'яті

- •68. Основні правила сторінкової організації пам'яті. Реалізація сторінкової організації пам'яті

- •69. Апаратна реалізація сторінкової таблиці

- •70. Сегментна організація віртуальної пам'яті

- •71. Захист пам'яті від несанкціонованих звернень

- •72. Захист пам'яті за значеннями ключів

- •73. Кільцева схема захисту пам'яті

- •74. Архітектура системної плати

- •75. Синхронізація

- •76. Система шин

- •77. Особливості роботи шини

- •78. Характеристики шин пк

- •79. Шина pcmcia, vbl

- •80. Шина pci

- •82. Універсальна послідовна шина usb

- •83.Типи передач і формати інформації що передається

- •84. Шина scsi

- •85. Адресація пристроїв і передача даних

- •86. Система команд

- •87. Конфігурування пристроїв scsi

- •88. Ігровий адаптер Game-порт

- •89. Відеоадаптери

- •90. Послідовний інтерфейс. Сом-порт

- •91. Програмна модель сом-порта

- •92. Програмування послідовного зв’язку

- •93. Ініціалізація послідовного порта. Передача і прийом даних

- •95. Паралельний інтерфейс lpt-порт. Стандартний режим spp

- •96. Режим epp

- •97. Режим ecp

- •98. Узгодження режимів

- •99. Приклад програмування

- •100. Клавіатура

- •101. Під'єднання зовнішніх пристроїв до комп'ютера

- •102. Розпізнавання пристроїв введення-виведення

- •103. Методи керування введенням-виведенням

- •104. Програмно-кероване введення-виведення.

- •105. Система переривання програм та організація введення-виведення за перериваннями

- •106. Прямий доступ до пам'яті. Введення-виведення під керуванням периферійних процесорів

- •107. Мультиплексний та селекторний канали введення-виведення

- •108. Використання принципів паралельної обробки інформації в архітектурі комп'ютера

- •109. Вибір кількості процесорів в багатопроцесорній системі

- •110. Багатопотокова обробка інформації. Окр

- •111. Класифікація Шора. Класифікація Фліна

- •112. Типи архітектур систем окмд. Типи архітектур систем мкмд

- •113.Організація комп'ютерних систем із спільною пам'яттю

- •114. Організація комп'ютерних систем із розподіленою пам'яттю

- •115. Комунікаційні мережі багатопроцесорних систем

47. Функції арифметико-логічного пристрою. Способи обробки даних в арифметико-логічному пристрої.

Функції арифметико-логічного пристрою

Арифметико-логічний пристрій (АЛП) призначений для виконання арифметичних, логічних та інших операцій обробки даних над операндами, які представляють собою двійкові числа з фіксованою та рухомою комою, двійково-десяткові числа, команди, адреси, логічні коди, алфавітно-цифрові коди. АЛП є одним з основних вузлів процесора. Інтерфейс АЛП, тобто його зв’язки з іншими вузлами процесора, показано на рис. 7.1.

Вхідні дані поступають в АЛП з регістрового файлу процесора або з основної пам’яті (залежно від типу архітектури комп’ютера), до яких записуються і вихідні дані. Код операції поступає з поля коду операції виконуваної команди, яка зберігається в регістрі команди РгК, а сигнали станів АЛП повідомляють пристрій керування про стан ходу виконання операцій та фіксуються в регістрі слова стану програми регістрової пам’яті процесора.

Арифметико-логічний пристрій процесора - це комбінаційна схема (КС) без внутрішньої пам’яті, яка здатна виконувати набір елементарних операцій та деяку множину складних операцій, які ініціюються командами обробки даних з системи команд комп’ютера. В потужних комп’ютерах, а останнім часом і в багатьох однокристальних комп’ютерах, використовуються багатоблокові АЛП з внутрішньою регістровою пам’яттю на основі табличних, однотактових, багатотактових та конвеєрних операційних пристроїв. Тип виконуваної операції вказується кодом на вході керування АЛП. Типово в АЛП виконуються такі операції: зсув - зміщення кодів, які зберігаються в регістрах, вліво або вправо на задане число розрядів; додавання до слова І або -1 - операція рахунку; дешифрування - перетворення двійкового коду в однорядний код; шифрування перетворення однорядного коду в двійковий; порівняння - визначення відношення старшинства двох слів або їх рівності; порозрядне доповнення - формування оберненого коду; порозрядні логічні множення і додавання двох слів; порозрядне додавання двох слів за модулем; сума двох чисел. В багатьох комп’ютерах цей перелік розширений більш складними операціями, наприклад арифметичними, відношення, обробки рядків символів, обчислення елементарних функцій і т. д.

Залежно від способу обробки операндів АЛП діляться на послідовні, послідовно- паралельні та паралельні. В першому випадку обробка операндів в АЛП здійснюється послідовно в часі над кожним розрядом, тоді як в останньому операції здійснюються паралельно в часі над всіма розрядами операндів.

За способом представлення чисел розділяють АЛП з фіксованою та з рухомою комою, причому перші можуть бути орієнтовані на обробку цілих або дробових чисел.

Залежно від способу виконання операцій АЛП діляться на однотактові, коли задана операція виконується за один такт, та багатотактові, коли для виконання операції потрібно виконати деяку кількість тактів.

АЛП можуть бути конвеєрними або скалярними. Використання конвеєрного принципу обробки даних дозволяє суттєво підвищити продуктивність АЛП та комп’ютера в цілому.

За характером використання елементів АЛП діляться на одно- та багатоблокові. В одноблокових (багатофункціональних) АЛП всі операції над всіма типами операндів виконуються тими ж вузлами, які комутуються відповідним чином залежно від потрібного режиму роботи. В багатоблокових АЛП окремі групи операцій над кожним типом операндів виконуються'окремими блоками. Це дозволяє підвищити продуктивність АЛП за рахунок паралельного виконання операцій.

Способи обробки даних в арифметико-логічному пристрої

Залежно від способу обробки операндів АЛП діляться на послідовні, послідовно- паралельні та паралельні.

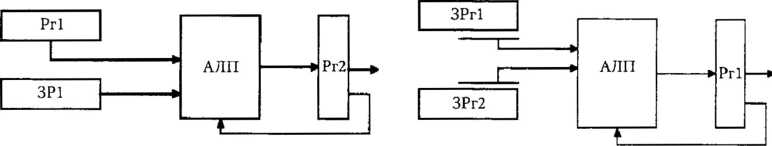

В послідовних АЛП обробка операндів здійснюється послідовно в часі над кожним розрядом, як це показано на рис. 7.2.

Рис. 7.2. Послідовний

спосіб обробки даних в АЛП

Тут на вході АЛП є зсувні регістри ЗРгІ та ЗРг2, з яких дані порозрядно поступають на обробку. Результат з АЛП також порозрядно поступає в вихідний зсувний регістр ЗРгЗ. В кожному такті операнди в зсувних регістрах зміщуються на один розряд вправо. Крім того, можливий зворотний зв’язок з вихідного регістра до входу АЛП. Оскільки обробка здійснюється порозрядно, то для отримання результату потрібно як мінімум п тактів, де п - розрядність операндів. Для складних операцій кількість тактів може становити п2 і більше. Тобто, при використанні цього способу АЛП характеризується малою швидкодією. Разом з тим, він знаходить досить широке застосування при проектуванні малогабаритних комп’ютерів завдяки малим витратам обладнання на побудову таких АЛП.

В паралельних АЛП операції виконуються одночасно над всіма розрядами операндів, як це показано на рис. 7.3.

Рис. 7.3. Паралельний

спосіб обробки даних в АЛП

Тут на вході АЛП є регістри Ргі та Рг2, з яких дані паралельно поступають на обробку. Результат також паралельно поступає в вихідний регістр РгЗ. Оскільки обробка здійснюється паралельно, вона виконується протягом лише одного такту незалежно від розрядності.операндів. Тобто АЛП з паралельним способом обробки даних характеризується високою швидкодією, що і є причиною його широкого використання. Разом з тим, такий АЛП характеризується великими витратами обладнання на його побудову Послідовно-паралельний спосіб обробки даних є проміжним стосовно швидкодії та затрат обладнання в порівнянні з вище розглянутими послідовним та паралельним способами. Тут одне з вхідних даних може поступати на обробку в АЛП паралельно, а інше послідовно з видачею проміжного результату в паралельному коді, як це показано на рис. 7.4 а, або вхідні дані можуть поступати в АЛП групами по к і гп розрядів, як це показано на рис. 7.4 Ь, та подаватись в вихідний регістр паралельно, або також групами.

а Ь

Рис. 7.4.

Послідовно-паралельний спосіб обробки

даних в АЛП