- •Двнз «Чернівецький індустріальний коледж» архітектура комп’ютерів

- •Чернівці,

- •1.Історія розвитку обчислювальної техніки

- •2. Поняття про архітектуру еом. Принцип функціонування еом

- •38. Процесор векторного комп'ютера.

- •47. Функції арифметико-логічного пристрою. Способи обробки даних в арифметико-логічному пристрої

- •63. Частково-асоціативне відображення

- •82. Універсальна послідовна шина usb

- •1.Історія розвитку обчислювальної техніки

- •Покоління процесорів x86

- •Поняття архітектури і структурної організації комп’ютера

- •2. Поняття про архітектуру еом. Принцип функціонування еом Структура й принципи функціонування еом

- •3. Склад і призначення основних блоків

- •4. Архітектурні принципи Джона фон Неймана. Ненейманівські архітектури комп'ютерів

- •5. Апаратні і програмні засоби. Класифікація еом

- •Стандартні додатки Windows

- •Службові програми

- •Методи класифікації комп'ютерів.

- •Класифікація за призначенням

- •Великі еом (Main Frame)

- •МікроЕом

- •Персональні комп'ютери

- •Класифікація по рівню спеціалізації

- •Класифікація за розміром

- •Класифікація за сумісністю

- •6. Основні характеристики еом. Пк, особливості, класифікація, основні характеристики Основні характеристики пк

- •7. Персональні комп'ютери

- •8. Робочі станції. Багатотермінальні системи. Сервери

- •9. Кластерні комп'ютерні системи.

- •10. Суперкомп'ютери. Мікроконтролери. Спеціалізовані комп'ютери

- •11. Позиційні системи числення. Двійкові, вісімкові та шістнадцяткові числа

- •Двійкові, вісімкові та шістнадцяткові числа

- •12. Переведення чисел із системи числення з основою k у десяткову систему

- •13. Переведення чисел із десяткової системи у систему числення з основою k.

- •14. Прямий код. Обернений код. Доповняльний код. Способи представлення чисел

- •15. Числа з фіксованою комою. Числа із рухомою комою

- •16. Арифметичні операції. Ділення двійкових чисел

- •17. Арифметичні операції над двійковими числами у форматі з рухомою комою

- •18. Стандарт іеее-754. Розширений двійково-кодований десятковий код обміну ebcdic

- •19. Кодування алфавітно-цифрової інформації. Двійково-кодовані десяткові числа.

- •20. Американський стандартний код інформаційного обміну ascii. Стандарт кодування символів Unicode.

- •21. Кодування та виконання команд в комп'ютері

- •22. Виконання команд на рівні регістрів процессора.

- •23. Конвеєрне виконання команд

- •24. Класифікація архітектури комп'ютера за типом адресованої пам'яті.

- •25. Безпосередня адресація. Пряма адресація. Непряма адресація.

- •26. Відносна адресація. Базова адресація. Індексна адресація.

- •27. Сторінкова адресація. Неявна адресація. Стекова адресація. Використання стекової адресації.

- •28. Одношинна структура процесора.

- •29. Основні операції процесора. Вибірка слова з пам'яті. Запам'ятовування слова в пам'яті. Обмін даними між регістрами.

- •30. Багатошинна структура процесора.

- •31. Приклади виконання операцій в процесорі. Виконання операції додавання двох чисел.

- •32. Вимоги до процесора комп'ютера з простою системою команд. Базові принципи побудови процесора комп'ютера з простою системою команд.

- •33. Взаємодія процесора з пам'яттю в комп'ютері з простою системою команд.

- •34. Виконання команд в процесорі комп'ютера з простою системою команд. Фаза вибирання команди. Фаза декодування команди.

- •35. Конвеєрний процессор.

- •36. Мікродії ярусів конвеєрного процесора.

- •37. Суперскалярні процесори.

- •38. Процесор векторного комп'ютера.

- •39. Класифікація архітектури комп'ютера за рівнем суміщення опрацювання команд та даних.

- •40. Логічні операції.

- •1. Формальна логіка

- •2. Математична логіка

- •3. Програмування

- •41. Операція заперечення. Логічна 1. Логічне або. Виключне або.

- •42. Операції зсуву.

- •43. Операції відношення.

- •44. Арифметичні операції.

- •45. Операції обчислення елементарних функцій.

- •46. Операції перетворення даних.

- •47. Функції арифметико-логічного пристрою. Способи обробки даних в арифметико-логічному пристрої.

- •48. Елементарні операції арифметико-логічного пристрою.

- •49. Складні операції арифметико-логічного пристрою.

- •50. Структура арифметико-логічного пристрою.

- •51. Функції та методи побудови пристрою керування.

- •52. Пристрій керування з жорсткою логікою.

- •53. Пристрій керування на основі таблиць станів.

- •54. Пристрій мікропрограмного керування.

- •55. Порівняння пристроїв керування з жорсткою логікою та пристроїв мікропрограмного керування.

- •56 Ієрархічна організація пам'яті комп'ютера

- •57. Принцип ієрархічної організації пам'яті. Характеристики ефективності ієрархічної організації пам'яті

- •58. Кеш пам'ять в складі комп'ютера. Порядок взаємодії процесора і основної пам'яті через кеш пам'ять

- •59. Забезпечення ідентичності вмісту блоків кеш пам'яті і основної пам'яті

- •60. Функція відображення. Типи функцій відображення

- •61. Повністю асоціативне відображення

- •62. Пряме відображення

- •63. Частково-асоціативне відображення

- •64. Порядок заміщення блоків в кеш пам'яті з асоціативним відображенням

- •65. Підвищення ефективності кеш пам'яті

- •66. Статичний та динамічний розподіл пам'яті. Розподіл основної пам'яті за допомогою базових адрес

- •67. Віртуальна пам'ять. Сторінкова організація пам'яті

- •68. Основні правила сторінкової організації пам'яті. Реалізація сторінкової організації пам'яті

- •69. Апаратна реалізація сторінкової таблиці

- •70. Сегментна організація віртуальної пам'яті

- •71. Захист пам'яті від несанкціонованих звернень

- •72. Захист пам'яті за значеннями ключів

- •73. Кільцева схема захисту пам'яті

- •74. Архітектура системної плати

- •75. Синхронізація

- •76. Система шин

- •77. Особливості роботи шини

- •78. Характеристики шин пк

- •79. Шина pcmcia, vbl

- •80. Шина pci

- •82. Універсальна послідовна шина usb

- •83.Типи передач і формати інформації що передається

- •84. Шина scsi

- •85. Адресація пристроїв і передача даних

- •86. Система команд

- •87. Конфігурування пристроїв scsi

- •88. Ігровий адаптер Game-порт

- •89. Відеоадаптери

- •90. Послідовний інтерфейс. Сом-порт

- •91. Програмна модель сом-порта

- •92. Програмування послідовного зв’язку

- •93. Ініціалізація послідовного порта. Передача і прийом даних

- •95. Паралельний інтерфейс lpt-порт. Стандартний режим spp

- •96. Режим epp

- •97. Режим ecp

- •98. Узгодження режимів

- •99. Приклад програмування

- •100. Клавіатура

- •101. Під'єднання зовнішніх пристроїв до комп'ютера

- •102. Розпізнавання пристроїв введення-виведення

- •103. Методи керування введенням-виведенням

- •104. Програмно-кероване введення-виведення.

- •105. Система переривання програм та організація введення-виведення за перериваннями

- •106. Прямий доступ до пам'яті. Введення-виведення під керуванням периферійних процесорів

- •107. Мультиплексний та селекторний канали введення-виведення

- •108. Використання принципів паралельної обробки інформації в архітектурі комп'ютера

- •109. Вибір кількості процесорів в багатопроцесорній системі

- •110. Багатопотокова обробка інформації. Окр

- •111. Класифікація Шора. Класифікація Фліна

- •112. Типи архітектур систем окмд. Типи архітектур систем мкмд

- •113.Організація комп'ютерних систем із спільною пам'яттю

- •114. Організація комп'ютерних систем із розподіленою пам'яттю

- •115. Комунікаційні мережі багатопроцесорних систем

38. Процесор векторного комп'ютера.

Вище були розглянуті скалярні та суперскалярні процесори, в яких операції виконуються над скалярними даними. Однак існує значна кількість завдань, коли опрацюванню за одними процедурами підлягають великі масиви (вектори) даних. У цьому випадку виглядає доцільним розгляд можливості модифікації комп’ютера під виконання цього класу завдань. До цих пір така модифікація здійснювалась в потужних комп’ютерах, але на даний час вона почала поширюватись на всі типи комп’ютерів. Відповідно комп’ютери, орієнтовані на опрацювання векторів даних, дістали назву векторних.

Різницю між виконанням скалярної та векторної операції наглядно відображає рис. 4.17, з якого видно, що скалярна операція передбачає виконання додавання над двома даними, тоді як векторна - над двома векторами даних.

Аби зрозуміти стиль програмування векторних комп’ютерів, наведемо приклад програми із скалярними і векторними кодами. Запишемо програму обчислення виразу У= а * X + У, де У, X - вектори, а а - скаляр. Нехай вектори мають довжину по 64 елементи. Векторна програма має вигляд:

LD . |

F0, а |

; load scalar a |

LV |

VI, Rx |

; load vector X |

MULTS |

V2, F0, VI |

; vector-scalar mult. |

LV |

V3, Ry |

; load vector Y |

ADDV |

V4, V2, V3 |

; add |

SV |

Ry, V4 |

; store vector |

Відповідна скалярна програма має вигляд:

|

LD ADDI |

F0,a R4,Rx,#512 |

; last address to |

Loop: |

load LD |

F2,0(Rx) |

; load X(l) |

|

MULTD |

F2,F0>,F2 |

; a*X(l) |

|

LD |

F4, 0(Ry) |

; load Y(l) |

|

ADDD |

F4,F2,F4 |

; a*X(l)+Y(l) |

|

SD |

F4,0(Ry) |

; store into Y(l) |

|

ADDI |

Rx,Rx,#8 |

; increment index |

|

ADDI |

Ry,Ry,#8 |

; increment index |

|

SUB |

R20,R4,Rx |

; compute bound |

|

BNZ |

R20, loop |

; check if done |

У скалярній програмі курсивом позначено залежності, яких немає у векторному варіанті програми. Обидва варіанти програми можна порівняти за наступними кількісними характеристиками:

За кількістю операцій: 578(2+9*64) проти 321(1+5*64); кількість операцій у векторній програмі зменшено в 1,8 разу

За кількістю команд: 578(2+9*64) проти 6-ти команд у векторній програмі; перевага в 96 разів.

В таблиці 4.3 наведені характеристики кількох промислових векторних комп’ютерів, з якої видно доцільність їх створення з огляду на досягнуту продуктивність.

Тип машини |

Рік випуску |

Частота, MHz |

Кількість регістрів |

Кількість елементів |

Кількість пристроїв float point |

Кількість пристроїв load/store |

Продуктив ність (MFLOPS) |

Cray-1 |

1976 |

80 |

8 |

64 |

6 |

1 |

160 |

Cray XMP |

1983 |

120 |

8 |

64 |

8 |

2L, IS |

940 |

Cray YMP |

1988 |

166 |

8 |

64 |

8 |

2L, IS |

2667 |

Cray C-90 |

1991 |

240 |

8 |

128 |

8 |

4 |

15238(16) |

Cray T-90 |

1996 |

455 |

8 |

128 |

8 |

4 |

57600(32) |

Conv. C-l |

1984 |

10 |

8 |

128 |

4 |

1 |

20(1) |

Conv. С-4 |

1994 |

133 |

16 |

128 |

3 |

1 |

3240(4) |

Fuj. VP200 |

1982 |

133 |

8-256 |

32-1024 |

3 |

2 |

533(1) |

Fuj. VP300 |

1996 |

100 |

8-256 |

32-1024 |

3 |

2 |

N/A |

NEC SX/2 |

1984 |

160 |

8 + 8К |

256 + var |

16 |

8 |

1300(1) |

NEC SX/3 |

1995 |

400 |

8 + 8К |

256 + var |

16 |

8 |

25600(4) |

Таким чином, процесори векторних комп’ютерів виконують команди над векторами даних. Структура цих процесорів за складом та зв’язками повторює вже розглянуті вище структури процесорів, тобто це можуть бути процесори векторних комп’ютерів із складною та простою системою команд, конвеєрні та суперконвеєрні, а також процесори супервекторних комп’ютерів, коли в процесорі є декілька конвеєрів команд. Основна їх відмінність - забезпечення одночасного виконання однієї команди над вектором даних. Це, зокрема, дозволяє будувати 'їх блоки виконання команд за конвеєрним принципом і при цьому позбутися конфліктів, які суттєво гальмують роботу конвеєра чи ускладнюють його структуру.

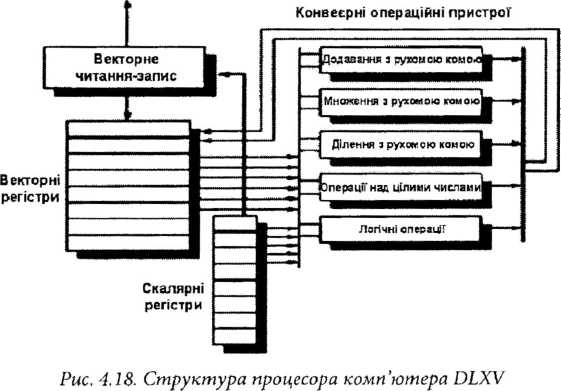

Для вияснення базових принципів побудови процесорів векторних комп’ютерів розглянемо структуру та систему команд процесора векторного варіанта комп’ютера БЬХ, а саме комп’ютера ЭЪХУ. До складу процесора, структура якого приведена на рис. 4.18, входять пристрій векторного читання запису, регістрові файли з векторними та скалярними регістрами, а також операційний пристрій з набором конвеєрних операційних пристроїв додавання, множення та ділення з рухомою комою та виконання арифметичних і логічних операцій над цілими числами.

Таблиця

4.4

Команда

Операнди

Операція

Коментар

ADDV

VI,

V2.V3

V1=V2+V3

VECTOR+VECTOR

ADDSV

VI,

F0,V2

V1=F0+V2

SCALAR+VECTOR

MULTV

VI,

V2,V3

Vl=V2xV3

VECTORxVECTOR

MULSV

VI,

F0,V2

V1=F0XV2

SCALAR

x VECTOR

LV

VI,R1

V1=M[R]

..Rl+63]

LOAD,

STRIDES

LVWS

V1,R1,R2

V1=[R1.,R1+63*R2]

LOAD,

STRIDE=R2

LVI

VI,

R1.V2

V1=[R1+V2i,i=0..63

indirect

(“gather”)

CeqV

VM,V1,V2

VMASKi=(Vl

I=V2I)

comp.

Set mask

MOV

VLR,R1

Vec.

Len. Reg = R1

set

vector length

MOV

VM.Rl

Vec.

Mask=Rl

set

vector mask

Приведений процесор є процесором комп’ютера з простою системою команд. До цього типу належать усі векторні суперкомп’ютери: Cray, Convex, Fujitsu, Hitachi, NEC.

Хоча потрібно зауважити, що існують і векторні комп’ютери з архітектурою «пам’ять- пам’ять», коли всі векторні операції є операціями типу пам’ять-пам’ять наприклад, CDC-6600 Подібно до приведеного на рис. 4.18, процесори векторних комп’ютерів містять наступні основні компоненти

Векторні регістри; це регістрий файл фіксованої ємності що вміщує вектор даних. Цей файл має як мінімум 2 порти на читання і один порт на запис та зазвичай включає 8-32 векторних регістри, кожний з яких є 64-128-розрядним

Конвеєрні операційні пристрої. Зазвичай застосовують 4-8 операційних пристроїв, а саме: додавання, множення і ділення з фіксованою та рухомою комою, зсуву тощо

Векторний вузол читання-запису, також конвеєрний, який опрацьовує вектори даних. Водночас застосовують декілька таких вузлів

Скалярні регістри, які містять один скаляр з рухомою комою або адресу

Багатошинні магістралі або комутаційні мережі, які з’єднують між собою всі зазначені компоненти, аби прискорити роботу процесора в цілому

Перші векторні комп’ютери STAR-100 фірми CDC та ASC фірми ТІ були створені в 1972 році. Це були векторні комп’ютери з архітектурою типу пам’ять-пам’ять

Значний внесок в теорію побудови векторних комп’ютерів зробив видатний американський конструктор векторних суперкомп’ютерів Сеймур Крей. На рис. 4.19 зображено його перший векторний суперкомп’ютер Cray-1 та векторні суперкомп’ютери Cray-2 і Cray-YMP.

Рис. 4.19. Векторні

суперкомп’ютери Cray-1, Cray-2 і Cray-YMP

Комп’ютер CRAY-1 був створений в 1976 році і мав архітектуру типу «регістр-ре- гістр», тому він був найшвидшим серед векторних та скалярних комп’ютерів свого часу. В 1981 році на ринку з’явився значно потужніший векторний комп’ютер CYBER-205 фірми CDC з тією ж базовою архітектурою, що і STAR-100, але більшою кількістю векторних функціональних блоків. Це були векторні комп’ютери з архітектурою типу “пам’ять- пам’ять”. В 1983 році фірма Cray Research поставила на ринок векторний суперкомп’ютер CRAY Х-МР, а через кілька років - CRAY-2, який мав вищу тактову частоту та іще більший рівень конвеєризації. В 1988 році фірма Cray Research створила значно швидший, ніж Х-МР суперкомп’ютер CRAY Y-MP, котрий мав 8 конвеєрних процесорів, кожний з яких працював з тактом 6 не.

Одночасно потужні векторні суперкомп’ютери почали створюватись і в інших державах. Зокрема, в середині 80-х років в Японії були створені суперкомп’ютери Fujitsu

VP100 і VP200, за ними Hitachi S810 і NEC SX/2, які за технічними характеристиками не поступалися комп’ютерам фірми Cray Research

Протягом наступних 20 років векторні комп’ютери мали швидкий розвиток і з екзотичних перетворились в широковживаний клас потужних комп’ютерів.