- •Двнз «Чернівецький індустріальний коледж» архітектура комп’ютерів

- •Чернівці,

- •1.Історія розвитку обчислювальної техніки

- •2. Поняття про архітектуру еом. Принцип функціонування еом

- •38. Процесор векторного комп'ютера.

- •47. Функції арифметико-логічного пристрою. Способи обробки даних в арифметико-логічному пристрої

- •63. Частково-асоціативне відображення

- •82. Універсальна послідовна шина usb

- •1.Історія розвитку обчислювальної техніки

- •Покоління процесорів x86

- •Поняття архітектури і структурної організації комп’ютера

- •2. Поняття про архітектуру еом. Принцип функціонування еом Структура й принципи функціонування еом

- •3. Склад і призначення основних блоків

- •4. Архітектурні принципи Джона фон Неймана. Ненейманівські архітектури комп'ютерів

- •5. Апаратні і програмні засоби. Класифікація еом

- •Стандартні додатки Windows

- •Службові програми

- •Методи класифікації комп'ютерів.

- •Класифікація за призначенням

- •Великі еом (Main Frame)

- •МікроЕом

- •Персональні комп'ютери

- •Класифікація по рівню спеціалізації

- •Класифікація за розміром

- •Класифікація за сумісністю

- •6. Основні характеристики еом. Пк, особливості, класифікація, основні характеристики Основні характеристики пк

- •7. Персональні комп'ютери

- •8. Робочі станції. Багатотермінальні системи. Сервери

- •9. Кластерні комп'ютерні системи.

- •10. Суперкомп'ютери. Мікроконтролери. Спеціалізовані комп'ютери

- •11. Позиційні системи числення. Двійкові, вісімкові та шістнадцяткові числа

- •Двійкові, вісімкові та шістнадцяткові числа

- •12. Переведення чисел із системи числення з основою k у десяткову систему

- •13. Переведення чисел із десяткової системи у систему числення з основою k.

- •14. Прямий код. Обернений код. Доповняльний код. Способи представлення чисел

- •15. Числа з фіксованою комою. Числа із рухомою комою

- •16. Арифметичні операції. Ділення двійкових чисел

- •17. Арифметичні операції над двійковими числами у форматі з рухомою комою

- •18. Стандарт іеее-754. Розширений двійково-кодований десятковий код обміну ebcdic

- •19. Кодування алфавітно-цифрової інформації. Двійково-кодовані десяткові числа.

- •20. Американський стандартний код інформаційного обміну ascii. Стандарт кодування символів Unicode.

- •21. Кодування та виконання команд в комп'ютері

- •22. Виконання команд на рівні регістрів процессора.

- •23. Конвеєрне виконання команд

- •24. Класифікація архітектури комп'ютера за типом адресованої пам'яті.

- •25. Безпосередня адресація. Пряма адресація. Непряма адресація.

- •26. Відносна адресація. Базова адресація. Індексна адресація.

- •27. Сторінкова адресація. Неявна адресація. Стекова адресація. Використання стекової адресації.

- •28. Одношинна структура процесора.

- •29. Основні операції процесора. Вибірка слова з пам'яті. Запам'ятовування слова в пам'яті. Обмін даними між регістрами.

- •30. Багатошинна структура процесора.

- •31. Приклади виконання операцій в процесорі. Виконання операції додавання двох чисел.

- •32. Вимоги до процесора комп'ютера з простою системою команд. Базові принципи побудови процесора комп'ютера з простою системою команд.

- •33. Взаємодія процесора з пам'яттю в комп'ютері з простою системою команд.

- •34. Виконання команд в процесорі комп'ютера з простою системою команд. Фаза вибирання команди. Фаза декодування команди.

- •35. Конвеєрний процессор.

- •36. Мікродії ярусів конвеєрного процесора.

- •37. Суперскалярні процесори.

- •38. Процесор векторного комп'ютера.

- •39. Класифікація архітектури комп'ютера за рівнем суміщення опрацювання команд та даних.

- •40. Логічні операції.

- •1. Формальна логіка

- •2. Математична логіка

- •3. Програмування

- •41. Операція заперечення. Логічна 1. Логічне або. Виключне або.

- •42. Операції зсуву.

- •43. Операції відношення.

- •44. Арифметичні операції.

- •45. Операції обчислення елементарних функцій.

- •46. Операції перетворення даних.

- •47. Функції арифметико-логічного пристрою. Способи обробки даних в арифметико-логічному пристрої.

- •48. Елементарні операції арифметико-логічного пристрою.

- •49. Складні операції арифметико-логічного пристрою.

- •50. Структура арифметико-логічного пристрою.

- •51. Функції та методи побудови пристрою керування.

- •52. Пристрій керування з жорсткою логікою.

- •53. Пристрій керування на основі таблиць станів.

- •54. Пристрій мікропрограмного керування.

- •55. Порівняння пристроїв керування з жорсткою логікою та пристроїв мікропрограмного керування.

- •56 Ієрархічна організація пам'яті комп'ютера

- •57. Принцип ієрархічної організації пам'яті. Характеристики ефективності ієрархічної організації пам'яті

- •58. Кеш пам'ять в складі комп'ютера. Порядок взаємодії процесора і основної пам'яті через кеш пам'ять

- •59. Забезпечення ідентичності вмісту блоків кеш пам'яті і основної пам'яті

- •60. Функція відображення. Типи функцій відображення

- •61. Повністю асоціативне відображення

- •62. Пряме відображення

- •63. Частково-асоціативне відображення

- •64. Порядок заміщення блоків в кеш пам'яті з асоціативним відображенням

- •65. Підвищення ефективності кеш пам'яті

- •66. Статичний та динамічний розподіл пам'яті. Розподіл основної пам'яті за допомогою базових адрес

- •67. Віртуальна пам'ять. Сторінкова організація пам'яті

- •68. Основні правила сторінкової організації пам'яті. Реалізація сторінкової організації пам'яті

- •69. Апаратна реалізація сторінкової таблиці

- •70. Сегментна організація віртуальної пам'яті

- •71. Захист пам'яті від несанкціонованих звернень

- •72. Захист пам'яті за значеннями ключів

- •73. Кільцева схема захисту пам'яті

- •74. Архітектура системної плати

- •75. Синхронізація

- •76. Система шин

- •77. Особливості роботи шини

- •78. Характеристики шин пк

- •79. Шина pcmcia, vbl

- •80. Шина pci

- •82. Універсальна послідовна шина usb

- •83.Типи передач і формати інформації що передається

- •84. Шина scsi

- •85. Адресація пристроїв і передача даних

- •86. Система команд

- •87. Конфігурування пристроїв scsi

- •88. Ігровий адаптер Game-порт

- •89. Відеоадаптери

- •90. Послідовний інтерфейс. Сом-порт

- •91. Програмна модель сом-порта

- •92. Програмування послідовного зв’язку

- •93. Ініціалізація послідовного порта. Передача і прийом даних

- •95. Паралельний інтерфейс lpt-порт. Стандартний режим spp

- •96. Режим epp

- •97. Режим ecp

- •98. Узгодження режимів

- •99. Приклад програмування

- •100. Клавіатура

- •101. Під'єднання зовнішніх пристроїв до комп'ютера

- •102. Розпізнавання пристроїв введення-виведення

- •103. Методи керування введенням-виведенням

- •104. Програмно-кероване введення-виведення.

- •105. Система переривання програм та організація введення-виведення за перериваннями

- •106. Прямий доступ до пам'яті. Введення-виведення під керуванням периферійних процесорів

- •107. Мультиплексний та селекторний канали введення-виведення

- •108. Використання принципів паралельної обробки інформації в архітектурі комп'ютера

- •109. Вибір кількості процесорів в багатопроцесорній системі

- •110. Багатопотокова обробка інформації. Окр

- •111. Класифікація Шора. Класифікація Фліна

- •112. Типи архітектур систем окмд. Типи архітектур систем мкмд

- •113.Організація комп'ютерних систем із спільною пам'яттю

- •114. Організація комп'ютерних систем із розподіленою пам'яттю

- •115. Комунікаційні мережі багатопроцесорних систем

34. Виконання команд в процесорі комп'ютера з простою системою команд. Фаза вибирання команди. Фаза декодування команди.

Фаза вибирання команди

Виконання команд в процесорі комп’ютера з простою системою команд розглянемо на прикладі процесора комп’ютера ПЬХ, структура якого була розглянута в п. 4.2.2.

В рамках фази вибирання команди ІР виконуються наступні мікродії (мікрооперації):

Виконання першої мікродії спричинює завантаження до 32-бітовото регістра поточної команди IR вмісту чотирьох послідовно розташованих комірок пам’яті команд, починаючи від адреси (PC) + 0 і завершуючи адресою (PC) + 3. Як і завжди, за допомогою (PC) позначено вміст програмного лічильника PC.

Друга мікродія (NPC = PC + 4) вираховує “планову” адресу наступної за чергою команди з послідовного потоку. Тобто тут визначається і тимчасово зберігається у регістрі NPC вміст програмного лічильника. “Логічне” вибирання вмісту чотирьох послідовно розташованих однобайтових комірок замість однієї чотирибайтової підкреслює те, що навіть на рівні мікродій адресування комірок пам’яті вказують логічно. За умови коли адреса байта кратна чотирьом, тобто дотримано вирівнювання границь адрес команд, із пам яті, одразу (за одне звернення) вибирають чотири байти і навіть цілі пакети по чотири байти. Отриманий з пам’яті даних код тлумачать як 32-розрядне слово, а з пам’яті команд - як одну команду

Зауважимо, що обидві наведені мікродії теоретично є сумісними в часі. Саме тому вони можуть і мають виконуватися паралельно. Ці мікродії утворюють єдину мікроко- манду

Важливою властивістю фази IF є те, що вона не приймає до уваги існування відомого «парадокса пам’яті». Дійсно, у фазі IF за часовими витратами мікродія вибирання з повільних комірок пам’яті команд є тотожною мікродії, що працює з внутрішніми, а саме тому надшвидкими регістрами процесора.

Фаза декодування команди

В рамках фази декодування команди ID виконуються наступні мікродії (мікрооперації):

У наведеному мікрокоді, що складений з трьох сумісних у часі, тобто придатних до одночасного (паралельного) виконання мікродій, вжито наступні позначення:

А, В, Imm - внутрішні службові 32-розрядні регістри для проміжного збереження кодів; всі три регістри є “прозорими” для програміста в тому сенсі, що вони аж ніяк не відбиті в машинних командах.

Regs [address] - номер регістра регістрового файла процесора;

R ^ - поле регістра команд, яке містить групу послідовно розташованих бітів - від біта з номером X до біта з номером Y включно; звернемо увагу на нумерацію бітів у слові процесора - лівий біт має 0-й номер, а правий - 31-й номер.

IR6 ш - поле регістра команд, що містить бінарний номер регістра - джерела даного (див. формат команд); довжина поля рівна 5 бітам, що дозволяє позначати та адресувати 32 регістри - від RQ до R3,

IR - також п’ятибітове поле номера ще одного регістра - джерела даного з множини R0...R31

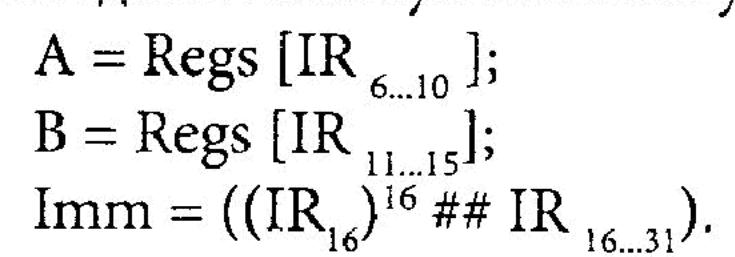

Вже зауважувалося, що поле безпосереднього операнда (Immediate або Imm) у форматі команди має довжину лише 16 бітів. В той же час, розрядність інформаційного тракту в усіх трьох службових регістрів рівна 32 біти. До того, як записати 16-бітовий код IR]6 31 безпосереднього операнда з регістра команд до службового регістра Imm, цей код треба розширити з врахуванням знака (тобто розряду IR16) до 32-бітового значення а наступним стандартним алгоритмом знакового розширення:

![]()

Тут символом ## позначено операцію зчеплення (конкатенацію).

Важливо, що в рамках фази ID виконується декодування (розпізнавання) команди та вибирання усіх можливих варіантів операндів поточної команди, незалежно від її типу, з метою збільшення швидкодії. З іншого боку, можливість одночасного вибирання усіх варіантів операндів потенційно обумовлено відповідною структурою форматів команд, де фіксовано розташування полів-покажчиків на джерела даних та приймачі операндів і результатів. Іншими словами, формати команд процесора втілюють техніку кодування форматів команд, що відома під назвою “fixed-field coding”.