- •Двнз «Чернівецький індустріальний коледж» архітектура комп’ютерів

- •Чернівці,

- •1.Історія розвитку обчислювальної техніки

- •2. Поняття про архітектуру еом. Принцип функціонування еом

- •38. Процесор векторного комп'ютера.

- •47. Функції арифметико-логічного пристрою. Способи обробки даних в арифметико-логічному пристрої

- •63. Частково-асоціативне відображення

- •82. Універсальна послідовна шина usb

- •1.Історія розвитку обчислювальної техніки

- •Покоління процесорів x86

- •Поняття архітектури і структурної організації комп’ютера

- •2. Поняття про архітектуру еом. Принцип функціонування еом Структура й принципи функціонування еом

- •3. Склад і призначення основних блоків

- •4. Архітектурні принципи Джона фон Неймана. Ненейманівські архітектури комп'ютерів

- •5. Апаратні і програмні засоби. Класифікація еом

- •Стандартні додатки Windows

- •Службові програми

- •Методи класифікації комп'ютерів.

- •Класифікація за призначенням

- •Великі еом (Main Frame)

- •МікроЕом

- •Персональні комп'ютери

- •Класифікація по рівню спеціалізації

- •Класифікація за розміром

- •Класифікація за сумісністю

- •6. Основні характеристики еом. Пк, особливості, класифікація, основні характеристики Основні характеристики пк

- •7. Персональні комп'ютери

- •8. Робочі станції. Багатотермінальні системи. Сервери

- •9. Кластерні комп'ютерні системи.

- •10. Суперкомп'ютери. Мікроконтролери. Спеціалізовані комп'ютери

- •11. Позиційні системи числення. Двійкові, вісімкові та шістнадцяткові числа

- •Двійкові, вісімкові та шістнадцяткові числа

- •12. Переведення чисел із системи числення з основою k у десяткову систему

- •13. Переведення чисел із десяткової системи у систему числення з основою k.

- •14. Прямий код. Обернений код. Доповняльний код. Способи представлення чисел

- •15. Числа з фіксованою комою. Числа із рухомою комою

- •16. Арифметичні операції. Ділення двійкових чисел

- •17. Арифметичні операції над двійковими числами у форматі з рухомою комою

- •18. Стандарт іеее-754. Розширений двійково-кодований десятковий код обміну ebcdic

- •19. Кодування алфавітно-цифрової інформації. Двійково-кодовані десяткові числа.

- •20. Американський стандартний код інформаційного обміну ascii. Стандарт кодування символів Unicode.

- •21. Кодування та виконання команд в комп'ютері

- •22. Виконання команд на рівні регістрів процессора.

- •23. Конвеєрне виконання команд

- •24. Класифікація архітектури комп'ютера за типом адресованої пам'яті.

- •25. Безпосередня адресація. Пряма адресація. Непряма адресація.

- •26. Відносна адресація. Базова адресація. Індексна адресація.

- •27. Сторінкова адресація. Неявна адресація. Стекова адресація. Використання стекової адресації.

- •28. Одношинна структура процесора.

- •29. Основні операції процесора. Вибірка слова з пам'яті. Запам'ятовування слова в пам'яті. Обмін даними між регістрами.

- •30. Багатошинна структура процесора.

- •31. Приклади виконання операцій в процесорі. Виконання операції додавання двох чисел.

- •32. Вимоги до процесора комп'ютера з простою системою команд. Базові принципи побудови процесора комп'ютера з простою системою команд.

- •33. Взаємодія процесора з пам'яттю в комп'ютері з простою системою команд.

- •34. Виконання команд в процесорі комп'ютера з простою системою команд. Фаза вибирання команди. Фаза декодування команди.

- •35. Конвеєрний процессор.

- •36. Мікродії ярусів конвеєрного процесора.

- •37. Суперскалярні процесори.

- •38. Процесор векторного комп'ютера.

- •39. Класифікація архітектури комп'ютера за рівнем суміщення опрацювання команд та даних.

- •40. Логічні операції.

- •1. Формальна логіка

- •2. Математична логіка

- •3. Програмування

- •41. Операція заперечення. Логічна 1. Логічне або. Виключне або.

- •42. Операції зсуву.

- •43. Операції відношення.

- •44. Арифметичні операції.

- •45. Операції обчислення елементарних функцій.

- •46. Операції перетворення даних.

- •47. Функції арифметико-логічного пристрою. Способи обробки даних в арифметико-логічному пристрої.

- •48. Елементарні операції арифметико-логічного пристрою.

- •49. Складні операції арифметико-логічного пристрою.

- •50. Структура арифметико-логічного пристрою.

- •51. Функції та методи побудови пристрою керування.

- •52. Пристрій керування з жорсткою логікою.

- •53. Пристрій керування на основі таблиць станів.

- •54. Пристрій мікропрограмного керування.

- •55. Порівняння пристроїв керування з жорсткою логікою та пристроїв мікропрограмного керування.

- •56 Ієрархічна організація пам'яті комп'ютера

- •57. Принцип ієрархічної організації пам'яті. Характеристики ефективності ієрархічної організації пам'яті

- •58. Кеш пам'ять в складі комп'ютера. Порядок взаємодії процесора і основної пам'яті через кеш пам'ять

- •59. Забезпечення ідентичності вмісту блоків кеш пам'яті і основної пам'яті

- •60. Функція відображення. Типи функцій відображення

- •61. Повністю асоціативне відображення

- •62. Пряме відображення

- •63. Частково-асоціативне відображення

- •64. Порядок заміщення блоків в кеш пам'яті з асоціативним відображенням

- •65. Підвищення ефективності кеш пам'яті

- •66. Статичний та динамічний розподіл пам'яті. Розподіл основної пам'яті за допомогою базових адрес

- •67. Віртуальна пам'ять. Сторінкова організація пам'яті

- •68. Основні правила сторінкової організації пам'яті. Реалізація сторінкової організації пам'яті

- •69. Апаратна реалізація сторінкової таблиці

- •70. Сегментна організація віртуальної пам'яті

- •71. Захист пам'яті від несанкціонованих звернень

- •72. Захист пам'яті за значеннями ключів

- •73. Кільцева схема захисту пам'яті

- •74. Архітектура системної плати

- •75. Синхронізація

- •76. Система шин

- •77. Особливості роботи шини

- •78. Характеристики шин пк

- •79. Шина pcmcia, vbl

- •80. Шина pci

- •82. Універсальна послідовна шина usb

- •83.Типи передач і формати інформації що передається

- •84. Шина scsi

- •85. Адресація пристроїв і передача даних

- •86. Система команд

- •87. Конфігурування пристроїв scsi

- •88. Ігровий адаптер Game-порт

- •89. Відеоадаптери

- •90. Послідовний інтерфейс. Сом-порт

- •91. Програмна модель сом-порта

- •92. Програмування послідовного зв’язку

- •93. Ініціалізація послідовного порта. Передача і прийом даних

- •95. Паралельний інтерфейс lpt-порт. Стандартний режим spp

- •96. Режим epp

- •97. Режим ecp

- •98. Узгодження режимів

- •99. Приклад програмування

- •100. Клавіатура

- •101. Під'єднання зовнішніх пристроїв до комп'ютера

- •102. Розпізнавання пристроїв введення-виведення

- •103. Методи керування введенням-виведенням

- •104. Програмно-кероване введення-виведення.

- •105. Система переривання програм та організація введення-виведення за перериваннями

- •106. Прямий доступ до пам'яті. Введення-виведення під керуванням периферійних процесорів

- •107. Мультиплексний та селекторний канали введення-виведення

- •108. Використання принципів паралельної обробки інформації в архітектурі комп'ютера

- •109. Вибір кількості процесорів в багатопроцесорній системі

- •110. Багатопотокова обробка інформації. Окр

- •111. Класифікація Шора. Класифікація Фліна

- •112. Типи архітектур систем окмд. Типи архітектур систем мкмд

- •113.Організація комп'ютерних систем із спільною пам'яттю

- •114. Організація комп'ютерних систем із розподіленою пам'яттю

- •115. Комунікаційні мережі багатопроцесорних систем

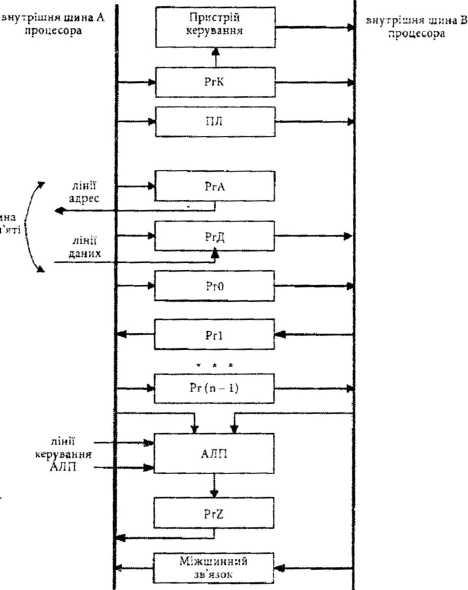

30. Багатошинна структура процесора.

Наведена на рис. 4.1 одношинна структура процесора є достатньо простою. Тому вона широко використовується при побудові процесорів реальних комп’ютерів. Зокрема, за такою схемою побудовано більшість мікроконтролерів, від яких не вимагається висока швидкодія. Якщо ж така вимога існує, то застосовується багатошинна організація процесора, в якій завдяки наявності багатьох шин забезпечується можливість паралельного обміну інформації між функціональними вузлами процесора і, тим самим, суттєво підвищується швидкість опрацювання інформації. Як приклад на рис. 4.3 показано можливий варіант двошинної структури процесора.

Рис. 4.3. Двошинна

структура процесора

.

Розглянемо виконання на цій структурі процесора операції РгЗ : = РгО + Ргі:

PrOout, Prlout, Add, PrZin (подання на шину А числа з регістра Ргі та на шину В числа з регістра РгО, виконання в АЛП операції додавання та запис результату до регістра PrZ).

PrZout, РгЗіп (запис числа з регістра PrZ до регістра РгЗ через міст М зв’язку між шинами).

Як видно, для виконання операції додавання тут потрібно лише два такти, тоді як в одношинній структурі процесора було потрібно три такти.

Зрозуміло, що із збільшенням кількості шин швидкість обміну зростає. Так, в тришин- ній структурі процесора операція додавання двох чисел буде виконана за один такт.

Збільшення кількості шин ускладнює структуру процесора та збільшує кількість необхідного обладнання на його побудову. Адже кожна додаткова шина - це велика кількість додаткових провідників, які займають багато місця на кристалі. Однак потреба підвищення продуктивності змушує розробників застосовувати саме багатошинну структуру процесора. Більшість процесорів сучасних високопродуктивних комп’ютерів є багатошинними.

31. Приклади виконання операцій в процесорі. Виконання операції додавання двох чисел.

Об’єднаємо послідовність елементарних операцій, необхідних для виконання однієї команди. Розглянемо команду “Додати вміст деякої комірки основної пам’яті до вмісту регістра Ргі із записом результату до цього ж регістра, причому адреса комірки основної пам’яті задана в адресному полі команди”.

Виконання цієї команди вимагає наступних дій:

Вибірки команди з основної пам’яті та її запис до регістра команди РгК.

Вибірки першого операнда з основної пам’яті та його запис до одного з регістрів надоперативної пам’яті процесора.

Виконання додавання.

Засилання результату в регістр Ргі.

Програма виконання цих дій на одношинній структурі процесора (рис. 4.1) буде мати наступний вигляд:

Фаза вибірки :

ПЛout, РгАіn, зчитування, очищення регістра PrY, включення переносу та операції додавання в АЛП, PrZin (адреса команди з програмного лічильника ПЛ подана на шину та записалась до регістра адреси РгА, на вхід керування режимом роботи основної пам’яті подано сигнал Read, на вхід скиду регістра PrY подано сигнал Reset, в АЛП виконалась операція додавання 1 до вмісту програмного лічильника ПЛ та її результат записався в регістр PrZ).

PrZout, ПЛіn, чекання підтвердження сигналу зчитування (результат додавання з регістра PrZ записався в програмний лічильник ПЛ, команда з основної пам’яті записалась в регістр РгД).

РгДоut:, РгКіn (команда з регістра даних РгД записалась до регістра команди РгК).

Фаза виконання:

(Поле адреси PrK)out, PrAin, зчитування (адреса з поля адреси регістра команди РгК переписується до регістра адреси РгА, на вхід керування режимом роботи основної пам’яті подано сигнал Read).

Prlout, РгУіп, чекання підтвердження сигналу зчитування (число з регістра Ргі записалось до регістра PrY, а число з основної пам’яті записалось до регістра РгД).

РгДоШ, Add, PrZin (число з регістра РгД поступило на шину та додалося в АЛП до числа з регістра PrY, а результат записався в регістр PrZ).

PrZout, Prlin, End (число з регістра PrZ переписалось в регістр Ргі, кінець виконання операції).

Тут Add - код операції додавання, який поступає на вхід АЛП та вказує йому тип виконуваної операції.