- •Двнз «Чернівецький індустріальний коледж» архітектура комп’ютерів

- •Чернівці,

- •1.Історія розвитку обчислювальної техніки

- •2. Поняття про архітектуру еом. Принцип функціонування еом

- •38. Процесор векторного комп'ютера.

- •47. Функції арифметико-логічного пристрою. Способи обробки даних в арифметико-логічному пристрої

- •63. Частково-асоціативне відображення

- •82. Універсальна послідовна шина usb

- •1.Історія розвитку обчислювальної техніки

- •Покоління процесорів x86

- •Поняття архітектури і структурної організації комп’ютера

- •2. Поняття про архітектуру еом. Принцип функціонування еом Структура й принципи функціонування еом

- •3. Склад і призначення основних блоків

- •4. Архітектурні принципи Джона фон Неймана. Ненейманівські архітектури комп'ютерів

- •5. Апаратні і програмні засоби. Класифікація еом

- •Стандартні додатки Windows

- •Службові програми

- •Методи класифікації комп'ютерів.

- •Класифікація за призначенням

- •Великі еом (Main Frame)

- •МікроЕом

- •Персональні комп'ютери

- •Класифікація по рівню спеціалізації

- •Класифікація за розміром

- •Класифікація за сумісністю

- •6. Основні характеристики еом. Пк, особливості, класифікація, основні характеристики Основні характеристики пк

- •7. Персональні комп'ютери

- •8. Робочі станції. Багатотермінальні системи. Сервери

- •9. Кластерні комп'ютерні системи.

- •10. Суперкомп'ютери. Мікроконтролери. Спеціалізовані комп'ютери

- •11. Позиційні системи числення. Двійкові, вісімкові та шістнадцяткові числа

- •Двійкові, вісімкові та шістнадцяткові числа

- •12. Переведення чисел із системи числення з основою k у десяткову систему

- •13. Переведення чисел із десяткової системи у систему числення з основою k.

- •14. Прямий код. Обернений код. Доповняльний код. Способи представлення чисел

- •15. Числа з фіксованою комою. Числа із рухомою комою

- •16. Арифметичні операції. Ділення двійкових чисел

- •17. Арифметичні операції над двійковими числами у форматі з рухомою комою

- •18. Стандарт іеее-754. Розширений двійково-кодований десятковий код обміну ebcdic

- •19. Кодування алфавітно-цифрової інформації. Двійково-кодовані десяткові числа.

- •20. Американський стандартний код інформаційного обміну ascii. Стандарт кодування символів Unicode.

- •21. Кодування та виконання команд в комп'ютері

- •22. Виконання команд на рівні регістрів процессора.

- •23. Конвеєрне виконання команд

- •24. Класифікація архітектури комп'ютера за типом адресованої пам'яті.

- •25. Безпосередня адресація. Пряма адресація. Непряма адресація.

- •26. Відносна адресація. Базова адресація. Індексна адресація.

- •27. Сторінкова адресація. Неявна адресація. Стекова адресація. Використання стекової адресації.

- •28. Одношинна структура процесора.

- •29. Основні операції процесора. Вибірка слова з пам'яті. Запам'ятовування слова в пам'яті. Обмін даними між регістрами.

- •30. Багатошинна структура процесора.

- •31. Приклади виконання операцій в процесорі. Виконання операції додавання двох чисел.

- •32. Вимоги до процесора комп'ютера з простою системою команд. Базові принципи побудови процесора комп'ютера з простою системою команд.

- •33. Взаємодія процесора з пам'яттю в комп'ютері з простою системою команд.

- •34. Виконання команд в процесорі комп'ютера з простою системою команд. Фаза вибирання команди. Фаза декодування команди.

- •35. Конвеєрний процессор.

- •36. Мікродії ярусів конвеєрного процесора.

- •37. Суперскалярні процесори.

- •38. Процесор векторного комп'ютера.

- •39. Класифікація архітектури комп'ютера за рівнем суміщення опрацювання команд та даних.

- •40. Логічні операції.

- •1. Формальна логіка

- •2. Математична логіка

- •3. Програмування

- •41. Операція заперечення. Логічна 1. Логічне або. Виключне або.

- •42. Операції зсуву.

- •43. Операції відношення.

- •44. Арифметичні операції.

- •45. Операції обчислення елементарних функцій.

- •46. Операції перетворення даних.

- •47. Функції арифметико-логічного пристрою. Способи обробки даних в арифметико-логічному пристрої.

- •48. Елементарні операції арифметико-логічного пристрою.

- •49. Складні операції арифметико-логічного пристрою.

- •50. Структура арифметико-логічного пристрою.

- •51. Функції та методи побудови пристрою керування.

- •52. Пристрій керування з жорсткою логікою.

- •53. Пристрій керування на основі таблиць станів.

- •54. Пристрій мікропрограмного керування.

- •55. Порівняння пристроїв керування з жорсткою логікою та пристроїв мікропрограмного керування.

- •56 Ієрархічна організація пам'яті комп'ютера

- •57. Принцип ієрархічної організації пам'яті. Характеристики ефективності ієрархічної організації пам'яті

- •58. Кеш пам'ять в складі комп'ютера. Порядок взаємодії процесора і основної пам'яті через кеш пам'ять

- •59. Забезпечення ідентичності вмісту блоків кеш пам'яті і основної пам'яті

- •60. Функція відображення. Типи функцій відображення

- •61. Повністю асоціативне відображення

- •62. Пряме відображення

- •63. Частково-асоціативне відображення

- •64. Порядок заміщення блоків в кеш пам'яті з асоціативним відображенням

- •65. Підвищення ефективності кеш пам'яті

- •66. Статичний та динамічний розподіл пам'яті. Розподіл основної пам'яті за допомогою базових адрес

- •67. Віртуальна пам'ять. Сторінкова організація пам'яті

- •68. Основні правила сторінкової організації пам'яті. Реалізація сторінкової організації пам'яті

- •69. Апаратна реалізація сторінкової таблиці

- •70. Сегментна організація віртуальної пам'яті

- •71. Захист пам'яті від несанкціонованих звернень

- •72. Захист пам'яті за значеннями ключів

- •73. Кільцева схема захисту пам'яті

- •74. Архітектура системної плати

- •75. Синхронізація

- •76. Система шин

- •77. Особливості роботи шини

- •78. Характеристики шин пк

- •79. Шина pcmcia, vbl

- •80. Шина pci

- •82. Універсальна послідовна шина usb

- •83.Типи передач і формати інформації що передається

- •84. Шина scsi

- •85. Адресація пристроїв і передача даних

- •86. Система команд

- •87. Конфігурування пристроїв scsi

- •88. Ігровий адаптер Game-порт

- •89. Відеоадаптери

- •90. Послідовний інтерфейс. Сом-порт

- •91. Програмна модель сом-порта

- •92. Програмування послідовного зв’язку

- •93. Ініціалізація послідовного порта. Передача і прийом даних

- •95. Паралельний інтерфейс lpt-порт. Стандартний режим spp

- •96. Режим epp

- •97. Режим ecp

- •98. Узгодження режимів

- •99. Приклад програмування

- •100. Клавіатура

- •101. Під'єднання зовнішніх пристроїв до комп'ютера

- •102. Розпізнавання пристроїв введення-виведення

- •103. Методи керування введенням-виведенням

- •104. Програмно-кероване введення-виведення.

- •105. Система переривання програм та організація введення-виведення за перериваннями

- •106. Прямий доступ до пам'яті. Введення-виведення під керуванням периферійних процесорів

- •107. Мультиплексний та селекторний канали введення-виведення

- •108. Використання принципів паралельної обробки інформації в архітектурі комп'ютера

- •109. Вибір кількості процесорів в багатопроцесорній системі

- •110. Багатопотокова обробка інформації. Окр

- •111. Класифікація Шора. Класифікація Фліна

- •112. Типи архітектур систем окмд. Типи архітектур систем мкмд

- •113.Організація комп'ютерних систем із спільною пам'яттю

- •114. Організація комп'ютерних систем із розподіленою пам'яттю

- •115. Комунікаційні мережі багатопроцесорних систем

28. Одношинна структура процесора.

Почнемо розгляд процесора з аналізу його структури та організації роботи. Однією з найпростіших структур процесора є одношинна структура. Одношинну структуру процесора і його зв’язки з іншими пристроями комп’ютера показано на рис. 4.1. Як бачимо, до складу процесора входять пристрій керування, арифметико-логічний пристрій АЛП з вхідним РгУ та вихідним Рг2 регістрами, і регістрова пам’ять, до складу якої входять регістр команд РгК, регістр даних РгД, регістр адреси РгА, програмний лічильник ПЛ, та регістре- вий файл - стек програмно доступних регістрів РгО, Ргі... Рг(п-І). Обмін інформацією між названими пристроями здійснюється через спільну внутрішню шину процесора. Зв’язок процесора з основною пам’яттю проводиться через регістри адрес РгА та даних РгД.

Рис. 4.1. Однотипна

структура процесора

Регістри загального призначення Рг0-Рг(п регістрового файла є програмно доступними. Вони можуть використовуватися програмістом в якості адресних регістрів, індексних регістрів при виконанні операцій модифікації адрес або в якості регістрів для зберігання проміжних результатів обчислень. Більшість комп’ютерів мають в складі процесора тригери для зберігання бітів стану процесора, або як їх ще називають, прапорців. Кожен прапорець має спеціальне призначення. Частина прапорців вказує на результати арифметичних і логічних операцій: додатній результат (Р), від’ємний результат (М), нульовий результат {Т), перенос (С), арифметичне переповнення (V) тощо.

Різні команди вказують процесору, коли встановити чи очистити ці тригери. Інша частина прапорців вказує режими захисту пам’яті. Існують також прапорці, які вказують пріоритети виконуваних програм. В деяких процесорах додаткові тригери слугують для зберігання кодів умов, формуючи регістр кодів умов. Взяті разом описані прапорці формують слово стану програми (ССП), а відповідні тригери - регістр ССП.

29. Основні операції процесора. Вибірка слова з пам'яті. Запам'ятовування слова в пам'яті. Обмін даними між регістрами.

Основні операції процесора

Можна виділити дві фази виконання команди в процесорі: фаза вибірки та фаза виконання. Фаза вибірки передбачає вибірку вмісту комірки основної пам’яті, в якій зберігається команда, за значенням програмного лічильника ПЛ і засилання команди в РгК (РгК := [[ПЛ]]), а також прирощення ПЛ на одиницю: [ПЛ] [ПЛ] + 1. Фаза виконання команди передбачає її дешифрування та виконання операцій, вказаних в коді операції команди. Для того, щоб побачити, як обидві фази виконуються в процесорі, розглянемо його основні операції, до виконання яких задіяні представлені на рис. 4.1 елементи.

Вибірка слова з пам’яті

Нехай адреса комірки основної пам’яті знаходиться в регістрі Ргі, а дані потрібно розмістити в регістрі Рг2.

Для вибірки із основної пам’яті необхідно виконати наступну послідовність операцій:

РгА := Ргі (запис до регістра адреси РгА вмісту регістра Ргі).

Зчитування (виконання операції зчитування команди з комірки основної пам’яті до регістра РгД шляхом подання сигналу Read на вхід керування режимом роботи основної пам’яті та сигналу запису до регістра РгД).

Чекання на сигнал підтвердження зчитування.

Рг2 := РгД (запис до регістра Рг2 даного з регістра РгД).

Пункт 3 виконується при асинхронному принципі обміну між процесором і основною пам’яттю, коли потрібно чекати на сигнал підтвердження зчитування. При синхронному принципі обміну чекати на сигнал підтвердження зчитування не потрібно, оскільки до подання сигналу запису в регістр РгД передбачається гарантована наявність даного на його вході.

Запам’ятовування слова в пам’яті

Нехай слово, яке запам’ятовується в основній пам’яті, знаходиться в регістрі Рг2, а адреса - в регістрі Ргі. Тоді послідовність операцій буде наступною:

РгА := Рг 1 (запис до регістра адреси РгА вмісту регістра Ргі).

РгД := Рг2 (запис до регістра даних РгД ВхМІсту регістра Рг2), запис (виконання операції запису слова з регістра РгД до комірки основної пам’яті шляхом подання сигналу Write на вхід керування режимом роботи основної пам’яті).

Чекання на сигнал підтвердження запису (при асинхронному принципі обміну між процесором і основною пам’яттю).

Обмін даними між регістрами

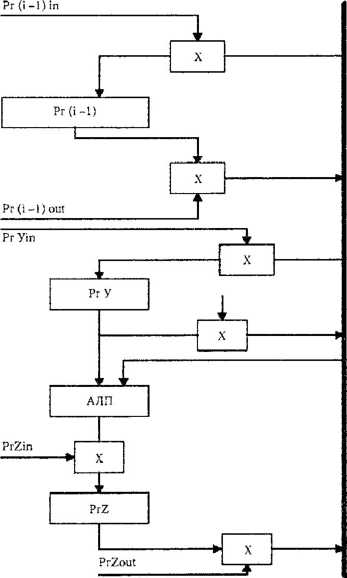

Символьне зображення вхідних і вихідних елементів регістрів процесора показане на рис. 4.2 у вигляді ключів, які пропускають або не пропускають інформацію з входу на вихід, залежно від значення сигналів керування на 'їх входах. Тут сигнал керування входом і-го регістра Ргі позначено як Ргі in, а сигнал керування виходом і-го регістра Ргі позначено як Ргі out. В конкретній схемі регістра це можуть бути, наприклад, вхід запису числа до регістра та його тристабільний вихід.

Рис. 4.2. Фрагмент

схеми процесора

з вхідними

та вихідними елементами регістрів

Подання 1 на вхід керування регістра Priout з’єднує вихід регістра Ргі з шиною, а подання 1 на вхід керування регістра Ргііп записує число з шини в регістр Ргі. Подаючи на регістри вказані сигнали, можна переписувати числа з одного регістра в інший наприклад, для перезапису числа із регістра РгЗ до регістра Рг5 необхідно подати наступні сигнали: Pr3out, Рг5іn.