- •Двнз «Чернівецький індустріальний коледж» архітектура комп’ютерів

- •Чернівці,

- •1.Історія розвитку обчислювальної техніки

- •2. Поняття про архітектуру еом. Принцип функціонування еом

- •38. Процесор векторного комп'ютера.

- •47. Функції арифметико-логічного пристрою. Способи обробки даних в арифметико-логічному пристрої

- •63. Частково-асоціативне відображення

- •82. Універсальна послідовна шина usb

- •1.Історія розвитку обчислювальної техніки

- •Покоління процесорів x86

- •Поняття архітектури і структурної організації комп’ютера

- •2. Поняття про архітектуру еом. Принцип функціонування еом Структура й принципи функціонування еом

- •3. Склад і призначення основних блоків

- •4. Архітектурні принципи Джона фон Неймана. Ненейманівські архітектури комп'ютерів

- •5. Апаратні і програмні засоби. Класифікація еом

- •Стандартні додатки Windows

- •Службові програми

- •Методи класифікації комп'ютерів.

- •Класифікація за призначенням

- •Великі еом (Main Frame)

- •МікроЕом

- •Персональні комп'ютери

- •Класифікація по рівню спеціалізації

- •Класифікація за розміром

- •Класифікація за сумісністю

- •6. Основні характеристики еом. Пк, особливості, класифікація, основні характеристики Основні характеристики пк

- •7. Персональні комп'ютери

- •8. Робочі станції. Багатотермінальні системи. Сервери

- •9. Кластерні комп'ютерні системи.

- •10. Суперкомп'ютери. Мікроконтролери. Спеціалізовані комп'ютери

- •11. Позиційні системи числення. Двійкові, вісімкові та шістнадцяткові числа

- •Двійкові, вісімкові та шістнадцяткові числа

- •12. Переведення чисел із системи числення з основою k у десяткову систему

- •13. Переведення чисел із десяткової системи у систему числення з основою k.

- •14. Прямий код. Обернений код. Доповняльний код. Способи представлення чисел

- •15. Числа з фіксованою комою. Числа із рухомою комою

- •16. Арифметичні операції. Ділення двійкових чисел

- •17. Арифметичні операції над двійковими числами у форматі з рухомою комою

- •18. Стандарт іеее-754. Розширений двійково-кодований десятковий код обміну ebcdic

- •19. Кодування алфавітно-цифрової інформації. Двійково-кодовані десяткові числа.

- •20. Американський стандартний код інформаційного обміну ascii. Стандарт кодування символів Unicode.

- •21. Кодування та виконання команд в комп'ютері

- •22. Виконання команд на рівні регістрів процессора.

- •23. Конвеєрне виконання команд

- •24. Класифікація архітектури комп'ютера за типом адресованої пам'яті.

- •25. Безпосередня адресація. Пряма адресація. Непряма адресація.

- •26. Відносна адресація. Базова адресація. Індексна адресація.

- •27. Сторінкова адресація. Неявна адресація. Стекова адресація. Використання стекової адресації.

- •28. Одношинна структура процесора.

- •29. Основні операції процесора. Вибірка слова з пам'яті. Запам'ятовування слова в пам'яті. Обмін даними між регістрами.

- •30. Багатошинна структура процесора.

- •31. Приклади виконання операцій в процесорі. Виконання операції додавання двох чисел.

- •32. Вимоги до процесора комп'ютера з простою системою команд. Базові принципи побудови процесора комп'ютера з простою системою команд.

- •33. Взаємодія процесора з пам'яттю в комп'ютері з простою системою команд.

- •34. Виконання команд в процесорі комп'ютера з простою системою команд. Фаза вибирання команди. Фаза декодування команди.

- •35. Конвеєрний процессор.

- •36. Мікродії ярусів конвеєрного процесора.

- •37. Суперскалярні процесори.

- •38. Процесор векторного комп'ютера.

- •39. Класифікація архітектури комп'ютера за рівнем суміщення опрацювання команд та даних.

- •40. Логічні операції.

- •1. Формальна логіка

- •2. Математична логіка

- •3. Програмування

- •41. Операція заперечення. Логічна 1. Логічне або. Виключне або.

- •42. Операції зсуву.

- •43. Операції відношення.

- •44. Арифметичні операції.

- •45. Операції обчислення елементарних функцій.

- •46. Операції перетворення даних.

- •47. Функції арифметико-логічного пристрою. Способи обробки даних в арифметико-логічному пристрої.

- •48. Елементарні операції арифметико-логічного пристрою.

- •49. Складні операції арифметико-логічного пристрою.

- •50. Структура арифметико-логічного пристрою.

- •51. Функції та методи побудови пристрою керування.

- •52. Пристрій керування з жорсткою логікою.

- •53. Пристрій керування на основі таблиць станів.

- •54. Пристрій мікропрограмного керування.

- •55. Порівняння пристроїв керування з жорсткою логікою та пристроїв мікропрограмного керування.

- •56 Ієрархічна організація пам'яті комп'ютера

- •57. Принцип ієрархічної організації пам'яті. Характеристики ефективності ієрархічної організації пам'яті

- •58. Кеш пам'ять в складі комп'ютера. Порядок взаємодії процесора і основної пам'яті через кеш пам'ять

- •59. Забезпечення ідентичності вмісту блоків кеш пам'яті і основної пам'яті

- •60. Функція відображення. Типи функцій відображення

- •61. Повністю асоціативне відображення

- •62. Пряме відображення

- •63. Частково-асоціативне відображення

- •64. Порядок заміщення блоків в кеш пам'яті з асоціативним відображенням

- •65. Підвищення ефективності кеш пам'яті

- •66. Статичний та динамічний розподіл пам'яті. Розподіл основної пам'яті за допомогою базових адрес

- •67. Віртуальна пам'ять. Сторінкова організація пам'яті

- •68. Основні правила сторінкової організації пам'яті. Реалізація сторінкової організації пам'яті

- •69. Апаратна реалізація сторінкової таблиці

- •70. Сегментна організація віртуальної пам'яті

- •71. Захист пам'яті від несанкціонованих звернень

- •72. Захист пам'яті за значеннями ключів

- •73. Кільцева схема захисту пам'яті

- •74. Архітектура системної плати

- •75. Синхронізація

- •76. Система шин

- •77. Особливості роботи шини

- •78. Характеристики шин пк

- •79. Шина pcmcia, vbl

- •80. Шина pci

- •82. Універсальна послідовна шина usb

- •83.Типи передач і формати інформації що передається

- •84. Шина scsi

- •85. Адресація пристроїв і передача даних

- •86. Система команд

- •87. Конфігурування пристроїв scsi

- •88. Ігровий адаптер Game-порт

- •89. Відеоадаптери

- •90. Послідовний інтерфейс. Сом-порт

- •91. Програмна модель сом-порта

- •92. Програмування послідовного зв’язку

- •93. Ініціалізація послідовного порта. Передача і прийом даних

- •95. Паралельний інтерфейс lpt-порт. Стандартний режим spp

- •96. Режим epp

- •97. Режим ecp

- •98. Узгодження режимів

- •99. Приклад програмування

- •100. Клавіатура

- •101. Під'єднання зовнішніх пристроїв до комп'ютера

- •102. Розпізнавання пристроїв введення-виведення

- •103. Методи керування введенням-виведенням

- •104. Програмно-кероване введення-виведення.

- •105. Система переривання програм та організація введення-виведення за перериваннями

- •106. Прямий доступ до пам'яті. Введення-виведення під керуванням периферійних процесорів

- •107. Мультиплексний та селекторний канали введення-виведення

- •108. Використання принципів паралельної обробки інформації в архітектурі комп'ютера

- •109. Вибір кількості процесорів в багатопроцесорній системі

- •110. Багатопотокова обробка інформації. Окр

- •111. Класифікація Шора. Класифікація Фліна

- •112. Типи архітектур систем окмд. Типи архітектур систем мкмд

- •113.Організація комп'ютерних систем із спільною пам'яттю

- •114. Організація комп'ютерних систем із розподіленою пам'яттю

- •115. Комунікаційні мережі багатопроцесорних систем

16. Арифметичні операції. Ділення двійкових чисел

Ділення X:Y передбачає визначення частки Q і залишку R відповідно до рівності

X = Q *Y + R,

де X - ділене, Y - дільник.

Алгоритм ділення в комп’ютерах виконується як послідовність операцій віднімання дільника Y від часткового залишку Ri, початкове значення якого рівне значенню діленого X. Знаковий розряд частки визначається за знаками діленого і дільника аналогічно операції множення (табл. 6.7). Приймемо, що значення X і Y завжди відповідають вимозі X<Y.

Існує два варіанти виконання операції ділення двійкових чисел:

зі зсувом залишків ліворуч відповідно до рекурентної формули

R = 2(RM-pY),

де p. = Sign (R , - Y), R0 = X, і=1,2,...п. При цьому i-й розряд частки визначається з виразу q.= NOT (p.);

зі зсувом дільника праворуч відповідно до рекурентної формули

V-R.,-q,,Y2‘

де R0 = X, i=l,2,...n, q. - i-й розряд частки, причому q. = Sign R.

На n-му кроці ділення в обох випадках визначається значення n-го розряду частки та залишок.

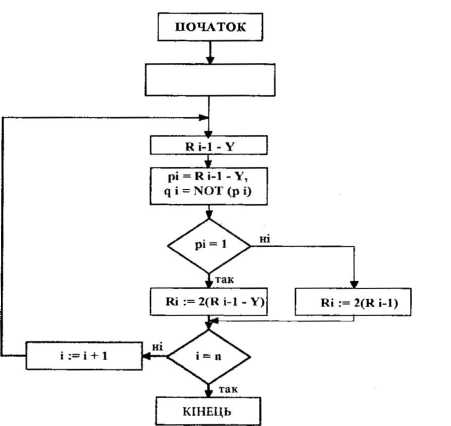

Блок-схема алгоритму ділення за першим варіантом, який має ширше використання, наведена на рис. 6.22.

Рис. 6.22. Блок-схема алгоритму ділення

Ділення може бути виконано двома способами: з відновленням і без відновлення залишку.

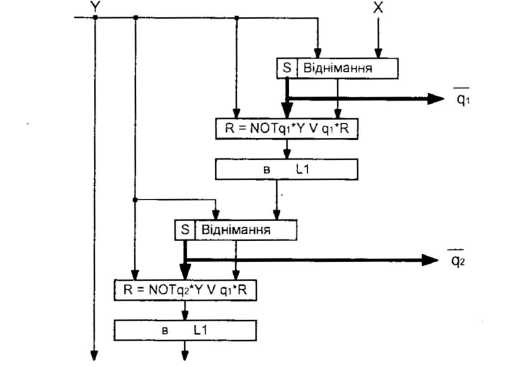

При діленні з відновленням залишку послідовно віднімається дільник від діленого і проводиться аналіз значення поточного залишку. Якщо після чергового віднімання залишок позитивний, то відповідний розряд частки рівний одиниці. При від’ємному залишку розряд частки рівний нулю. В цьому випадку виконується коригуюче збільшення дільника до поточного залишку (відновлення залишку), він зсувається на один розряд ліворуч і процес повторюється. Обчислення проводяться за формулою першого варіанту, де qi = 1, якщо Я. -У>= 0 і qj = 0, якщо II. -У<0. На рис. 6.23 наведено два перші яруси графа, описаного алгоритму ділення.

Розглянемо приклад. Нехай X = 0.1000, = 0.5[0 і Y = 0.1100, = 0.75]0. Тут виконана умова X<Y. Поетапні результати виконання ділення відповідно до блок-схеми алгоритму (рис. 6.22) наступні:

R0 = X = 0.1000;

R, = 2(R0 - Pl х Y) = 2 (0.1000 -Ox 0.1100) = 1.0000, q, = 1;

R2 = 2(R, - p2 x Y) = 2 (1.0000 - 1 x 0.1100) = 0.1000, q2 = 0;

R3 = 2(R2 - p3 x Y) = 2 (0.1000 -Ox 0.1100) = 1.0000, q3 = 1;

R4 = 2(R~ - p4 x Y) = 2 (1.0000 -Ox 0.1100) = 1.0000, q. = 0;

Таким чином маємо Q = q,q,q3q4 = 0.1010.

У методі ділення без відновлення залишку віднімання, що викликало появу від’ємного залишку при визначенні значення розряду частки, еквівалентне двом відніманням при визначенні сусіднього молодшого розряду частки. Ділення виконується за тим же співвідношенням зі зсувом залишків ліворуч відповідно до рекурентної формули R = 2(RM - PiY),

де р. = 1, якщо (R - Y) > = 0, та р. = -1, якщо (R. 1 - Y) < 0, R0 = X, і=1,2,...п. При цьому i-й розряд частки визначається з виразу q. = Sign R

Ділення чисел, які представлені в оберненому та доповняльному кодах, можна виконувати за правилами ділення в прямих кодах при відповідному перетворенні операн- дів в цей код. Розглянемо виконання операції ділення без відновлення залишків чисел, представлених доповняльними кодами. У цьому випадку ділення зводиться до послідовності додавань і віднімань дільника від діленого, а потім часток і часткових залишків і їх зсуву на розряд ліворуч за наступними виразами:

R. = 2R.ч - Y, при Sign R = Sign Y;

R. = 2R , + Y, при Sign R. =/ Sign Y,

для i=l,2,...,n+l при 2R0 = X та Sign R0 = Sign X. Тут Sign R - знак і-го часткового залишку, Sign Y, Sign X - відповідно знаки Y та X.

При цьому розряди частки визначаються наступним чином: q = 1, якщо Sign R. = Sign Y, q = 0, якщо Sign R =/ Sign Y.

Операція виконується за n+1 кроків і дає значення частки в доповняльному коді.