- •1.Що таке комп'ютер?

- •2. Дайте визначення алгоритму.

- •3. Дайте хронологію появи перших комп'ютерів.

- •4. Які основні функції комп'ютера? Які основні функціональні вузли комп'ютера? їх завдання

- •20. Як узгодити передачу даних між повільними і швидкими вузлами комп'ютера?

- •21. Поясніть роботу комп'ютера з одношинною структурою.

- •22. Що таке архітектура комп'ютера?

- •28. Які існують ненейманівські архітектури комп'ютерів? Які їх відмінні риси?

- •29. Назвіть два основних напрями використання комп'ютерів.

- •30. Що розуміється під паралельною обробкою?

- •31. Які є типи комп'ютерів?

- •43. В яких випадках використовується формат представлення чисел з рухомою-рухомою

- •45. Приведіть двійково-десятковий код з 2 з 5 та назвіть вигоди від його використання.

- •46. Приведіть двійково-десятковий код з надлишком 3 та назвіть вигоди від його викорис

- •47. Поясніть суть кодування чисел кодом ebcdic.

- •3. Як кодуються команди в комп ютері?

- •4. Що таке асемблерна мова і для чого використовується асемблер?

- •5. Як класифікуються команди за типами операцій?

- •6. Назвіть команди обробки даних

- •7. Назвіть базові операції зсуву

- •8. Назвіть команди переміщення даних

- •9. Поясніть принципи організації послідовного виконання команд і розгалуження

- •10. Назвіть команди передачі керування

- •15. Якою є продуктивність 4-ярусного конвеєра з тактом 20нс при виконанні 100 команд?

- •16. Назвіть можливі конфлікти, які можуть сповільнити конвеєр

- •17. Які використовуються формати команд при роботі з основною пам яттю?

- •18. Які формати команд використовуються при роботі з регістрами процесора?

- •3.5.1. Формати команд комп'ютерної системи ibm 370

- •19. Які головні критерії вибору формату команд?

- •20. Поясніть різницю між акумуляторною архітектурою, стековою архітектурою та архітектурою

- •21. Поясніть різницю між архітектурами системи команд типу регістр регістр, регістр

- •22. Які переваги та недоліки команд з фіксованим та зі змінним форматом? Який формат є

- •23. Яким чином знаходяться дані в пам'яті коли в команді відсутня адресна частина?

- •24. Яка програма має більше команд: та, що складається з безадресних команд, одноадресних

- •25. Що таке спосіб адресації?

- •26. Які є способи адресації пам'яті? їх призначення?

- •27. Як організовується стекова пам ять?

- •28. Поясніть порядок організації обчислень при використанні стекової адресації

- •29. Наведіть приклади використання інфіксної, префіксної та постфіксної форм запису арифметичних

- •30. Наведіть приклади безпосередньої, прямої, непрямої, відносної та базової адресацій

- •31. Чим відрізняється індексна адресація від базової?

- •32. Чому необхідна велика кількість різних способів адресації?

- •33. Які формати команд використовуються в системі ibm 370? їх відмінності

- •34. Які формати команд використовуються в машині Cyber-70?

- •35. Які формати команд використовуються в комп'ютері dlx?

- •36. Дайте класифікацію архітектур комп'ютера за складом системи команд

- •37. Яка різниця між комп'ютерами із складною та простою системами команд?

- •38. Які особливості має комп'ютер з доповненою системою команд?

- •39. Які переваги має комп'ютер з орієнтованою системою команд?

- •1. Місце процесора в комп'ютері та його функції.

- •2. Що таке командний цикл?

- •3. Дві основні фази командного циклу.

- •4. Основні вузли процесора.

- •5. Одношинна структура процесора комп'ютера із складною системою команд і його зв'язки з

- •6. Виконання процесором операції "Вибірка слова з пам'яті".

- •7. Виконання процесором операції "Запам'ятовування слова в пам'яті".

- •8. Виконання процесором операції обміну між регістрами.

- •9. Виконання процесором арифметичних і логічних операцій.

- •10. Порівняння одношинної та багатошинної структур процесора комп'ютера із складною

- •11. Чому в процесорі комп'ютера із складною системою команд команда виконується за багато

- •12. Чому в процесорі комп'ютера із складною системою команд потрібна складна система

- •13. Чому в процесорі комп'ютера із складною системою команд організація конвеєризації виконання команд складніша, ніж у процесорі комп'ютера з простою системою команд?

- •14. Основні вимоги до процесора комп'ютера з простою системою команд.

- •15. Сформуйте правила вибору системи команд комп'ютера з простою системою команд.

- •16. Чому в системі команд комп'ютера з простою системою команд відносно небагато операцій

- •26. Проаналізуйте та поясніть мікродії, що виконуються на сходинці id конвеєра комп'ютера

- •27. Проаналізуйте та поясніть мікродії, що виконуються на сходинці ех конвеєра комп'ютера dlx при виконанні команди алп.

- •28. Проаналізуйте та поясніть мікродії, що виконуються на сходинці ех конвеєра комп'ютера dlx при виконанні команд завантаження і збереження (load/store).

- •29. Проаналізуйте та поясніть мікродії, що виконуються на сходинці ех конвеєра комп'ютера dlx при виконанні команди умовного переходу (branch).

- •30. Проаналізуйте та поясніть мікродії, що виконуються на сходинці mem конвеєра комп'ютера

- •31. Проаналізуйте та поясніть мікродії, що виконуються на сходинці mem конвеєра комп'ютера dlx при виконанні команд завантаження або збереження.

- •32. Проаналізуйте та поясніть мікродії, що виконуються на сходинці wb конвеєра комп'ютера dlx при виконанні команд алп.

- •33. Проаналізуйте та поясніть мікродії, що виконуються на сходинці wb конвеєра комп'ютера dlx при виконанні команди load.

- •34. Основна ідея суперконвеєрних процесорів.

- •35. Суперскалярні процесори - структура та принцип роботи.

- •36. Процесори векторних комп'ютерів - структура та принцип роботи.

- •37. Наведіть класифікацію архітектури комп'ютера за рівнем суміщення в ньому опрацювання команд та даних.

- •2. Назвіть 3 класи конфліктів у конвеєрі команд та причини їх появи.

- •3. Які є дві групи структурних конфліктів?

- •6. Чому розробники допускають наявність структурних конфліктів?

- •9. Які є способи вирішення структурних конфліктів?

- •11. Назвіть три можливі конфлікти за даними.

- •15. Які можливі конфлікти за даними?

- •16. Які є методи зменшення впливу залежностей між даними на роботу конвеєра команд?

- •34. Поясніть суть способу введення буфера попередньої вибірки з метою зниження втрат на

- •35. Поясніть суть способу дублювання початкових ярусів конвеєра з метою зниження втрат

- •36. Поясніть суть способу затримки переходу з метою зниження втрат на виконання команд

- •37. Поясніть суть способу статичного передбачення переходу з метою зниження втрат на виконання

- •38. Назвіть методи статичного передбачення умовного переходу.

- •39. Поясніть суть методу повернення, який застосовується при статичному передбаченні

- •40. Поясніть суть методу профілювання, який застосовується при статичному передбаченні

- •41. Поясніть суть методу статичного передбачення умовного переходу, за яким результат переходу

- •42. Поясніть суть методу статичного передбачення умовного переходу, за яким результат переходу

- •43. Поясніть суть динамічного передбачення переходу.

- •44. Що таке таблиця історії переходів? Як вона реалізується?

- •45. Наведіть однорівневу схему передбачення переходу з формуванням адреси таблиці історії

- •46. Наведіть однорівневу схему передбачення переходу з формуванням адреси таблиці історії

- •47. Наведіть однорівневу схему передбачення переходу з комбінованим формуванням адреси

- •53. Наведіть основні ідеї, покладені в основу архітектури еріс.

6. Виконання процесором операції "Вибірка слова з пам'яті".

Нехай адреса комірки основної пам'яті знаходиться в регістрі Ргі, а дані потрібно

розмістити в регістрі Рг2.

Для вибірки із основної пам'яті необхідно виконати наступну послідовність операцій:

1. РгА := Ргі (запис до регістра адреси РгА вмісту регістра Ргі).

2. Зчитування (виконання операції зчитування команди з комірки основної пам'яті

до регістра РгД шляхом подання сигналу Read на вхід керування режимом роботи основної

пам'яті та сигналу запису до регістра РгД).

3. Чекання на сигнал підтвердження зчитування.

4. Рг2 := РгД (запис до регістра Рг2 даного з регістра РгД).

Пункт 3 виконується при асинхронному принципі обміну між процесором і основною

пам'яттю, коли потрібно чекати на сигнал підтвердження зчитування. При синхронному

принципі обміну чекати на сигнал підтвердження зчитування не потрібно,

оскільки до подання сигналу запису в регістр РгД передбачається гарантована наявність

даного на його вході.

7. Виконання процесором операції "Запам'ятовування слова в пам'яті".

Нехай слово, яке запам'ятовується в основній пам'яті, знаходиться в регістрі Рг2, а

адреса - в регістрі Ргі. Тоді послідовність операцій буде наступною:

1. РгА := Ргі (запис до регістра адреси РгА вмісту регістра Ргі).

2. РгД := Рг2 (запис до регістра даних РгД вмісту регістра Рг2), запис (виконання операції

запису слова з регістра РгД до комірки основної пам'яті шляхом подання сигналу

Write на вхід керування режимом роботи основної пам'яті).

3. Чекання на сигнал підтвердження запису (при асинхронному принципі обміну

між процесорам і основною пам'яттю).

8. Виконання процесором операції обміну між регістрами.

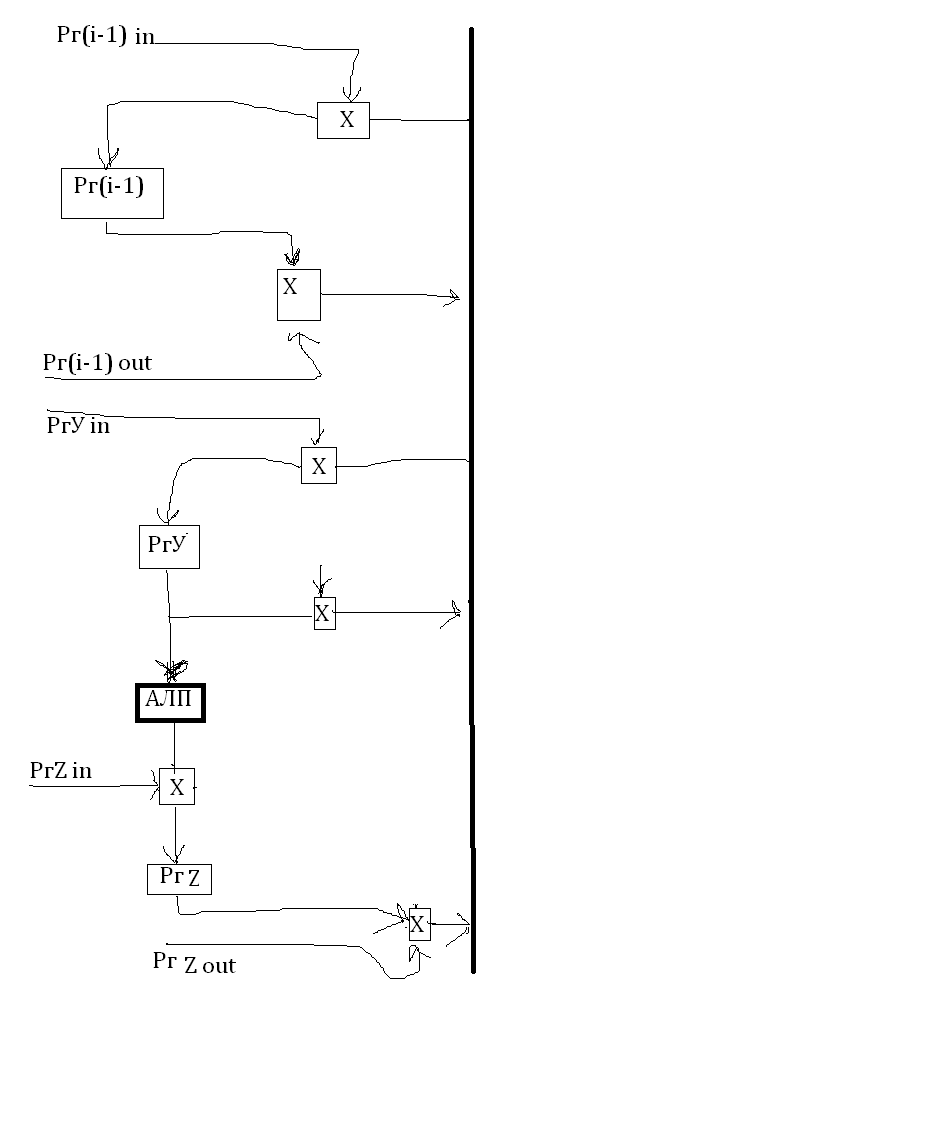

Символьне зображення вхідних і вихідних елементів регістрів процесора показане

на рис. 4.2 у вигляді ключів, які пропускають або не пропускають інформацію з входу

на вихід, залежно від значення сигналів керування на їх входах. Тут сигнал керування

входом і-го регістра Ргі позначено як Ргі in, а сигнал керування виходом і-го регістра Ргі

позначено як Ргі out. В конкретній схемі регістра це можуть бути, наприклад, вхід запису

числа до регістра та його тристабільний вихід.

Рис. 4.2. Фрагмент схеми процесора з вхідними та вихідними елементами регістрів

Подання 1 на вхід керування регістра Priout з'єднує вихід регістра Ргі з шиною, а подання

1 на вхід керування регістра Ргііп записує число з шини в регістр Ргі. Подаючи на регістри

вказані сигнали, можна переписувати числа з одного регістра в інший наприклад, для перезапису

числа із регістра РгЗ до регістра Рг5 необхідно подати наступні сигнали: РгЗош, Рг5іп.

9. Виконання процесором арифметичних і логічних операцій.

Арифметико-логічний пристрій (АЛП) процесора призначений для виконання операцій

обробки даних. Тип виконуваної операції вказується кодом на вході керування

АЛП. В АЛП, зокрема, виконуються такі операції: зсув - зміщення кодів, які зберігаються

в регістрах регістрового файлу, вліво або вправо на задане число розрядів; додавання

до слова 1 або -1 - операція рахунку; дешифрування - перетворення двійкових кодів у

сигнали (однорядний код); шифрування - перетворення однорядного коду в двійковий;

порівняння - визначення відношення старшинства двох чисел або їх рівності; пороз-

рядне доповнення - формування оберненого коду; порозрядні логічні множення і додавання

двох чисел; порозрядне додавання двох чисел по модулю; додавання двох чисел.

Звичайно, цей перелік може бути розширений.

Розглянемо виконання операції додавання двох чисел з регістрів Ргі і Рг2 з записом

результату в регістр РгЗ на одношинній структурі процесора, представленій на рис. 4.1:

1) Priout, РгУіп (запис до вхідного регістра АЛП РгУ вмісту регістра Ргі).

2) Pr2out, Add, PrZin (подання числа з регістра Рг2 на внутрішню шину процесора,

звідки воно поступає на другий вхід АЛП, виконання в АЛП операції додавання чисел з

регістра РгУ та з шини і запам'ятовування результату в регістрі PrZ).

3) Р й о и і , РгЗіп (запис до регістра РгЗ вмісту регістра Рг2).

Подібним чином виконуються інші вище перераховані операції. Необхідно відзначити,

що сигнали Ргіоиі та Рг)іп, де і т а ; - номери регістрів, мають бути рознесеними в

часі для забезпечення коректного перезапису інформації з одного регістра до іншого з

врахуванням часу спрацювання їх вхідних та вихідних схем, ємності провідників шини

та затримки в комбінаційних схемах АЛП. Цей час визначає такт роботи процесора.