- •1. Дати характеристику повного дешифратора

- •2. Навести принципову схему 4-канального мультиплексора з двома адресними входами

- •3. Дати характеристику неповного дешифратора

- •4. Етапи побудови логічної схеми

- •5. Дати характеристику мультиплексора

- •6. Прийоми, що використовуються у випадку, коли число ле більше за необхідне

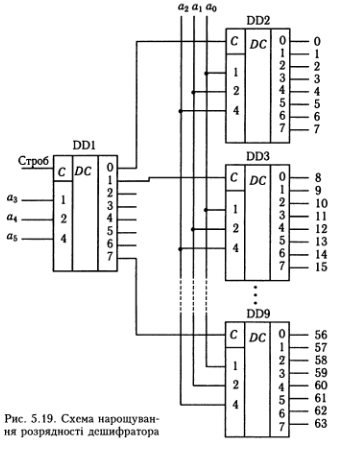

- •7. Як реалізовується збільшення розрядів дешифратора?

- •8. Як реалізовується підключення дешифратора на селекцію (вибір) заданих вхідних кодів?

- •9. Операціїї, що виконують пріорітетні шифратори.

- •10. Навести класифікацію цифрових пристроїв за способом кодування двійкових змінних

- •11. Генератор тактових імпульсів

- •12. Два роди кодування імпульсних сигналів.

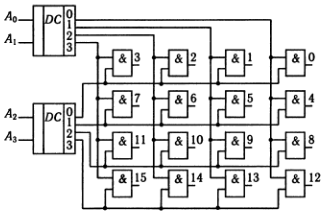

7. Як реалізовується збільшення розрядів дешифратора?

Багатоступінчасті структури. Переваги багатоступінчастих структур виявляються у разі збільшення розрядності вхідного коду. Значного поширення вони набули при побудові мікросхем пам'яті. Так, при побудові дешифратора 20-розрядного вхідного коду (використовують при побудові ІС пам’яті обсягом 1 Мбайт) паралельний дешифратор потребує 2,097-107 умовних апаратних одиниць. При одноразовому використанні принципу побудови пірамідального дешифратора буде потрібно 1,20•107, а при одноразовому використанні принципу багатоступінчастого дешифратора — 2,118•106 умовних апаратних одиниць.

Принцип побудови n – розрядного дешифратора: N = 2 • 2n + 2(n / 2)2n/2.

Рис. 5.17. Схема багатоступінчастого дешифратора

Рис. 5.19. Схема нарощування розрядності дешифратора

8. Як реалізовується підключення дешифратора на селекцію (вибір) заданих вхідних кодів?

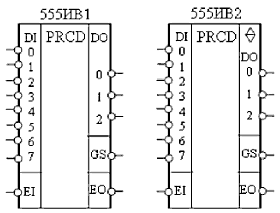

9. Операціїї, що виконують пріорітетні шифратори.

Рис. 1.4. Умовне графічне позначення пріоритетного шифратора

Пріоритетні шифратори використовуються для побудови контролерів клавіатур, контролерів переривань для ЕОМ, а також с основними вузлами перетворювачів кодів.

Окрім інформаційних входів DI та виходів 3-розрядного двійкового коду DO, мікросхема мас додаткові виводи, що виконують такі функції:

- El (Enable Input) — вхід дозволу роботи мікросхеми. Активний рівень низький.

- CiS (Group Signal) — вихід групового сигналу, який при GS =0 свідчить про наявність хоча б одного збудженого входу. Активний рівень низький.

- ЕО (Enable Output) — вихід сигналу дозволу, який при ЕО = 0 фіксує високі рівні на усіх інформаційних входах, тобто свідчить про відсутність збуджених входів. Активні рівні збуджених входів низькі.

10. Навести класифікацію цифрових пристроїв за способом кодування двійкових змінних

За способом кодування двійкові змінні елементів цифрових пристроїв поділяють на імпульсні, динамічні, потенціальні, імпульсно-потенціальні та фазові.

В імпульсних елементах «1» показує наявність електричного імпульсу напруги або струму, а «0» — відсутність відповідного імпульсу.

У динамічних елементах «1» показує пачку імпульсів або потенціал, що поновлюється через необхідний інтервал часу, а «0» — відсутність імпульсів (або навпаки).

У потенціальних елементах початкові і скінченні двійкові змінні кодують різною величиною електричного потенціалу. Для потенціальних елементів часто застосовують поняття позитивної і негативної логіки, яке відображає взятий спосіб кодування двійкової змінної конкретної серії елемента. Під позитивною логікою розуміють кодування «1» високим і «0» — низьким потенціалом, а під негативною логікою розуміють кодування «1» низьким і «0» — високим потенціалом.

В імпульсно-потенціальних елементах на входи елементів можуть подаватися як потенціальні рівні, так й електричні імпульси, причому вихідні сигнали зазвичай мають імпульсний характер. Розподіл сипіалів на імпульсні й потенціальні відносний. Тип сигналу визначають через тривалість такту, залежно від частоти тактового генератора цифрового пристрою. Імпульсний сипіал — сигнал з тривалістю, яка менша за тривалість такту. Потенціальний сигнал - сигнал з тривалістю, яка не менша за тривалість такту.

У фазових елементах застосовують сигнали у вигляді синусоїдної напруги, а значення 1 і 0 двійкових змінних кодуються фазою синусоїдної напруги відносно опорної напруги. Фазовий принцип кодування двійкових змінних застосовують переважно у пристроях аналого-цифрового типу.