- •1. Дати характеристику повного дешифратора

- •2. Навести принципову схему 4-канального мультиплексора з двома адресними входами

- •3. Дати характеристику неповного дешифратора

- •4. Етапи побудови логічної схеми

- •5. Дати характеристику мультиплексора

- •6. Прийоми, що використовуються у випадку, коли число ле більше за необхідне

- •7. Як реалізовується збільшення розрядів дешифратора?

- •8. Як реалізовується підключення дешифратора на селекцію (вибір) заданих вхідних кодів?

- •9. Операціїї, що виконують пріорітетні шифратори.

- •10. Навести класифікацію цифрових пристроїв за способом кодування двійкових змінних

- •11. Генератор тактових імпульсів

- •12. Два роди кодування імпульсних сигналів.

1. Дати характеристику повного дешифратора

Дешифратори (декодери) є комбінаційними пристроями, призначеними для перетворення кодованих двійкових вхідних сигналів у сигнали керування виконавчими пристроями, пристроями відображення інформації і т.п.

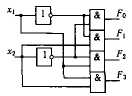

Приклад схеми дешифратора 3 на 8

Дешифратор називається повним, якщо кількість виходів рівна кількості можливих наборів вхідних сигналів, тобто n=2m

У повному дешифраторі кожній комбінації значень вхідних сигналів відповідає сигнал, який дорівнює 1, тільки на одному виході. Інакше кажучи, залежно від вхідного коду на виході збуджується одне з кіл.

а) б)

Рисунок 5.3 – Дешифратор 2x4:

а - принципова схема, б - позначення

Особливість дешифратора: початковий стан всіх виходів декодера - "1". Кожному вхідному двійковому коду відповідає рівень логічного нуля на одному з восьми виходів декодера, на інших виходах при цьому присутній рівень логічної одиниці.

Входи & E дозволяють роботу декодера. На верхній вхід дозволу подається рівень логічної одиниці, на нижні входи дозволу подеется рівень логічного нуля. При інших комбінаціях рівнів напруг на цих входах напруга на всіх його виходах одно рівню логічної одиниці.

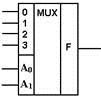

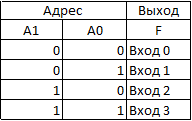

2. Навести принципову схему 4-канального мультиплексора з двома адресними входами

Рисунок 1.1. Умовне графічне позначення і таблиця функціонування мультиплексора 4:1

Тут входи 0,1,2,3 - інформаційні входи, А0 і А1-адресні, код на яких визначає, з якого з входів будуть взяті сигнали для передачі на вихід F. Принцип визначення номера входу по адресній комбінації такий же, як у дешифратора і демультиплексор. При т-адресних входах мультиплексор може мати в залежності від конструкції до 2m входів.

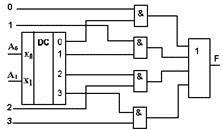

Рисунок 1.2. Схема мультиплексора 4:1

3. Дати характеристику неповного дешифратора

Дешифратор (декодер) виконує операцію перетворення m-елементного паралельного коду на входах в сигнал високого (або низького) рівня на одному з його n виходів. Дешифратор називається повним, якщо кількість виходів рівна кількості можливих наборів вхідних сигналів, тобто n=2m. Неповний дешифратор має меншу кількість виходів.

4. Етапи побудови логічної схеми

Етап 1. Укладання таблиці істинності. Етап 2. Якщо функція визначена не на всіх наборах аргументів, то потрібно ліквідувати неоднозначність таблиці. Етап 3. За цілком визначеною таблицею скласти ДДНФ. Етап 4. Мінімізувати ДДНФ будь-якими доступними методами. Етап 5. Реалізувати знайдені диз’юнктивні форми на логічному базисі заданої серії елементів. Спробувати варіанти реалізації на І —АБО —НЕ і на І-НЕ, АБО —НЕ. Етап 6. Оцінити властивості двоїстості логічної схеми з урахуванням зміни числа вхідних і вихідних інверторів. Етап 7. Спробувати знайти таку декомпозицію функції, щоб кожен фрагмент отриманого розкладання залежав від меншого числа аргументів, ніж початкова функція. Етап 8. Вибрати з отриманих на етапах 5, 6, 7 варіантів найпридатніший з погляду поставленої мети.