- •1. Понятие интегральной схемы:

- •2. Составляющие стоимости ис и пути ее уменьшения

- •3. Типы интегральных схем по технологическому признаку:

- •4. Классификация ис по степени интеграции.

- •Типы выходов ис (с открытым коллектором, с открытым эмиттером, с тремя состояниями).

- •Базовый элемент транзисторно-транзисторной логики (принципиальная схема, работа элемента). Каким состоянием выходного каскада ис определяется нагрузочная способность элемента ис ттл?

- •1. Базовый элемент транзисторно-транзисторной логики

- •Базовый элемент ис на транзисторах Шотки (принципиальная схема, отличия от классических ттл). Почему в выходном каскаде ттл ис возникают броски тока и как с ними бороться?

- •1. Базовый элемент ис диодно-транзисторных схем на диодах и транзисторах Шотки

- •5. Подключение неиспользуемых логических элементов и входов ис ттл. Снижение нагрузок на выходах логических элементов. Подключение светодиодов.

- •2. Неиспользуемые логические элементы

- •Цифровые ис на n-moп и p-моп структурах (принципиальная схема инвертора, работа; принципиальная схема базового элемента, его работа).

- •1. Цифровые ис на n-moп структурах

- •Цифровые ис на кмоп-структурах (принципиальная схема инвертора и его работа; принципиальная схема элемента или-не и его работа). Особенности применения ис кмоп.

- •1. Цифровые ис на кмоп-стуктурах

- •Достоинства и недостатки ис кмоп. Согласование ис ттл-уровней с ис кмоп, ис кмоп с ис ттл-уровней.

- •1. Достоинства и недостатки ис кмоп

- •2. Согласование ис ттл-уровней с ис кмоп, ис кмоп с ис ттл-уровнй

- •Сумматоры групповой структуры (групповой сумматор с цепным переносом, сумматор с условным переносом, сумматор с параллельным и межгрупповым переносом).

- •1.. Сумматоры групповой структуры

- •Реализация мультиплексоров (назначение, таблица функционирования, мультиплексная формула, реализация мультиплексора 4-1 на элементах и-не).

- •Схемотехническая реализация двоичных дешифраторов (описание функционирования, обозначение на функциональной схеме, схема дешифратора 3-8 на элементах и).

- •Матричные умножители (математические выражения, схема множительно-суммирующего блока для четырехразрядных сомножителей, увеличение разрядности до 4х4 из двух 4х2).

- •Организация контроля правильности функционирования устройств обработки данных (контроль чётности, мажоритарные схемы голосования, код Хэмминга – принципиальные схемы, таблицы функционирования).

- •Асинхронный и синхронный (тактируемый) rs-триггеры (схемы на элементах и-не, или-не, таблицы функционирования и временные диаграммы, время задержки).

- •Классификация, краткое описание и таблицы функционирования триггеров.

- •Последовательные сдвигающие регистры.

- •Двоичные счетчики.

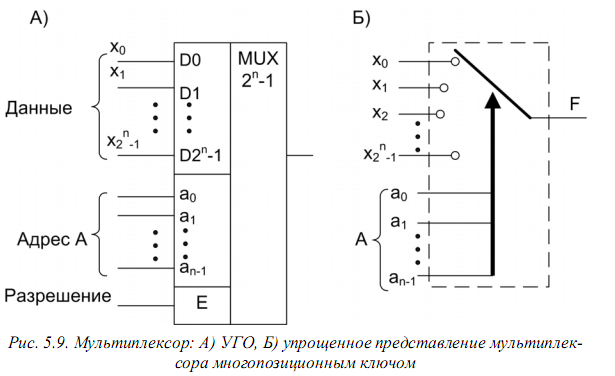

Реализация мультиплексоров (назначение, таблица функционирования, мультиплексная формула, реализация мультиплексора 4-1 на элементах и-не).

Мультиплексор (от англ. слова multiplexer) – это функциональный узел, осуществляющий подключение (коммутацию) одного из нескольких входов данных к выходу под управлением управляющего (адресующего) слова.

Адресующий код А задает переключателю определенное положение, соединяя с выходом F из информационных входов xi. При нулевом адресующем коде переключатель занимает верхнее положение x0, с увеличением кода на единицу переходит в соседнее положение, подключая к выходу вход x1 и т.д.

Работа мультиплексора описывается выражением:

![]()

При любом значении адресующего кода все слагаемые, кроме одного, равны нулю.

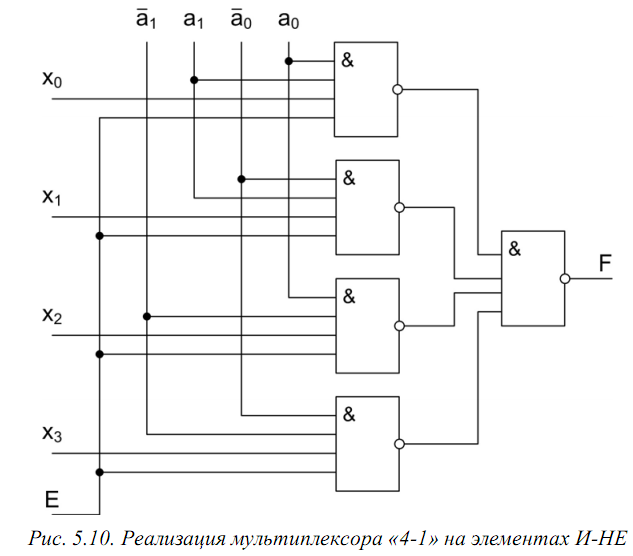

Реализация мультиплексора 4-1 на элементах И-НЕ

Таблица истинности

А0 |

А1 |

F |

0 |

0 |

Х0 |

0 |

1 |

Х1 |

1 |

0 |

Х2 |

1 |

1 |

Х3 |

Схемотехническая реализация двоичных дешифраторов (описание функционирования, обозначение на функциональной схеме, схема дешифратора 3-8 на элементах и).

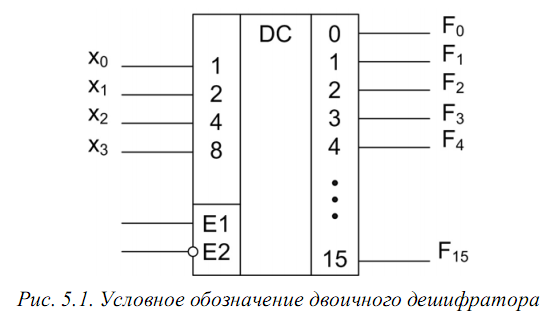

Двоичным дешифратором или декодером (от англ. слова decoder) чаще всего называют кодирующее устройство, преобразующее двоичный код в код «1 из N». Из всех m выходов дешифратора активный уровень имеется только на одном, а именно на том, номер которого равен поданному на вход двоичному числу. На всех остальных выходах дешифратора уровни напряжения неактивные.

Входы дешифратора (их иногда называют адресными входами) обозначают их двоичными весами. Кроме информационных входов дешифратор обычно имеет один или несколько разрешающих (управляющих, стробирующих) входов Е (от англ. слова

enable – разрешать). Дешифратор, имеющий разрешающий вход, иногда называют декодер-демультиплексор и на условном обозначении вместо символа DC используют символ DX. При наличии разрешения по этому входу дешифратор работает как обычно, при его отсутствии на всех выходах устанавливаются неактивные уровни независимо от поступившего кода адреса. Если разрешающих входов несколько, то общий сигнал

разрешения работы образуется как конъюнкция сигналов отдельных входов. Часто дешифратор имеет инверсные выходы. В этом случае только один выход имеет нулевое значение, а все остальные – единичные. При запрещении работы дешифратора на всех его выходах будет присутствовать логическая единица.

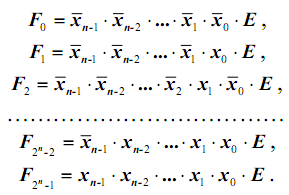

Функционирование дешифратора описывается системой конъюнкций:

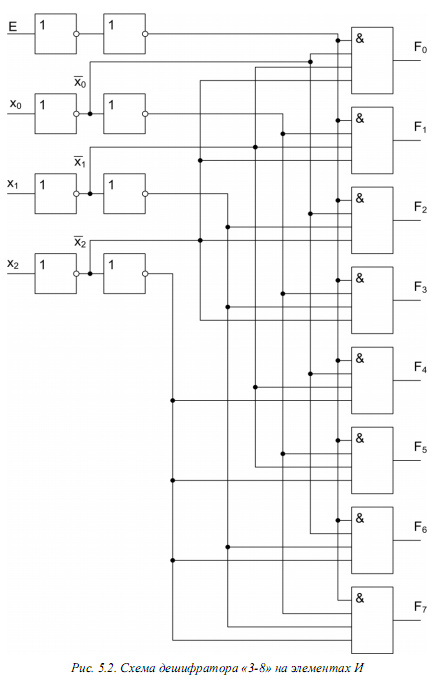

Схемотехнически дешифратор представляет собой совокупность конъюнкторов, не связанных между собой.

Компараторы (определение компаратора, выражения для компаратора: признак равенства разрядов, признак неравенства разрядов, признак равенства слов; принципиальная схема четырехразрядного компаратора на основе сумматора).

Компараторы (устройства сравнения) определяют отношения между двумя словами.

В процессе обработки данных возникает необходимость проверить логические условия двух слов информации: А=В; А≠В; А<В; А>В; А≤В; А≥В. Основные отношения, через которые можно выразить остальные, принято использовать два: А=В; А>В.

Функции, вырабатываемые компараторами, определяют следующим образом: они принимают единичное значение (истинны), если соблюдается условие, указанное в индексе обозначения функции. Например, функция FA=B=1, если А=В и принимает нулевое значение при А≠В. Приняв в качестве основных отношения «равно» и «больше» для остальных можно записать:

![]()

Устройства сравнения на равенство строятся н

операций над одноименными разрядами обоих с

Признак равенства разрядов

![]()

Признак неравенства разрядов

![]()

Построение четырехразрядного компаратора на основе сумматоров

Двоичные и приоритетные шифраторы (назначение двоичного шифратора, его условное обозначение на функциональной схеме; функция, выполняемая приоритетным шифратором, таблица функционирования восьмиразрядного приоритетного шифратора, выражения для выходов приоритетного шифратора, обозначение на функциональной схеме приоритетного шифратора).

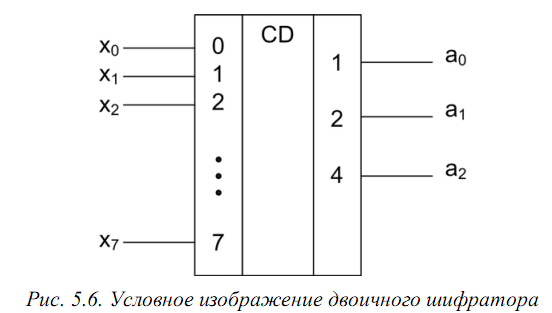

Двоичные шифраторы выполняют операцию, обратную по отношению к операции дешифратора: они преобразуют код «1 из N» в двоичный. При подаче на один (обязательно на один, и не более) из входов шифратора на его выходе формируется двоичный код номера возбужденной входной линии. Полный двоичный шифратор имеет 2n входов и n выходов.

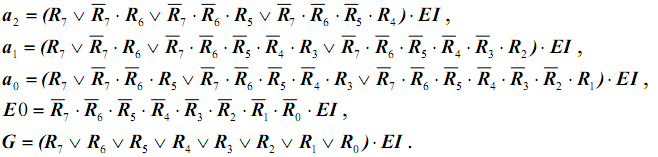

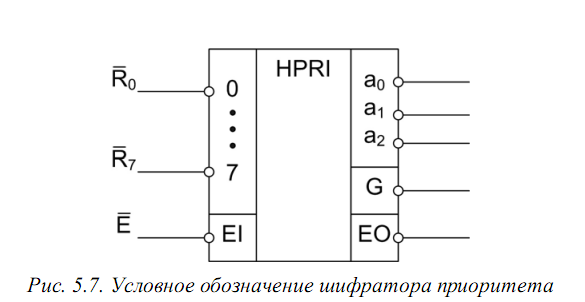

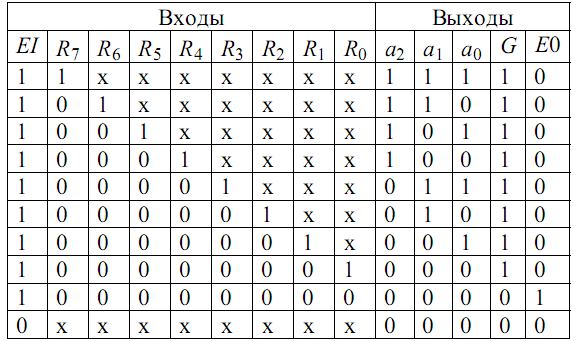

Функционирование восьмиразрядного шифратора приоритета приведено в табл. В табл. приняты обозначения: EI – сигнал разрешения работы данного шифратора; R7…R0 – сигналы запросов на входах шифратора; а2…а0 – значения разрядов выходного двоичного кода, формирующего номер старшего запроса; G – сигнал, отмечающий наличие запросов на входе данного шифратора. Сигналы а2…а0 и G формируются

при значении EI=1 (работа шифратора разрешена). При EI=0 независимо от состояний входов запросов все выходные сигналы приоритетного шифратора становятся нулевыми.

Из табл. 5.1 можно получить следующие выражения для выходных функций а2, а1, а0, E0, G: