- •1. Понятие интегральной схемы:

- •2. Составляющие стоимости ис и пути ее уменьшения

- •3. Типы интегральных схем по технологическому признаку:

- •4. Классификация ис по степени интеграции.

- •Типы выходов ис (с открытым коллектором, с открытым эмиттером, с тремя состояниями).

- •Базовый элемент транзисторно-транзисторной логики (принципиальная схема, работа элемента). Каким состоянием выходного каскада ис определяется нагрузочная способность элемента ис ттл?

- •1. Базовый элемент транзисторно-транзисторной логики

- •Базовый элемент ис на транзисторах Шотки (принципиальная схема, отличия от классических ттл). Почему в выходном каскаде ттл ис возникают броски тока и как с ними бороться?

- •1. Базовый элемент ис диодно-транзисторных схем на диодах и транзисторах Шотки

- •5. Подключение неиспользуемых логических элементов и входов ис ттл. Снижение нагрузок на выходах логических элементов. Подключение светодиодов.

- •2. Неиспользуемые логические элементы

- •Цифровые ис на n-moп и p-моп структурах (принципиальная схема инвертора, работа; принципиальная схема базового элемента, его работа).

- •1. Цифровые ис на n-moп структурах

- •Цифровые ис на кмоп-структурах (принципиальная схема инвертора и его работа; принципиальная схема элемента или-не и его работа). Особенности применения ис кмоп.

- •1. Цифровые ис на кмоп-стуктурах

- •Достоинства и недостатки ис кмоп. Согласование ис ттл-уровней с ис кмоп, ис кмоп с ис ттл-уровней.

- •1. Достоинства и недостатки ис кмоп

- •2. Согласование ис ттл-уровней с ис кмоп, ис кмоп с ис ттл-уровнй

- •Сумматоры групповой структуры (групповой сумматор с цепным переносом, сумматор с условным переносом, сумматор с параллельным и межгрупповым переносом).

- •1.. Сумматоры групповой структуры

- •Реализация мультиплексоров (назначение, таблица функционирования, мультиплексная формула, реализация мультиплексора 4-1 на элементах и-не).

- •Схемотехническая реализация двоичных дешифраторов (описание функционирования, обозначение на функциональной схеме, схема дешифратора 3-8 на элементах и).

- •Матричные умножители (математические выражения, схема множительно-суммирующего блока для четырехразрядных сомножителей, увеличение разрядности до 4х4 из двух 4х2).

- •Организация контроля правильности функционирования устройств обработки данных (контроль чётности, мажоритарные схемы голосования, код Хэмминга – принципиальные схемы, таблицы функционирования).

- •Асинхронный и синхронный (тактируемый) rs-триггеры (схемы на элементах и-не, или-не, таблицы функционирования и временные диаграммы, время задержки).

- •Классификация, краткое описание и таблицы функционирования триггеров.

- •Последовательные сдвигающие регистры.

- •Двоичные счетчики.

5. Подключение неиспользуемых логических элементов и входов ис ттл. Снижение нагрузок на выходах логических элементов. Подключение светодиодов.

2. Неиспользуемые логические элементы

ИС содержат в одном корпусе несколько логических элементов, связанных общим питанием. При составлении схемы отдельные логические элементы остаются свободными. Рекомендуется такие элементы включать так, чтобы их выходы имели высокий потенциал (в этом состоянии элемент потребляет минимальную мощность), для чего входы ЛЭ И-НЕ и ИЛИ-НЕ соединяют с общей шиной. В этом случае рассеиваемая мощность минимальна, а сами схемы можно использовать в качестве генератора логической единицы.

Неиспользуемые входы можно объединить с используемыми, если это не ведет к превышению нагрузочной способности предшествующего каскада. Если на неиспользуемом входе должен быть логический ноль, то подключают к общей шине. Для создания уровня лог. 1 напряжение на входе должно находиться в пределах 2,4-3,6 В; непосредственное подключение входов ТТЛ к проводу питания недопустимо из-за большого входного тока.

Логическую 1 на входах ТТЛ можно обеспечить:

• подключив к выходу свободного элемента, чаще всего И-НЕ, входы которого соединены с общей шиной (генератор константы 1); максимальное число входов, подключаемых к элементу, определяется

нагрузочной способностью.

• на неиспользуемые входы подают напряжение 2,4-3,6 В от отдельного источника питания;

• неиспользуемые входы подсоединяют к своему источнику питания через ограничивающий резистор сопротивлением 1-2 кОм; к этому резистору допускается присоединять до 20 входов микросхем ТТЛ .

• неиспользуемые входы, на которых постоянно должна быть лог. 1, в крайнем случае можно оставлять свободными: за счет токов утечки на них устанавливается нужное напряжение, но надо иметь в виду, что этот способ ведет к уменьшению быстродействия и помехоустойчивости, особенно при большой частоте переключений, т.к. свободные входы подвержены действию наводок.

Цифровые ис на n-moп и p-моп структурах (принципиальная схема инвертора, работа; принципиальная схема базового элемента, его работа).

1. Цифровые ис на n-moп структурах

С точки зрения функционального принципа работы между элементами p -типа и n -типа нет принципиальной разницы. Однако технология изготовления последних сложнее.

Параметры n-транзисторов превосходят параметры p-транзисторов по следующим причинам:

1. В транзисторах с n-каналами носители заряда – электроны, подвижность которых в два раза выше подвижности дырок

2. Транзисторы с n-каналами выполняют по технологии с самосовмещением затворов, обеспечивающей уменьшение паразитных ёмкостей в 2-3 раза; в результате быстродействие схем n-транзисторами в среднем в 5-10 раз выше.

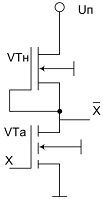

На рис. 2.13 у VTн затвор соединён с истоком, и транзистор всегда включен и проводит ток, причём в большей части диапазон изменения напряжения работает в области пологой части выходной характеристики. При высоком уровне входного сигнала в открытом (проводящем) режиме находятся оба транзистора и уровень напряжения выходного определяется соотношением сопротивлений канала нагрузочного и активного.

Рис. 2.13. Инвертор n-МОП

Специфика параметров транзисторов такова, что требования к отношению площадей каналов здесь намного ниже, чем для элементов р-МОП, и достаточно иметь отношение сопротивлений около 4. Характеристики n-МОП транзисторов позволяют использовать питание +5В.

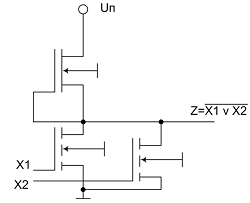

Базовым элементом является схема ИЛИ-НЕ (рис. 2.14).

Рис. 2.14. ИЛИ-НЕ n-МОП

Работа базового элемента аналогична работе инвертора за исключением того, что теперь при открытии одного из транзисторов образуется логический ноль на выходе.