- •1. Понятие интегральной схемы:

- •2. Составляющие стоимости ис и пути ее уменьшения

- •3. Типы интегральных схем по технологическому признаку:

- •4. Классификация ис по степени интеграции.

- •Типы выходов ис (с открытым коллектором, с открытым эмиттером, с тремя состояниями).

- •Базовый элемент транзисторно-транзисторной логики (принципиальная схема, работа элемента). Каким состоянием выходного каскада ис определяется нагрузочная способность элемента ис ттл?

- •1. Базовый элемент транзисторно-транзисторной логики

- •Базовый элемент ис на транзисторах Шотки (принципиальная схема, отличия от классических ттл). Почему в выходном каскаде ттл ис возникают броски тока и как с ними бороться?

- •1. Базовый элемент ис диодно-транзисторных схем на диодах и транзисторах Шотки

- •5. Подключение неиспользуемых логических элементов и входов ис ттл. Снижение нагрузок на выходах логических элементов. Подключение светодиодов.

- •2. Неиспользуемые логические элементы

- •Цифровые ис на n-moп и p-моп структурах (принципиальная схема инвертора, работа; принципиальная схема базового элемента, его работа).

- •1. Цифровые ис на n-moп структурах

- •Цифровые ис на кмоп-структурах (принципиальная схема инвертора и его работа; принципиальная схема элемента или-не и его работа). Особенности применения ис кмоп.

- •1. Цифровые ис на кмоп-стуктурах

- •Достоинства и недостатки ис кмоп. Согласование ис ттл-уровней с ис кмоп, ис кмоп с ис ттл-уровней.

- •1. Достоинства и недостатки ис кмоп

- •2. Согласование ис ттл-уровней с ис кмоп, ис кмоп с ис ттл-уровнй

- •Сумматоры групповой структуры (групповой сумматор с цепным переносом, сумматор с условным переносом, сумматор с параллельным и межгрупповым переносом).

- •1.. Сумматоры групповой структуры

- •Реализация мультиплексоров (назначение, таблица функционирования, мультиплексная формула, реализация мультиплексора 4-1 на элементах и-не).

- •Схемотехническая реализация двоичных дешифраторов (описание функционирования, обозначение на функциональной схеме, схема дешифратора 3-8 на элементах и).

- •Матричные умножители (математические выражения, схема множительно-суммирующего блока для четырехразрядных сомножителей, увеличение разрядности до 4х4 из двух 4х2).

- •Организация контроля правильности функционирования устройств обработки данных (контроль чётности, мажоритарные схемы голосования, код Хэмминга – принципиальные схемы, таблицы функционирования).

- •Асинхронный и синхронный (тактируемый) rs-триггеры (схемы на элементах и-не, или-не, таблицы функционирования и временные диаграммы, время задержки).

- •Классификация, краткое описание и таблицы функционирования триггеров.

- •Последовательные сдвигающие регистры.

- •Двоичные счетчики.

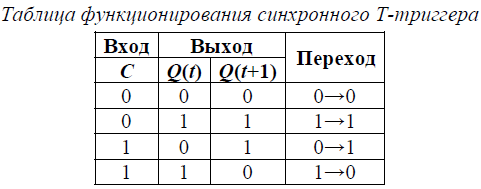

Классификация, краткое описание и таблицы функционирования триггеров.

Триггер – это устройство с двумя устойчивыми состояниями, содержащее фиксатор состояния и схему управления. На схему управления (входы) поступают сигналы (информационные, тактирующие, управляющие). Состояние триггера определяется элементом памяти. Обычно триггер имеет прямой и инверсный выходы (Q и Q соответственно).

Классифицировать триггеры можно по признаку логического функционирования и способу записи информации. По логическому функционированию различают триггеры следующих типов: RS, D, T, DV, TV, JK, комбинированные и со сложной логикой.

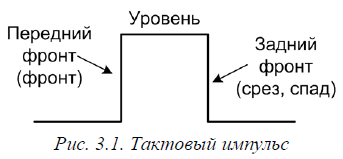

По способу записи информации триггеры можно разделить на асинхронные и синхронные (тактируемые). Тактируемые триггеры в свою очередь делятся на триггеры управляемые фронтами и уровнем (рис. 3.1). Управляемые уровнем триггеры бывают двухступенчатые и одноступенчатые.

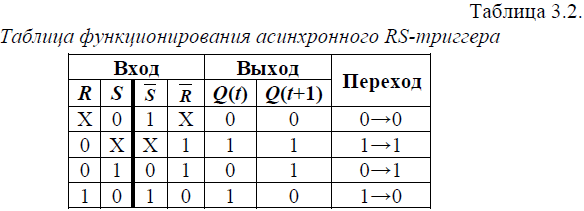

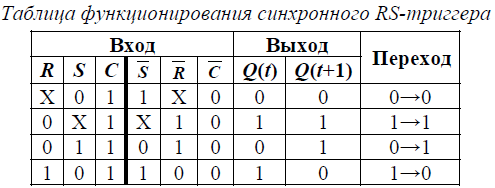

RS-триггер имеет два входа раздельной установки в нулевое и единичное состояние. Воздействие по входу S (Set) переводит триггер в единичное состояние. Воздействие по входу R (Reset) переводит триггер в нулевое состояние. Одновременная подача управляющих сигналов (воздействий) запрещена.

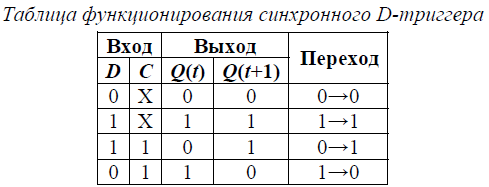

D-триггер принимает информацию по одному входу, его состояние через некоторое время повторяет выходной сигнал. Время задержки определяется тактовым сигналом. Название триггера происходит от английского слова Delay – задержка.

T-триггер называют триггер со счётным входом, который изменяет состояние на противоположное каждый раз, когда на входе триггера появляется тактовый импульс. Триггер назван первой буквой английского слова Toggle – переключать.

DV и TV триггеры отличаются от своих прототипов дополнительным входом V, который позволяет переводить триггер в режим хранения при V=0, а при V=1 работать также, как и обычные D и T триггеры соответственно.

JK-триггер универсален. Также как и в RS-триггере имеет раздельную установку единичного (Jump) и нулевого (Kill) состояний. В отличии от RS-триггера одновременная подача управляющих сигналов разрешена – она переводит триггер в счётный режим.

Последовательные сдвигающие регистры.

Регистры – последовательностное устройство, предназначенное для записи, хранения и (или) сдвига данных, представленных в виде много разрядного двоичного кода. Последовательные (сдвигающие регистры) – данные записываются в последовательном коде разряд за разрядом; тактирующие сигналы перемещают слово в разрядной сетке;

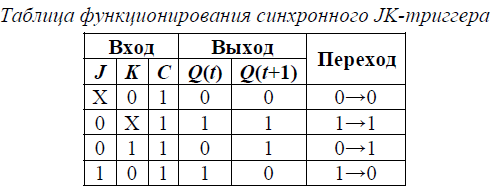

Последовательные сдвигающие регистры представляют собой цепи последовательных взаимосвязанных одноразрядных схем. В регистрах данного типа коды принимаются и выдаются разряд за разрядом. Тактирующие сигналы перемещают слово в разрядной сетке. В однотактных последовательных регистрах со сдвигом вправо (DSR – Data Serial Right) слово сдвигается на один разряд вправо при поступлении синхросигнала (рис. 4.1).

![]()

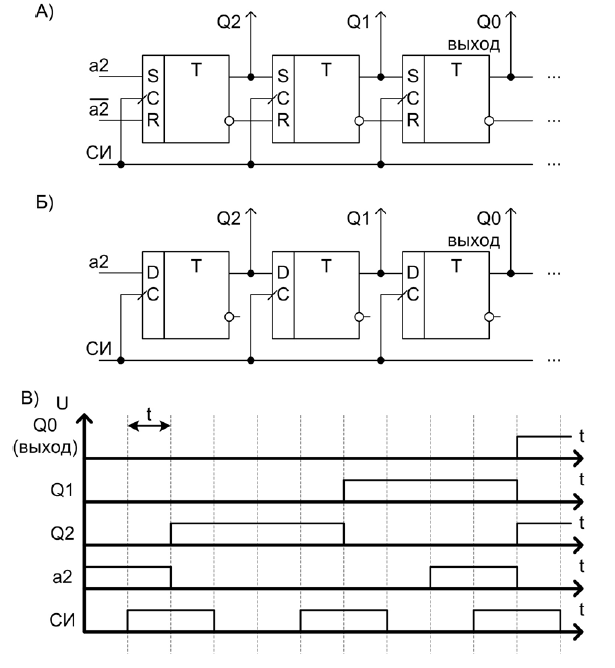

В однотактных последовательных регистрах со сдвигом влево (DSR – Data Serial Left) слово сдвигается на один разряд влево при поступлении синхросигнала (рис. 4.2).

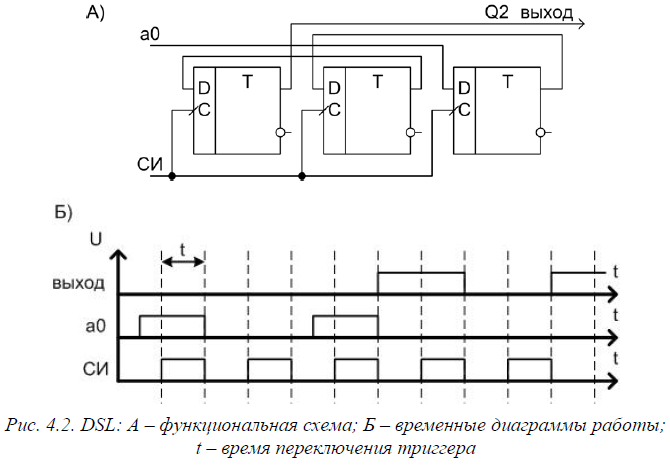

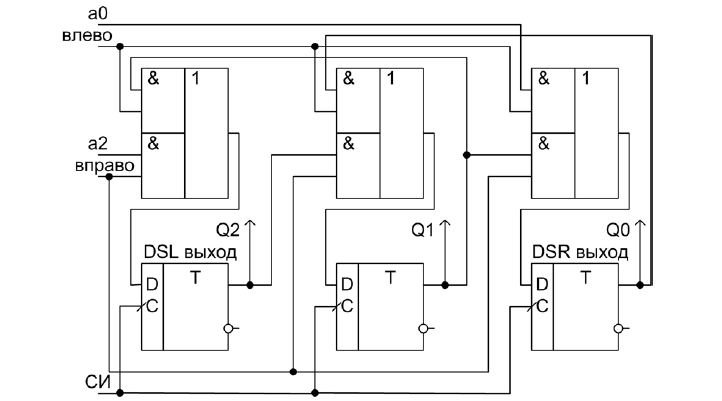

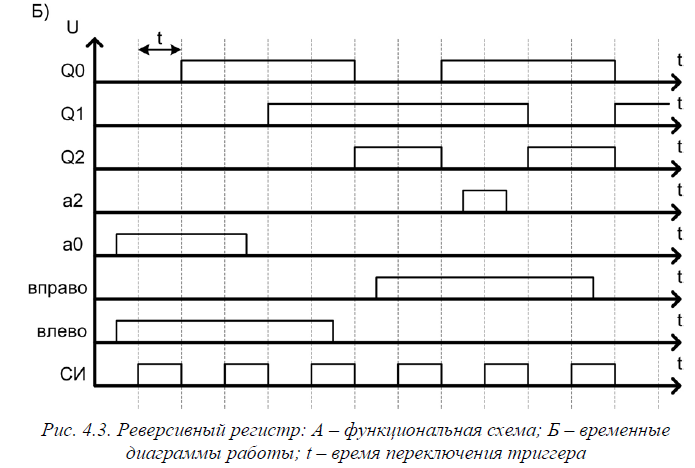

Реверсивный однотактный последовательный регистр совмещает в себе DSR и DSL. Для управления, записи и выдачи данных в разных режимах (сдвиг вправо или влево) имеются раздельные входы и выходы (рис. 4.3). Команды «влево» и «вправо» одновременно не подаются.

В сдвигающих регистрах, не имеющих логических элементов в межразрядных связях, нельзя применять одноступенчатые триггеры, управляемые уровнем, поскольку некоторые триггеры могут за время действия разрешающего уровня синхросигнала переключиться неоднократно, что недопустимо.