- •4. Эволюция элементной базы эвм: основные этапы

- •18. Архитектура и логическая структура эвм: понятие, типы архитектур

- •19, 20, 21. Классическая схема эвм и принципы Джона фон Неймана

- •22, 23, 24, 25. Эвм с магистрально – модульной архитектурой

- •31, 32, 33. Двоичная арифметика: основные сведения

- •35, 36. Представление в эвм текстовой и числовой информации

- •64,65. Процессор эвм: понятие, функции, состав, конструктивное исполнение, основные характеристики

- •70. Процессор: классы команд, структура команд

- •71, 72. Микропроцессоры: понятие, эволюция, применение, основные характеристики. Понятие о cisc и risc процессорах

- •Кремний - основа всех микропроцессоров Intel

- •Производство микропроцессоров: триста операций от старта до финиша

- •Выращивание диоксида кремния и создание проводящих областей

- •Тестирование

- •Изготовление корпуса

- •Доставка

- •73. Взаимодействие процессора и оперативной памяти

- •74. Технологические особенности современных процессоров: конвейеризация, суперскаляризация, динамическое исполнение команд

- •75. Память эвм: понятие, назначение, классификация

- •76. Типы интерфейсов периферийных устройств эвм

- •77. Динамическая память: принцип работы, организация, применение, основные типы

- •79. Статическая памяти: принцип работы, организация, применение, основные типы

- •84. Программное обеспечение эвм: понятие, назначение, состав

- •81. Операционная система: назначение, состав, примеры, этапы загрузки.

31, 32, 33. Двоичная арифметика: основные сведения

Двоичная система – позиционная. Значит, правила арифметики в ней подобны правилам десятичной арифметики. Например, при сложении для всех позиционных систем:

Числа складываются строго поразрядно, начиная с младшего.

Результат сложения конкретных знаков в разряде – величина определенная, фиксированная в таблице сложения.

При переполнении текущего разряда он обнуляется, старший увеличивается на единицу.

Таблица сложения для двоичной системы:

0+0=0

0+1=1

1+0=1

1+1=10

Вычитание:

Вычитание есть алгебраическое сложение: А-В=А+(-В)

При чем: А-А=А+(-А)=0

Для представления отрицательных двоичных чисел используется дополнительный код. Дополнительный код обозначается чертой сверху: Ā

А+ Ā=0

Понятие дополнительного кода связано с разрядной сеткой, т.е. с количеством разрядов.

Для получения дополнительного кода Ā n-разрядного двоичного числа А нужно:

Вписать число в n-разрядную сетку, прижав число к правому краю.

Инвертировать число, т.е. получить его инверсный код.

К инверсному коду прибавить единицу.

Таким образом, алгоритм вычитания следующий:

1. Вписать операнды в n-разрядную сетку, прижав их к правому краю.

2. Получить дополнительный код вычитаемого.

3. Сложить уменьшаемое и дополнительный код вычитаемого.

Умножение:

Произведение любого числа на ноль в любой системе есть 0. Произведение любого числа на единицу в любой системе есть само число. Таким образом, двоичное умножение сводится к сложению со сдвигом.

Деление:

Деление осуществляется при помощи умножения и вычитания, которые рассмотрены выше.

Вывод: двоичная арифметика сводится к сложению, инвертированию, сдвигу. Все это выполняется в CPU арифметико – логическим устройством, которое состоит из:

Регистров – схем для хранения операндов

Инверторов – схем для инвертирования

Сумматоров – схем, осуществляющих поразрядное сложение

Регистров сдвига – схем для выполнения операций сдвига.

35, 36. Представление в эвм текстовой и числовой информации

Представление любой информации в ЭВМ - это кодирование этой информации последовательностью определенных знаков (0 и 1) и реализация последовательностей знаков в ячейках памяти ЭВМ. Кодирование – процесс преобразования информации из одного вила в другой с использованием алфавита и кода. Алфавит – конечный набор знаков для представления информации. Код – правило представления информации при помощи алфавита.

Для кодирования информации для представления в ЭВМ используется двоичное кодирование – кодирование с использованием двоичного алфавита, в котором 2 знака (0 и 1). Правило кодирования (код) зависит от типа информации.

Правило кодирования текстовой информации заключается в замене каждого элемента текста (символа) комбинацией 0 и 1 в соответствии с принятой кодовой таблицей (стандартом), например UNICODE. Данный стандарт является международным, он 16- разрядный. В UNICODE можно закодировать 216=65 536 символов. 28 000 – это буквы, знаки, слоги, иероглифы национальных языков, 30 000 мест зарезервировано для пользователей. Двоичные коды (результат кодирования) представляются в ячейках памяти электрическими импульсами, раз- или намагниченными участками, участками с углублениями – в зависимости от вида памяти.

Правила двоичного кодирования числовой информации соответствуют правилам перевода чисел из десятичной в двоичную систему счисления, реализуемыми в ЭВМ. Двоичные числа ориентированы в n-разрядных сетках в соответствии с используемой формой (с фиксированной или плавающей точкой) и форматом (полуслово, слово, двойное слово). Для представления отрицательных чисел используется дополнительный код.

40 - 44 Основные элементы и цифровые схемы ЭВМ: понятие

Логические элементы

Логический элемент – электронная схема, преобразующая уровни напряжения электрического тока согласно логической функции.

Основные логические элементы и их таблицы истинности (двухвходовые):

Инвертор:

вход |

выход |

0 |

1 |

1 |

0 |

И:

Вход1 |

Вход2 |

Выход |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

И-НЕ:

Вход1 |

Вход2 |

Выход |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

ИЛИ:

Вход1 |

Вход2 |

Выход |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

ИЛИ-НЕ:

Вход1 |

Вход2 |

Выход |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

Исключающее ИЛИ:

Вход1 |

Вход2 |

Выход |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

Исключающее ИЛИ-НЕ:

Вход1 |

Вход2 |

Выход |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

39.

Логический элемент – электронная схема, преобразующая уровни напряжения электрического тока согласно логической функции.

Комбинационные схемы – схемы, состояние выходов которых однозначно определяет комбинация входных сигналов. Это, например, логические элементы, комбинационные сумматоры, дешифраторы.

Цифровые автоматы с памятью - схемы, состояние выходов которых определяет комбинация входных сигналов, а также внутреннее состояние. К таким схемам относятся, например, триггеры, регистры, счетчики.

Полный одноразрядный комбинационный сумматор – схема, выполняющая сложение двух операндов в одном разряде. Входы (их три) предназначены для приема операндов i-того разряда и переноса сигнала из предыдущего разряда. Выходы (их 2) отображают Si - разряд суммы, Pi - перенос в следующий разряд. Закон преобразования определен таблицей сложения: 0+0=0, 0+1=1, 1+0=1, 1+1=10.

N – разрядный комбинационный сумматор - схема, выполняющая сложение двух операндов в n разрядах. Представляет собой последовательность одноразрядных сумматоров.

Дешифратор- схема, преобразующая n – разрядные двоичные комбинации входных сигналов в единичный сигнал на одном из 2n выходов. Десятичный номер выхода соответствует двоичной комбинации, активизирующей данный выход.

Триггер – элемент памяти, предназначен для приема, хранения, выдачи 1 разряда двоичной информации, т.е. одного бита. Состояние триггера – это состояние его прямого выхода Q. Триггеры используются для построения регистров, счетчиков.

Двоичный регистр приема и передачи – схема, предназначенная для приема, хранения, выдачи n разрядов двоичной информации. N – разрядный регистр состоит из n триггеров, установленных на цепи, управляющие очисткой, приемом, чтением информации. Двоичная информация регистра считывается с выходов триггеров, входящих в состав регистра.

Двоичный регистр сдвига – схема, предназначенная для приема n разрядов двоичной информации и выполнения над ней операций сдвига (вправо, влево).

Двоичный счетчик – схема, предназначенная для приема импульсов, подсчета и отображения количества поступивших импульсов. N – разрядный счетчик состоит из n триггеров, соединенных последовательно, выход предыдущего – информационный вход для следующего. Количество поступивших импульсов отображается в двоичном виде на прямых выходах триггеров, входящих в состав счетчика.

50 - 56. Основные сведения о триггерах

Триггер – элемент памяти, предназначен для приема, хранения, выдачи 1 разряда двоичной информации, т.е. одного бита. Состояние триггера – это состояние его прямого выхода Q.

Триггеры широко используются во многих узлах электронной аппаратуры в виде самостоятельных изделий или в качестве базовых элементов для построения более сложных устройств (регистров, счетчиков, запоминающих устройств). Общее свойство всех триггеров – способность длительно оставаться в одном из двух устойчивых состояний, которые распознаются по значению сигналов на выходах. Один из выходов называют прямым выходом Q, другой – инверсным Q’.

Простейшие триггеры – RS-триггеры либо на элементах или-не, либо на и-не. Входы R и S играют роль информационных. Смена состояний триггера производится внешними сигналами, этот процесс называют переключением, перебросом, опрокидыванием. Информационный вход, по которому триггер устанавливается в состояние 1, называют единичным S-входом. Информационный вход, по которому триггер устанавливается в состояние 0, называют нулевым R-входом. Информационные входы есть у любого триггера.

Более сложные триггеры кроме информационных входов могут иметь тактовые (тактирующие или синхронизирующие). Сигналы на тактовых входах могут разрешить или запретить влияние на схему информационных входов. Сигналы на тактовых входах задают частоту смены информации в дискретные моменты времени и, значит, общий ритм работы узлов аппаратуры. Дискретные моменты – это время в начале (конце) временного такта. Триггеры, которые имеют только информационные входы, называют асинхронными. Триггеры, которые имеют кроме информационных входов тактирующие, называют синхронные.

По назначению различают:

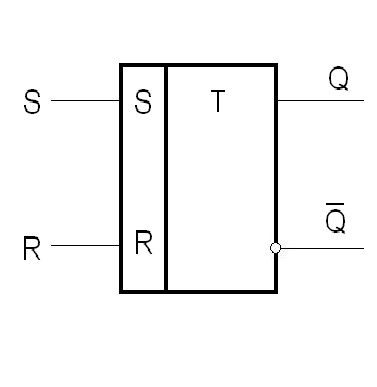

RS – триггер (простейший):

Условное обозначение |

Схема |

|

|

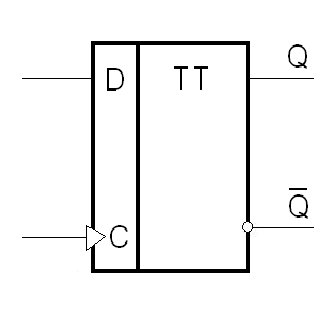

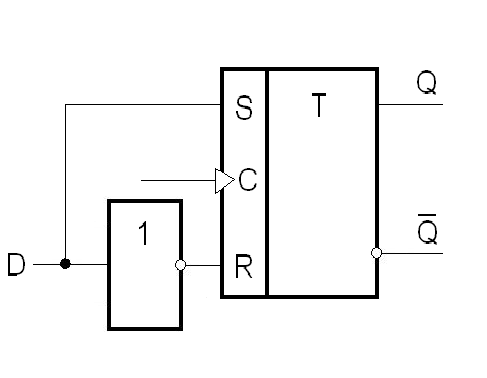

D – триггер (работает только в режиме установки):

Условное обозначение |

Схема |

|

|

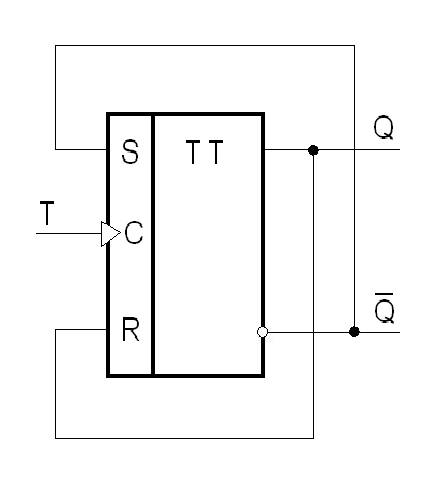

T – триггер (меняет состояние на противоположное после прохождения импульса):

Условное обозначение |

Схема |

|

|

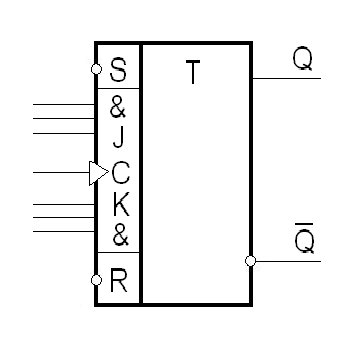

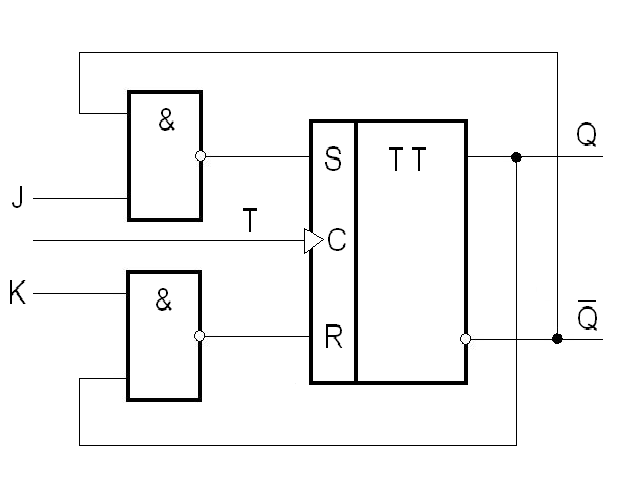

JK – триггер (универсальный):

Условное обозначение |

Схема |

|

|

Основное назначение регистров – хранение многоразрядных двоичных чисел. Наиболее простыми регистрами являются регистры памяти – регистры приема и передачи информации. Они могут хранить двоичную информацию в течении короткого промежутка времени. Двоичный регистр приема и передачи – схема, предназначенная для приема, хранения, выдачи n разрядов двоичной информации. N – разрядный регистр состоит из n триггеров, установленных на цепи, управляющие очисткой, приемом, чтением информации. Регистры имеют информационные входы – для приема разрядов. Также имеются управляющие входы: вход для обнуления, вход для разрешения записи, вход для считывания в прямом коде, вход для считывания в инверсном коде. Двоичная информация регистра считывается с выходов триггеров, входящих в состав регистра.