Аналоговый компаратор

Аналоговый компаратор сравнивает уровни на положительном выводе PE2 (AC+) и отрицательном выводе PE3 (AC-). При напряжении на положительном выводе PE2 (AC+) большем, чем напряжение на отрицательном выводе PE3 (AC-), выход аналогового компаратора ACO устанавливается в состояние 1. Выход компаратора может быть использован для управления входом захвата таймера/счетчика. Кроме того, компаратор может формировать свой запрос прерывания. Пользователь может задать формирование запроса на прерывание по нарастающему или падающему фронту или по переключению.

ACSR – регистр статуса и управления

D7 |

ADC |

Запрет аналогового компаратора (при установке в 1). Отключение позволяет снизить потребление в активном и Idle режимах |

|

D6 |

- |

Зарезервированный |

|

D5 |

ACO |

Выход аналогового компаратора |

|

D4 |

ACI |

Флаг прерывания аналогового компаратора. Устанавливается в 1 в случае формирования компаратором прерывания, определяемого ACIS1 и ACIS0 |

|

D3 |

ACIE |

Разрешение прерывания по аналоговому компаратору. Снимается с регистра статуса МК |

|

D2 |

ACIC |

Разрешение входа захвата аналогового компаратора. Разрешает срабатывание функции захвата входа таймера/счетчика1 по переключению аналогового компаратора. В этом случае выход аналогового компаратора подсоединяется непосредственно ко входной цепи логики захвата входа, что обеспечивает использование функций подавления шума и выбора вида срабатывания прерывания по захвату входа таймера/счетчика1 |

|

D1 |

ASIS1 |

Определяет прерывание аналогового компаратора |

|

D0 |

ASIS0 |

||

|

|

|

|

D1 |

D0 |

|

|

0 |

0 |

Прерывание по переключению выхода компаратора |

|

0 |

1 |

Зарезервировано |

|

1 |

0 |

Прерывание по падающему фронту на входе компаратора |

|

1 |

1 |

Прерывание по нарастающему фронту на входе компаратора |

|

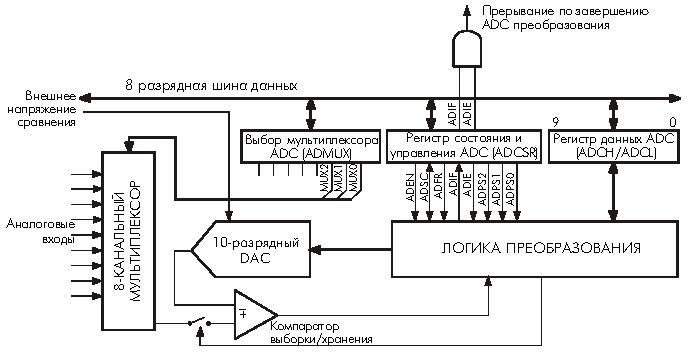

13 Аналогово-цифровой преобразователь

Для преобразования аналоговой величины, поступающей с мультиплексора, в цифровую.

Особенности:1) Разрешение 10 разрядов 2) Время преобразования 70...280 мс ~ 50-200 кГц 3) 8 мультиплексируемых каналов входа 4) Режимы циклического и однократного преобразования 5) Прерывание по завершению преобразования 6) Устройство подавления шумов Sleep режима

ADC подсоединен к 8-канальному аналоговому мультиплексору, позволяющему использовать любой вывод порта F в качестве входа ADC.

Структурная схема

Преобразование идет по методу последовательного счета

ADMUX – выбор мультиплексора

ADCSR – выбор управления и статуса

ADCH / ADCL – регистр данных

2 режима преобразования: метод однократного и циклического преобразования. В режиме однократного преобразования каждое преобразование инициируется пользователем. В режиме циклического преобразования ADC осуществляет выборку и обновление содержимого регистра данных ADC непрерывно. Выбор режима производится битом ADFR регистра ADCSR.

Регистр управления и состояния – ADCSR

D7 |

ADEN |

Разрешение преобразования ADC (0 – запрещение преобразования) |

D6 |

ADSC |

Запуск преобразования. В режиме однократного преобразования – установка в 1 для каждого цикла преобразования, в режиме циклического преобразования –достаточно установить 1 раз, при запуске первого цикла преобразования. |

D5 |

ADFR |

Установка циклического режима работы ADC |

D4 |

ADIF |

Флаг прерывания ADC. Устанавливается по завершению преобразования. |

D3 |

ADIE |

Разрешение прерывания. При установленных в состояние 1 бите ADIE и I-бите регистра SREG активируется прерывание по завершению преобразования. |

D2-D0 |

|

Выбор коэффициента предварительного деления – получение тактовой частоты. Описывается тремя разрядами |

ADP2 - ADP0 |

Получение тактовой частоты преобразователя 000 – без деления, 001 – 2, 010 – 4, 011 – 8, 100 – 16, 101 – 32, 110 – 64, 111 – 128 |

|