Курсовой - Розробка комбінаційного пристрою по заданій логічній функції / Электроника.Курсач__ПЗ

.doc

|

Аналітичний спосіб. Від табличного способу легко перейти до аналітичного способу опису логічної функції. З таблиці істинності видно, що функція Y приймає значення одиниці тільки на тих наборах, на яких не менше двох змінних мають значення одиниці. Це такі набори:

Функцію можна записати як суму добутків усіх наборів вхідних змінних, на яких вона приймає значення одиниці. При цьому змінні, які мають значення нуля, записуються з інверсією.

Таким чином, розглянута вище функція представлена сумою (диз’юнкцією) кон’юнкцій. Така форма запису функції називається диз’юнктивною нормальною формою (ДНФ). Добутки вхідних логічних функцій (кон’юнкцій) називаються мінтермами або конституєнтами одиниці. Якщо в кожен мінтерм входять усі вхідні змінні або їх інверсії, то така форма запису називається досконалою диз’юнктивною нормальною формою (ДДНФ), або першою стандартною формою запису логічної функції. Аналогічно із таблиці істинності можна виділити набори вхідних змінних, на яких функція приймає нульові значення і записати для цих наборів ДДНФ, взявши функцію з інверсією.

Інвертуючи ліву і праву частини цього рівняння і примінив аксіому подвійного інвертування та закон де Моргана, одержимо:

Вирази в дужках є сумами вхідних змінних, при яких функція дорівнює нулю. Такі суми називаються макстермами, або конституєнтами нуля. В разі, якщо в кожен макстерм входять усі вхідні змінні або їх інверсії, то така форма запису функції називається досконалою кон’юнктивною нормальною формою (ДКНФ), або другою стандартною формою запису логічної функції. В іншому разі форма запису називається кон’юнктивною нормальною формою (КНФ). Логічна функція Y є визначеною, якщо відомі її логічні значення для кожного можливого набору вхідних змінних Х1 , Х2 , ... , Хn . В разі, якщо для деяких наборів вхідних змінних функція не задана, то таку функцію називають недовизначеною або частково визначеною.

1.1.4. Побудова схем цифрових пристроїв. Функціонально повні системи логічних елементів; Після одержання аналітичного запису логічної функції можна перейти до побудови схеми цифрового пристрою, що її реалізує. Побудуємо електричну схему мажоритарного елемента “2 із 3-х” за його рівнянням у ДДНФ, яке, як було показано вище, має вигляд:

|

||||||

|

|

|

Якименко |

|

|

ПО61.006124.001 ПЗ |

Аркуш |

|

|

|

Побєдаш |

|

|

8 |

|

|

Зм. |

Арк. |

№ докум. |

Підпис |

Дата |

||

|

Для реалізації логічного пристрою знадобляться:

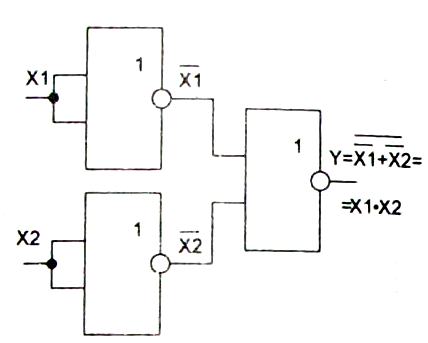

Схема розглянутого елемента зображена на рис. 1.1.1.

Рис. 1.1.1.

Набір логічних елементів, за допомогою яких можна побудувати будь-якої складності схему цифрового пристрою, називається функціонально повною системою логічних елементів або базисом. Функціональну повноту утворюють такі набори логічних елементів:

За допомогою аксіом і теорем алгебри логіки легко показати, що кожен з цих наборів є функціонально повним. Найбільш вживаними є логічні елементи І – НІ та АБО – НІ, які ще називаються універсальними. На рис. 1.1.2. показана реалізація будь – якої із трьох логічних операцій (інверсії, кон’юнкції та диз’юнкції) на універсальних логічних елементах. Прямий спосіб побудови логічних пристроїв ( ЛП ) після одержання аналітичного запису функції за звичай не є задовільним для практики, тому що використовується “надлишкова” за своєю повнотою система логічних елементів. Крім того, в разі прямого способу побудови ЛП не є оптимальним з точки зору кількості використаних для його побудови логічних елементів. Справа в тому, що одержану функцію за допомогою правил і теорем булевої алгебри можна перетворити в ряд інших, тотожних. З усіх можливих варіантів необхідно вибрати найкращий, який потребує найменшої кількості елементів для реалізації цифрового пристрою. При цьому покращуються як техніко-економічні (вартість, вага, розміри), так і технічні (наприклад, швидкодія, надійність, завадостійкість) показники розроблюваного пристрою.

|

||||||

|

|

|

Якименко |

|

|

ПО61.006124.001 ПЗ |

Аркуш |

|

|

|

Побєдаш |

|

|

9 |

|

|

Зм. |

Арк. |

№ докум. |

Підпис |

Дата |

||

|

Логічна

операція На

елементах І –

НІ На

елементах АБО –

НІ

Інверсія Кон’юнкція

Диз’юнкція

Рис. 1.1.2.

1.2. Цифрові комбінаційні пристрої. Комбінаційні схеми реалізують логічні функції ( ЛФ ), значенню котрих у даний момент часу визначаються тільки сукупністю значень вхідних змінних у цей же момент часу і не залежить від попередніх значень вхідних змінних. Цифрові комбінаційні пристрої використовуються як складові частини комп’ютерів, контролерів та інших цифрових пристроїв і на загал виконують перетворення цифрових кодів з однієї системи в іншу. Найбільш широко для обробки інформації використовуються наступні комбінаційні цифрові пристрої: мультиплексори, демультиплексори, шифратори, дешифратори, перетворювачі кодів, суматори, схеми порівняння двійкових чисел, перемножувачі та ін. Розглянемо деякі із них.

1.2.1. Мультиплексори; Мультиплексори – це комутатори логічних сигналів з декількох вхідних шин на одну вихідну. (Рис. 1.2.1. , а ). Мультиплексор має інформаційні входи – D0 , D1 , D2 , D3 ; адресні входи – A, B; дозволяючий вхід V і вихід F. Кількість адресних і інформаційних входів взаємно зв’язане. Число інформаційних входів дорівнює 2 m , де m – число адресних входів.

|

|||||||||||||||||||||

|

|

|

Якименко |

|

|

ПО61.006124.001 ПЗ |

Аркуш |

|||||||||||||||

|

|

|

Побєдаш |

|

|

10 |

||||||||||||||||

|

Зм. |

Арк. |

№ докум. |

Підпис |

Дата |

|||||||||||||||||

|

Рис. 1.2.1.

D0

M

D1

D2

D3

B

A

V

V B A F 0 0 0 D0 0 0 1 D1 0 1 0 D2 0 1 1 D3 1 * * 0

F Дозволяючий (стробуючий) вхід керує одночасно всіма інформаційними входами незалежно від адресних входів. Забороняючий сигнал на цьому вході блокує всю роботу усього пристрою. Дозволяючий вхід використовується також для нарощування розрядності мультиплексорів, а також синхронізує його роботу з роботою інших цифрових пристроїв. Двійковим кодом адресних входів А і В (В – старший розряд) задається індекс задіяного інформаційного входу, що комутується на вихід. Наприклад, двійкове число ВА=102 =210 на адресних входах забезпечує селекцію шини D2 , тобто F= D2 . Розглянемо таблицю істинності мультплексора, яка подана на рис. 1.2.1. , б. Рівняння у ДДНФ має вигляд:

Комбінаційна схема мультиплексора, відповідно до записаного рівняння, подана на рис. 1.2.2. Схема допоможе краще побачити роботу пристрою.

Рис. 1.2.2. |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

Якименко |

|

|

ПО61.006124.001 ПЗ |

Аркуш |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

Побєдаш |

|

|

11 |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Зм. |

Арк. |

№ докум. |

Підпис |

Дата |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Пояснимо роботу мультиплексора. Якщо на дозволяючий вхід подати логічну одиницю V=1 , то на одному вході кожного ЛЕ І буде присутній логічний нуль і на виході цих елементів, а також на виході елемента АБО, буде також логічний нуль (F=0). В разі, коли V=0, будь-які комбінації на адресних входах В і А створюють умови, при яких на входах трьох логічних елементів І присутні логічні нулі, а стан четвертого ЛЕ І визначається сигналом на інформаційному вході. Такий же сигнал буде на виході мультиплексора. Наприклад, війкове число 10 на адресних входах забезпечує селекцію шини D2 , тобто F=D2 . Випускаються мікросхеми мультиплексорів з 2-ма , 4-ма , 8-ма , 16-ма інформаційними входами.

1.2.2. Демультиплексори (розподільники); Інші пристрої, що у функціональному відношенні протилежні мультиплексорам називаються демультиплексорами (розподільниками). У демультиплексорах сигнали з одного інформаційного входу розподіляються у бажаній послідовності по декількох виходах. Вибір потрібної вихідної шини, як і в мультиплексорах, забезпечується кодом на адресних входах. Демультиплексор, умовне позначення якого приведене на рис. 1.2.3. , а , має Х – інформаційний вхід, В і А – адресні входи, V – дозволяючий вхід, F0, F1 , F2, F3 – виходи. В разі m входів демультиплексор може мати 2 m виходів. З таблиці істинності демультиплексора (рис. 1.2.3. , б ) одержимо рівняння функцій на його виходах:

Входи

Виходи

Х B A V F0 F1 F2 F3

Х

0

0

1

Х

0

0

0

Х

0

1

1

0

Х

0

0

Х

1

0

1

0

0

Х

0

Х

1

1

1

0

0

0

Х

*

*

*

0

0

0

0

0

а) б) Рис. 1.2.3.

Схема демультиплексора за цими рівняннями зображена на рис. 1.2.4. Демультиплексори використовують в якості розподільників інформаційних сигналів і синхроімпульсів, для організації адресної логіки в пристроях пам’яті та ін.

1.2.3. Шифратори;

Шифратори (кодери) призначені для перетворення чисел поданих у одиничній позиційній системі числення у двійкове число. В одиничній позиційній системі числення натуральне число N зображається одиницею у N-ому розряді, в той час як у решті розрядів стоять нулі. Наприклад число 4 зображується 000001000, число 9 відповідно 100000000. В таблиці істинності наведена відповідність між вхідним одиничним позиційним кодом і двійковим кодом перших десяти чисел. Кожен розряд вихідного двійкового коду залежить від усіх розрядів вхідного коду і тому є логічною (булевою) функцією змінних Х0 , Х1 , Х2 , ... , Х9, тобто: Qi = f (Х0 ,Х1 ,Х2 , ... , Х9).

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

Якименко |

|

|

ПО61.006124.001 ПЗ |

Аркуш |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

Побєдаш |

|

|

12 |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Зм. |

Арк. |

№ докум. |

Підпис |

Дата |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Рис. 1.2.4.

Виразимо розряди вихідного коду через розряди вхідного коду відповідно до таблиці істинності за допомогою операції диз’юнкції:

Відповідно до наведених логічних виразів, реалізована схема шифратора (Рис. 1.2.5. , а ). Графічне зображення шифратора наведене на рис. 1.2.5. , б.

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

Якименко |

|

|

ПО61.006124.001 ПЗ |

Аркуш |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

Побєдаш |

|

|

13 |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Зм. |

Арк. |

№ докум. |

Підпис |

Дата |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

S

S