- •1.3. Работа в лаборатории

- •1.4. Содержание отчета

- •1. Цель работы.

- •1.5 Домашнее задание

- •1.6 Контрольные вопросы

- •2. Проектирование комбинационно-логических устройств

- •2.1.Цель работы

- •2.2. Краткая теория вопроса

- •2.3. Домашнее задание

- •2.4. Работа в лаборатории

- •2.5. Методика проверки работы схемы в статическом режиме

- •2.6. Методика проверки работы схемы в динамическом режиме

- •2.7. Содержание отчета

- •1. Цель работы.

- •2.8. Контрольные вопросы

- •3. Интегральные триггеры

- •3.1. Цель работы

- •3.2. Краткое теоретическое введение

- •3.3. Домашнее задание

- •3.4. Методика экспериментального исследования

- •3.5. Работа в лаборатории

- •3.6. Содержание отчета

- •1. Цель работы.

- •3.6. Контрольные вопросы

- •4. Регистры

- •4.1. Цель работы

- •4.2. Краткая теория вопроса

- •4.3. Представление цифр в цвм

- •4.4. Методика выполнения работы

- •4.5. Исследование параллельного регистра

- •4.6. Исследование регистров сдвига

- •4.7. Исследование кольцевого регистра

- •4.8. Исследование комбинированного регистра

- •4.9. Запись чисел в 8-разрядный регистр в прямом, обратном и дополнительном кодах

- •4.10. Содержание отчета

- •1. Цель работы.

- •4.11. Контрольные вопросы

- •5. Асинхронные счетчики электрических импульсов

- •5.1. Цель работы.

- •5.2. Краткая теория вопроса.

- •5.3. Домашнее задание

- •5.4. Работа в лаборатории

- •5.5. Содержание отчета

- •1. Цель работы.

- •5.6. Контрольные вопросы

- •6. Исследование сумматоров

- •6.1. Цель работы

- •6.2. Выполнение арифметических операций в цвм

- •6.3. Одноразрядные сумматоры

- •6.4. Многоразрядные сумматоры

- •6.5. Домашнее задание

- •6.6. Работа в лаборатории

- •6.7. Содержание отчета

- •1. Цель работы.

- •6.8. Контрольные вопросы

- •7. Исследование основных комбинационных устройств мп

- •7.1. Цель работы

- •7.2. Дешифраторы

- •7.3. Шифраторы

- •7.4. Распределители сигналов

- •7.5. Мультиплексоры и демультиплексоры

- •7.6. Домашнее задание

- •7.7. Порядок выполнения работы

- •7.8. Содержание отчета

- •7.9. Контрольные вопросы

1. ИССЛЕДОВАНИЕ ЛОГИЧЕСКИХ ЭЛЕМЕНТОВ

И ПРОСТЕЙШИХ УСТРОЙСТВ НА ИХ ОСНОВЕ

1.1. Цель работы

Изучение схемотехники, экспериментальное исследование основных свойств и характеристик логических устройств на основе КМДП-ключей.

1.2. КМДП интегральные схемы

Из многочисленных серий цифровых схем на полевых транзисторах наибольшее распространение получили микросхемы на основе комплементарных (взаимно-дополняющих) полевых транзисторов со структурой металл-диэлектрик-полупроводник (КМДП-транзисторов).

Приемлемое быстродействие при малой потребляемой мощности, высокая помехоустойчивость и большое входное сопротивление, а также широкий диапазон питающих напряжений обеспечили значительное распространение КМДП интегральных схем в цифровых устройствах обработки информации.

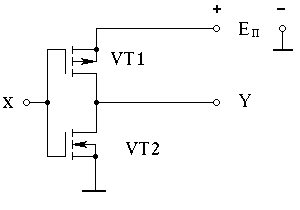

Основой КМДП-схем является транзисторный инвертор (ключ) (рис. 1.1), содержащий два МДП-транзистора с индуцированными каналами (транзистор VT1 с каналом p-типа, а транзистор VT2 с каналом n-типа).

а) б)

Рис.1.1 Структура

(а) и принципиальная схема (б) логического

элемента «НЕ»

![]() ),

напряжение затвор-исток транзистора

VT2 мало, поэтому проводящий канал n-типа

между истоком и стоком отсутствует

(транзистор VT2 закрыт). Так как VT1 открыт,

а VT2 закрыт, то выходное напряжение имеет

высокий уровень (Eп) (логическая единица).

),

напряжение затвор-исток транзистора

VT2 мало, поэтому проводящий канал n-типа

между истоком и стоком отсутствует

(транзистор VT2 закрыт). Так как VT1 открыт,

а VT2 закрыт, то выходное напряжение имеет

высокий уровень (Eп) (логическая единица).

При

подаче на вход напряжения высокого

уровня (логическая единица) напряжение

затвор-исток транзистора VT1 мало,

проводящий канал отсутствует, и транзистор

VT1 закрыт, при этом напряжение затвор-исток

транзистора VT2 велико, между стоком и

истоком образуется проводящий канал

n-типа, транзистор VT2 открыт, (

При

подаче на вход напряжения высокого

уровня (логическая единица) напряжение

затвор-исток транзистора VT1 мало,

проводящий канал отсутствует, и транзистор

VT1 закрыт, при этом напряжение затвор-исток

транзистора VT2 велико, между стоком и

истоком образуется проводящий канал

n-типа, транзистор VT2 открыт, (![]() )

поэтому выходной сигнал имеет низкий

уровень (логический нуль). Следовательно,

транзисторный ключ является инвертором

и реализует логическую операцию НЕ,

т.е.

)

поэтому выходной сигнал имеет низкий

уровень (логический нуль). Следовательно,

транзисторный ключ является инвертором

и реализует логическую операцию НЕ,

т.е.

![]() .

.

Благодаря тому, что при любом входном сигнале один из транзисторов VT1 или VT2 закрыт, потребление мощности происходит только во время переключения, когда оба транзистора находятся в активном режиме (заряд паразитных емкостей транзисторов). В статическом режиме мощность источника питания не потребляется.

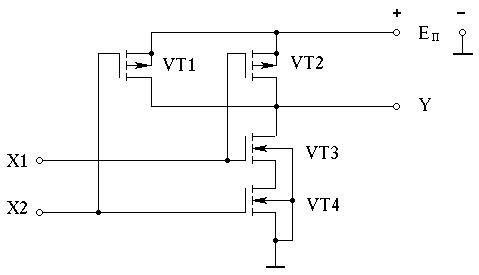

При построении цифровых микросхем на КМДП-транзисторах используются три типа логических элемента (ЛЭ), реализующих функции И-НЕ, ИЛИ-НЕ и коммутационный ключ (КК). С помощью КК реализуются выходы с третьим высокоимпедансным состоянием Z ( выходная цепь практически разомкнута).

а) б)

Рис. 1.2 Структура

(а) и принципиальная схема (б) логического

элемента 2И-НЕ

Затворы транзисторов

с различным типом проводимости попарно

соединены между собой. Входной сигнал

с уровнем логической единицы приводит

к открыванию одного из транзисторов

VT3 или VT4 (![]() или

или

![]() )

и закрыванию одного из транзисторов

VT1 или VT2 (

)

и закрыванию одного из транзисторов

VT1 или VT2 (![]() или

или

![]() ),

и наоборот, входной сигнал с уровнем

логического нуля приводит к открыванию

одного из транзисторов VT1 или VT2 и

закрыванию одного из транзисторов VT3

или VT4.

),

и наоборот, входной сигнал с уровнем

логического нуля приводит к открыванию

одного из транзисторов VT1 или VT2 и

закрыванию одного из транзисторов VT3

или VT4.

Для получения

сигнала логической единицы на выходе

ЛЭ необходимо на один из входов подать

сигнал с уровнем логического нуля, а

для получения на выходе ЛЭ уровня

логического нуля необходимо на все

входы подать сигнал с уровнем логической

единицы.Таким образом, ЛЭ реализует

логическую функцию 2И-НЕ, т.е.![]() .

.

ЛЭ, реализующий

функцию 2ИЛИ-НЕ, т.е.

![]() ,

приведен на рис. 1.3.

,

приведен на рис. 1.3.

Как видно из рис. 1.2 и 1.3, при построении ЛЭ используется следующее правило: если основные (нижние) транзисторы включены последовательно, то их динамические нагрузки (верхние транзисторы) - параллельно. Справедливо также и обратное утверждение.

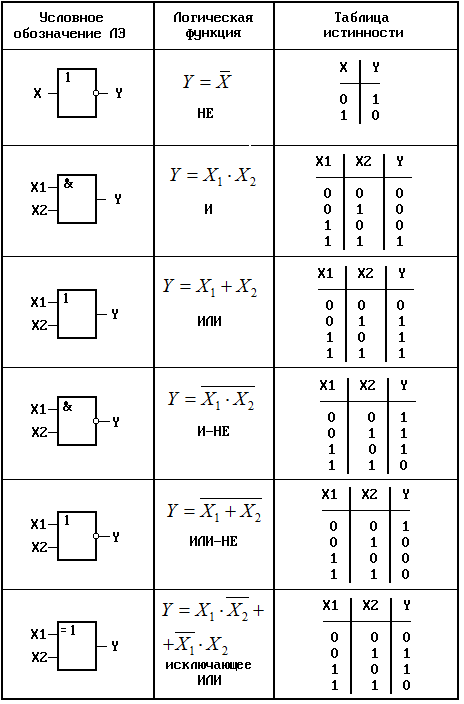

Условные обозначения основных в цифровой электронике ЛЭ и выполняемые ими функции приведены в табл. 1.1.

Таблица 1.1

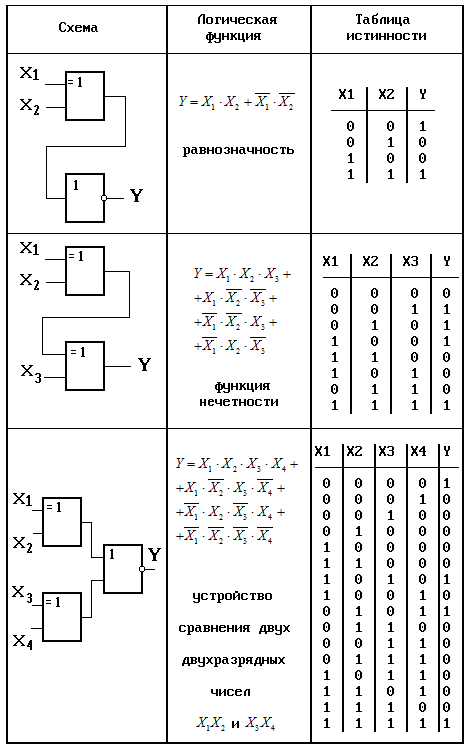

На основе логических элементов реализуются как простые логические функции, так и микропроцессорные БИС, содержащие тысячи элементов в одном полупроводниковом кристалле. Некоторые из устройств, реализующие сравнительно простые и наиболее распространенные логические функции, приведены в табл. 1.2.

Таблица 1.2

1.3. Работа в лаборатории

2. Снять передаточную характеристику ЛЭ. Для этого сначала плавным увеличением Uвх найти такое его значение Uвх, при котором Uвых начинает заметно уменьшаться. В диапазоне входных напряжений от 0 до Uвх провести 3 - 4 измерения с равномерным шагом - Uвх. Затем провести 3 - 4 измерения при таких входных напряжениях, которые соответствуют равномерному изменению Uвых от максимального до минимального значения (Uвых макс=Eп, Uвых мин=0 В). При достижении Uвых значений, близких к нулю, входное напряжение необходимо изменять с шагом Uвх до напряжения питания Eп = 5 В. Полученные результаты занести в табл. 1.3.

Таблица 1.3

Uвх, В |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Uвых, В |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3. Собрать схему опыта (рис. 1.6) и измерить частоту импульсов (f) (для измерения используется частотомер или высокочастотный осциллограф). Среднее время задержки определить по формуле

![]()

4. К схеме рис. 1.6 подключить конденсатор C на вход любого ЛЭ. Определить среднее время задержки ЛЭ tзад1 при различных значениях емкости C (C=20, 43, 82, 160, 330, 680 пФ) и данные занести в табл. 1.4.

![]() .

.

Таблица 1.4

С, пФ |

0 |

20 |

43 |

82 |

160 |

330 |

680 |

t'зад, мкс |

|

|

|

|

|

|

|

По данным табл. 1.4 построить график.

Рис. 1.6. Схема опыта для измерения среднего времени задержки tзад

5. Последовательно исследовать работу логических элементов, реализующих логические функции И, И-НЕ, ИЛИ, ИЛИ-НЕ, исключающее ИЛИ (см. табл. 1.1), подавая различные комбинации входных сигналов на входы ЛЭ.

В стенде все входы ЛЭ через резисторы, не показанные на передней панели, соединены с общей шиной, т.е. с уровнем логического нуля, и, следовательно, на свободных входах будет уровень логического нуля. Для контроля состояния выходов ЛЭ используются светодиоды. По результатам исследований составить таблицы истинности для каждого ЛЭ (см. табл. 1.1).

6. Последовательно собрать и исследовать ЛЭ “Неравнозначность” и трехразрядное устройство проверки на четность (см. табл. 1.2). Составить таблицы истинности.

7. Собрать и исследовать устройство сравнения двух двухразрядных чисел (см. табл. 1.2). Составить таблицы истинности.

При исследовании устройства сравнения первым числом является X1 X2, а вторым - Х3 X4.

8. Собрать и исследовать приведенные в табл. 1.5 схемы логических устройств, соответствующие вашему варианту. По таблицам истинности получить математические выражения, характеризующие функционирование этих схем.