- •Обобщенная структура эвм. Принцип программного управления. Параметры эвм.

- •Классификация и принципы структурной организации алу.

- •Структурная организация бо алу. Состав узлов и их связи.

- •Универсальное алу на короткие операции.

- •Проектирование алб универсального алу.

- •5. Сдвигатели.

- •6. Выполнение длинных операций в универсальном алу на короткие операции.

- •7. 7. Ау для выполнения длинных операций с фиксированной запятой. Умножение кодов

- •8. Ау для выполнения длинных операций с фиксированной запятой. Умножение чисел.

- •9. Ау для выполнения длинных операций с фиксированной запятой. Деление кодов.

- •12. Двоично-десятичный сумматор. Ау, работающие в д-кодах, на его основе.

- •13. Динамические и статические озу эвм.

- •14. Расслоение памяти.

- •16. Ассоциативное зу.

- •Универсальный запоминающий элемент ассоциативного зу.

- •20. Микропрограммые уу. Проектирование фус.

- •21. Микропрограммые уу. Проектирование фамк с принудительной адресацией.

- •22. Микропрограммые уу. Проектирование фамк с естественной адресацией.

- •23. Центральный процессорный элемент секционированного мпк.

- •24. Бис схемы управления адресом микрокоманды секционированного мпк.

- •25. Построение блока обработки данных процессора на элементах секционированного мпк.

- •26. Построение блока микропрограммного управления процессора на элементах секционированного мпк.

- •27. Организация процессора. Форматы команд. Способы адресации.

- •Режимы прямой адресации

- •Структура процессора универсальной эвм. Алгоритм выполнения двухадресной арифметической команды.

- •Двухадресные команды

- •Структура процессора универсальной эвм. Алгоритм выполнения одноадресной арифметической команды.

- •Одноадресные команды

- •Структура процессора универсальной эвм. Алгоритм выполнения посылочных команд работы со стеком.

- •Структура процессора универсальной эвм. Алгоритм выполнения команд ветвления.

- •Структура процессора универсальной эвм. Алгоритм выполнения команд работы с подпрограммами.

- •Команды работы с подпрограммами

- •33. Организация обработки прерываний в эвм

- •Цепочечная однотактная система определения приоритета запроса прерывания

- •34. Интерфейсы.

Классификация и принципы структурной организации алу.

АЛУ представляет собой технические средства, обеспечивающие выполнение арифметико-логических операций над данными. АЛУ бывают: параллельными, последовательными, параллельно-последовательными.

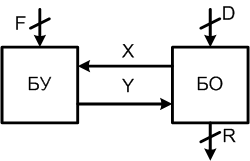

Параллельные АЛУ - выполняют обработку над всеми операндами сразу. Последовательные АЛУ - обработка операндов последовательная, бит за битом. Параллельно-последовательные - операнды обрабатываются по группам разрядов. В общем случае АЛУ может состоять из двух блоков: блок обработки(БО), блок управления(БУ). Связь с внешним миром осуществляется через входную шину D и выходную шину R. F - входная шина, задающая режим работы. Работа АЛУ реализуется программой из некоторых микроопераций. Во время работы БО характеризуется состоянием S. На основании D, S, R БО образует множество X для реализации микропрограммы, которая вырабатывается в БУ путем формирования Y.

Структурная организация бо алу. Состав узлов и их связи.

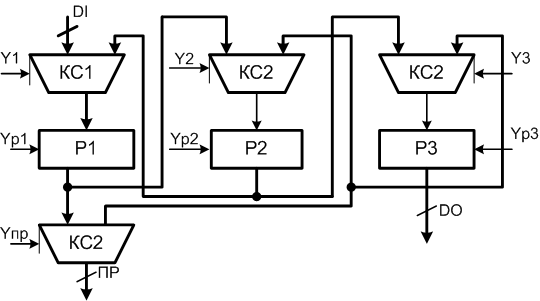

Существует два подхода в организации АЛУ: 1. Структура с непосредственными связями между операционными узлами и распределённой обработкой данных.

Присутствуют

два типа узлов: регистры (Р) и комбинационные

схемы (КС).

Присутствуют

два типа узлов: регистры (Р) и комбинационные

схемы (КС).

Достоинства:

потенциальная возможность минимизировать аппаратные затраты;

эта структура самая быстрая, потому что за один такт можно сделать несколько микроопераций в различных узлах.

Недостатки:

нерегулярность структуры;

отсутствие гибкости (схема привязана к алгоритму);

большая трудоёмкость при реализации оптимального варианта

2. Структура с магистральной организацией В общем виде эта структура заключается в следующем - происходит разделение на память и комбинационные схемы.

Достоинства:

КС можно сделать регулярной;

КС может быть универсальной

По способу организации магистрали разделяют на:

т

рехмагистральные

(рис.3.4, 3.5), где АЛБ - арифметико-логический

блок; А и В - магистрали;

рехмагистральные

(рис.3.4, 3.5), где АЛБ - арифметико-логический

блок; А и В - магистрали;

рис.3.4

рис.3.5

рис.3.4

рис.3.5двухмагистральные (рис.3.6), где F - некоторая функция от А и В.

одномагистральные (рис. 3.7).

На

рис. 3.4 (два входа, один выход) и рис.3.5 -

распределенная коммутация, также

существует сосредоточенная коммутация

(рис. 3.6), где используется мультиплексор.

рис.3.6 рис.3.7

С

целью уменьшения количества линий связи

используют:

рис.3.6 рис.3.7

С

целью уменьшения количества линий связи

используют:

двухмагистральную организацию (один вход, один выход) (рис.3.7), где БР - буферный регистр

одномагистральная организация (вход и выход объединены) (рис.3.8)

рис.3.8

рис.3.8

Универсальное алу на короткие операции.

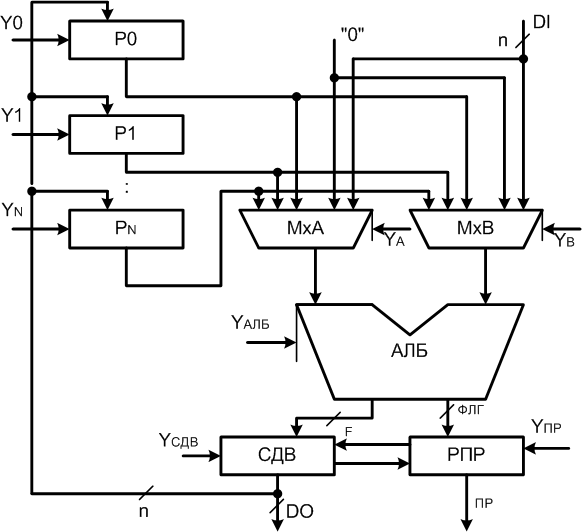

Универсальное АЛУ на "короткие" операции.

"Короткие"

операции выполняются за один такт

СДВ

- сдвигатель, пространственная передача,

сдвиги вправо, влево;

Р(0) - Р(N-1) -

регистры;

АЛБ - выполняет двухместные

и одноместные операции;

РПР - регистр

признаков, здесь хранятся флаги,

вталкиваемые и выталкиваемые разряды

сдвигателя.

СДВ

- сдвигатель, пространственная передача,

сдвиги вправо, влево;

Р(0) - Р(N-1) -

регистры;

АЛБ - выполняет двухместные

и одноместные операции;

РПР - регистр

признаков, здесь хранятся флаги,

вталкиваемые и выталкиваемые разряды

сдвигателя.