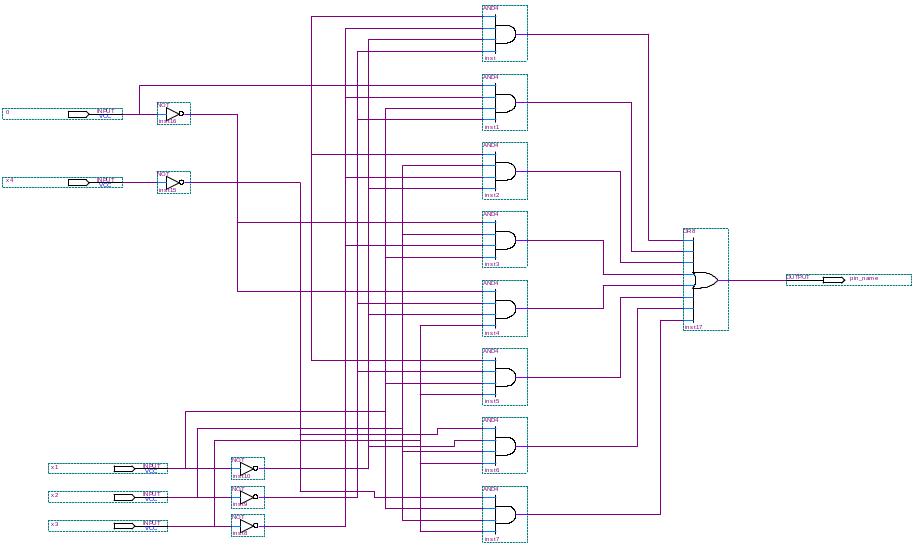

2.3 Схема 8-х канального мультиплексора

Схема, синтезированная при помощи графических примитивов.

Описание на языке VHDL.

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity Mux8pro is

port

(

InBus : in STD_LOGIC_VECTOR(7 downto 0);

Sel : in STD_LOGIC_VECTOR(2 downto 0);

OutBit : out STD_LOGIC

);

end Mux8pro;

architecture mux_impl8 of Mux8Pro is

component mux8

port

(

x1 : IN STD_LOGIC ;

x2 : IN STD_LOGIC ;

x3 : IN STD_LOGIC ;

x4 : IN STD_LOGIC

);

end component;

begin

m : mux8 port map

(

InBus(0) <= 0,

InBus(1) <= 0,

InBus(2) <= 0,

InBus(3)<= 1,

InBus(4)<= 1,

InBus(5)<= (not(x4)),

InBus(6)<= not(x4),

InBus(7)<= 0,

Sel(0)<=x1,

Sel(1)<=x2,

Sel(2)<=x3

);

process (InBus, Sel)

begin

OutBit <= InBus(TO_INTEGER (UNSIGNED(Sel)));

end process ;

end mux_impl8;

Описание на языке VHDL, создание при помощи MegaWizard Plug-In Manager

-- megafunction wizard: %LPM_MUX%

-- GENERATION: STANDARD

-- VERSION: WM1.0

-- MODULE: lpm_mux

-- ============================================================

-- File Name: mux8.vhd

-- Megafunction Name(s):

-- lpm_mux

--

-- Simulation Library Files(s):

-- lpm

-- ============================================================

-- ************************************************************

-- THIS IS A WIZARD-GENERATED FILE. DO NOT EDIT THIS FILE!

--

-- 9.1 Build 350 03/24/2010 SP 2 SJ Web Edition

-- ************************************************************

LIBRARY ieee;

USE ieee.std_logic_1164.all;

LIBRARY lpm;

USE lpm.lpm_components.all;

ENTITY mux81 IS

PORT

(

data0 : IN STD_LOGIC ;

data1 : IN STD_LOGIC ;

data2 : IN STD_LOGIC ;

data3 : IN STD_LOGIC ;

data4 : IN STD_LOGIC ;

data5 : IN STD_LOGIC ;

data6 : IN STD_LOGIC ;

data7 : IN STD_LOGIC ;

sel : IN STD_LOGIC_VECTOR (2 DOWNTO 0);

result : OUT STD_LOGIC

);

END mux81;

ARCHITECTURE SYN OF mux81 IS

-- type STD_LOGIC_2D is array (NATURAL RANGE <>, NATURAL RANGE <>) of STD_LOGIC;

SIGNAL sub_wire0 : STD_LOGIC_VECTOR (0 DOWNTO 0);

SIGNAL sub_wire1 : STD_LOGIC ;

SIGNAL sub_wire2 : STD_LOGIC ;

SIGNAL sub_wire3 : STD_LOGIC_2D (7 DOWNTO 0, 0 DOWNTO 0);

SIGNAL sub_wire4 : STD_LOGIC ;

SIGNAL sub_wire5 : STD_LOGIC ;

SIGNAL sub_wire6 : STD_LOGIC ;

SIGNAL sub_wire7 : STD_LOGIC ;

SIGNAL sub_wire8 : STD_LOGIC ;

SIGNAL sub_wire9 : STD_LOGIC ;

SIGNAL sub_wire10 : STD_LOGIC ;

BEGIN

sub_wire10 <= data0;

sub_wire9 <= data1;

sub_wire8 <= data2;

sub_wire7 <= data3;

sub_wire6 <= data4;

sub_wire5 <= data5;

sub_wire4 <= data6;

sub_wire1 <= sub_wire0(0);

result <= sub_wire1;

sub_wire2 <= data7;

sub_wire3(7, 0) <= sub_wire2;

sub_wire3(6, 0) <= sub_wire4;

sub_wire3(5, 0) <= sub_wire5;

sub_wire3(4, 0) <= sub_wire6;

sub_wire3(3, 0) <= sub_wire7;

sub_wire3(2, 0) <= sub_wire8;

sub_wire3(1, 0) <= sub_wire9;

sub_wire3(0, 0) <= sub_wire10;

lpm_mux_component : lpm_mux

GENERIC MAP (

lpm_size => 8,

lpm_type => "LPM_MUX",

lpm_width => 1,

lpm_widths => 3

)

PORT MAP (

sel => sel,

data => sub_wire3,

result => sub_wire0

);

END SYN;

-- ============================================================

-- CNX file retrieval info

-- ============================================================

-- Retrieval info: PRIVATE: INTENDED_DEVICE_FAMILY STRING "Cyclone III"

-- Retrieval info: PRIVATE: SYNTH_WRAPPER_GEN_POSTFIX STRING "1"

-- Retrieval info: CONSTANT: LPM_SIZE NUMERIC "8"

-- Retrieval info: CONSTANT: LPM_TYPE STRING "LPM_MUX"

-- Retrieval info: CONSTANT: LPM_WIDTH NUMERIC "1"

-- Retrieval info: CONSTANT: LPM_WIDTHS NUMERIC "3"

-- Retrieval info: USED_PORT: data0 0 0 0 0 INPUT NODEFVAL data0

-- Retrieval info: USED_PORT: data1 0 0 0 0 INPUT NODEFVAL data1

-- Retrieval info: USED_PORT: data2 0 0 0 0 INPUT NODEFVAL data2

-- Retrieval info: USED_PORT: data3 0 0 0 0 INPUT NODEFVAL data3

-- Retrieval info: USED_PORT: data4 0 0 0 0 INPUT NODEFVAL data4

-- Retrieval info: USED_PORT: data5 0 0 0 0 INPUT NODEFVAL data5

-- Retrieval info: USED_PORT: data6 0 0 0 0 INPUT NODEFVAL data6

-- Retrieval info: USED_PORT: data7 0 0 0 0 INPUT NODEFVAL data7

-- Retrieval info: USED_PORT: result 0 0 0 0 OUTPUT NODEFVAL result

-- Retrieval info: USED_PORT: sel 0 0 3 0 INPUT NODEFVAL sel[2..0]

-- Retrieval info: CONNECT: result 0 0 0 0 @result 0 0 1 0

-- Retrieval info: CONNECT: @data 1 7 1 0 data7 0 0 0 0

-- Retrieval info: CONNECT: @data 1 6 1 0 data6 0 0 0 0

-- Retrieval info: CONNECT: @data 1 5 1 0 data5 0 0 0 0

-- Retrieval info: CONNECT: @data 1 4 1 0 data4 0 0 0 0

-- Retrieval info: CONNECT: @data 1 3 1 0 data3 0 0 0 0

-- Retrieval info: CONNECT: @data 1 2 1 0 data2 0 0 0 0

-- Retrieval info: CONNECT: @data 1 1 1 0 data1 0 0 0 0

-- Retrieval info: CONNECT: @data 1 0 1 0 data0 0 0 0 0

-- Retrieval info: CONNECT: @sel 0 0 3 0 sel 0 0 3 0

-- Retrieval info: LIBRARY: lpm lpm.lpm_components.all

-- Retrieval info: GEN_FILE: TYPE_NORMAL mux8.vhd TRUE

-- Retrieval info: GEN_FILE: TYPE_NORMAL mux8.inc FALSE

-- Retrieval info: GEN_FILE: TYPE_NORMAL mux8.cmp TRUE

-- Retrieval info: GEN_FILE: TYPE_NORMAL mux8.bsf FALSE

-- Retrieval info: GEN_FILE: TYPE_NORMAL mux8_inst.vhd FALSE

-- Retrieval info: GEN_FILE: TYPE_NORMAL mux8_syn.v TRUE

-- Retrieval info: LIB_FILE: lpm

Результаты исследования схемы.